Design of Memory :

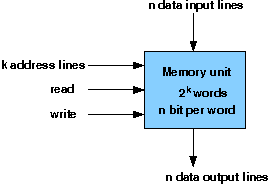

A memory unit is a collection of storage cells together with associated circuits needed to transform insformation in and out of the device. Memory cells which can be accessed for information transfer to or from any desired random location is called random access memory(RAM). The block diagram of a memory unit-

Internal Construction: The internal construction of a random-access memory of m words with n bits per word consists of m*n binary storage cells and associated decoding circuits for selecting individual words. The binary cell is the basic building block of a memory unit.

RAM Design:

Design Issues :

A basic RAM cell has been provided here as a component which can be used to design larger memory units. An IC memory consisting of 4 words each having 3 bits has been aslo provided.

Design of a RAM cell :

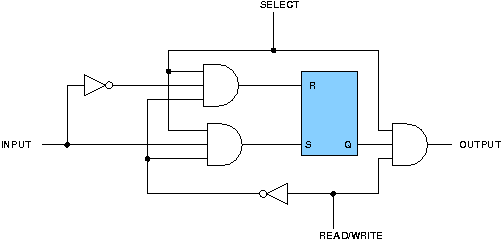

The binary cell has three inputs and one output. The select input enables the cell for reading or writing and the reda/write input determines the cell operation when it is selected. A 1 in the read/write input provides the read operation by forming a path from the flip-flop to the output terminal. A 0 in the read/write input provides the write operation by forming a path from the input terminal to the flip-flop. the logic diagram is-

Design of a 4X4 RAM :

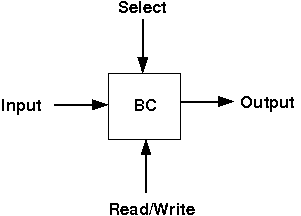

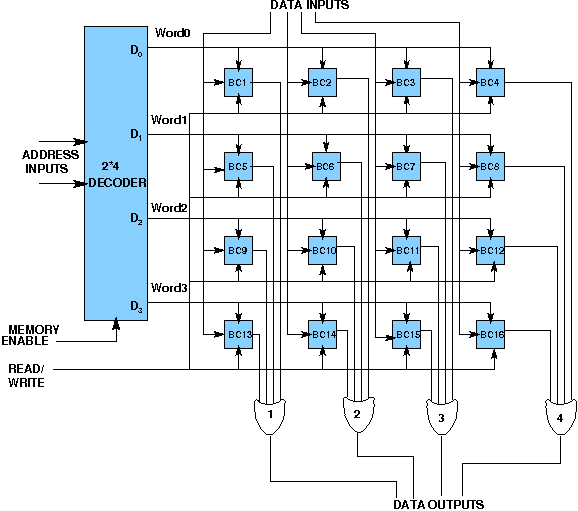

The logical construction of a small RAM 4X3 is shown below. It consists of 4 words of 3 bits each and has a total of 12 binary cells. Each block labeled BC represents the binary cell with its 3 inputs and 1 output. The block diagram of a binary cell-

A memory with 4 words needs two address lines. The two address inputs go through a 2*4 decoder to select one of the four words. The decoder is enabled with the memory enable input. When the memory enable is 0, all outputs of the decoder are 0 and none of the memory words are selected. With the memory enable at 1, one of the four words is selected, dictated by the value in the two address lines. Once a word has been selected, the read/write input determines the operation. the logic diagram is-

Design of Memory :

Basic stage

Multiple choice questions:

- What is the cycle time of a memory?

- Which of the following is electrically programmable and ultraviolet ray irasable?

- Dynamic RAM with respect to static RAM has

- Read Only Memory (ROM) is programmables and contains the bootstrap loader

- Which of the following is not a form of memory?

- Which memory is difficult to interface with processor?

Is greater than access time

Is less than access time

Same as access time

None of these

PROM

ROM

RAM

EPROM

Lower power consumption and higher bit density

Higher power consumption and lower bit density

lower power consumption and lower bit density

Higher power consumption and Higher bit density

True

False

Instruction cache

Instruction register

Instruction opcode

None of these

ROM

Static memory

Dynamic memory

None of these

Subjective questions:

- How many address bits are needed to select all memory locations in the 2118 16K × 1 RAM? `

- What is the storage element for a static RAM?

Advanced stage

Multiple choice questions:

- Dynamic RAM needs to be refreshed periodically

- Desirable characteristic(s) of a memory system is(are)

- 1M Byte memory consists of ____ RAM chips with size 256K X 1 bit

- Memory refreshing is done by

- What is the difference between PLA and ROM?

True

False

Speed and reliability

Durability and compactness

Low power consumption

All of these

10

12

24

32

CPU

Both CPU and external refresh controller

External refresh controller

None of these

PLA economises the number of minterms

PLA is combinational ROM is sequential

PLA has fixed AND array, ROM has fixed NAND array

None of these

Subjective questions:

- What is the maximum time required before a dynamic RAM must be refreshed?

- Design a 16G X 32-bit memory using 16Mb RAM chips with a word size w=8 bits.

- What is the number of address bits for addressing 256MB?

Design of Memory :

Procedure to perform the experiment:Design of 4X3 RAM memory:- Start the simulator as directed.This simulator supports 5-valued logic.

- To design the circuit we need 12 binary RAM cell, 9 OR gate, 7 bit switch (to give input,which will toggle its value with a double click), 3 bit display (to see the output), wires.

- The pin configuration of a component is shown whenever the mouse is hovered on any canned component of the palette or press the 'show pinconfig' button. Pin numbering starts from 1 and from the bottom left corner (indicated with the circle) and increases anticlockwise.

- For a binary RAM cell input is in pin-5, output is in pin-4 and select is pin-8, Read/Write is in pin-6, for read operation give 1 input to Read/Write pin. For write operation give 0 input to Read/Write pin.

- For a 'decoder with enable', input A is in pin-6, B is in pin-5, output D0 is in pin-4, D1 is in pin-3, D2 is in pin-2, D3 is in pin-1 and Enable is in pin-8

- Click on the 'decoder with enable' component (in the Other Components drawer in the pallet) and then click on the position of the editor window where you want to add the component (no drag and drop, simple click will serve the purpose), likewise add 12 binary RAM cell (from the Other Components drawer in the pallet), 9 OR gates (from Logic Gates drawer in the pallete), 7 bit switches (which will toggle its value with a double click), 3 bit displays (from Display and Input drawer of the pallet,if it is not seen scroll down in the drawer)

- To connect any two components select the Connection menu of Palette, and then click on the Source terminal and click on the target terminal. According to the circuit diagram connect all the components, connect 2 bit switches to the inputs of the 'decoder with enable' (which will act as address input), 1 bit switch to the enable pin of the 'decoder with enable' (which will act as memory enable input), connect a bit switch to the Read/Write(R/W') line, 3 bit switches to the data inputs line, 3 bit displays to the data output line and OR gates according to the diagram shown in the circuit diagram. after athe connection is over click the selection tool in the pallete.

- To see the circuit working, Do some read or write operation by properly setting the R/W', memory enable then give input and check the output. suppose you give, R/W'=1, memory enable=1, address input=01, data input=101, then it will be a read operation and you will not see 101 as output, it will store 101 in the word-1. now again set, R/W'=0, memory enable=1, address input=01, then it will be a write operation and you will see 101 as the content of word-1 on the output display.

Components :

To build a RAM Cell, we need :

- AND Gate(2 input)-6

- NOT Gate-2

- RS Flip Flop-1

To build a 4X3 RAM, we need :

- OR Gate(2 input)-11

- RAM Cell-12

- 2X4 Decoder with Enable-1

Objective of memory design(single bit RAM cell):

To design memory units and understand how it operates during read and write operation.

- understanding behaviour of memory from working module and the module designed by the student as part of the experiment

- designing an memory for given parameter

Examining behaviour of memory for the working module and module designed by the student as part of the experiment (refer to the circuit diagram):

examining the write behaviour:

- initialization (refer to experiment manual for pin numbers):

- select=1

- R/W'=0

- Loading data in the memory (refer to procedure tab for further detail and experiment manual for pin numbers):

- input(i/p)=1

examining the read behaviour:

- initialization (refer to experiment manual for pin numbers):

- select=1

- R/W'=1

- check output:

- output(o/p)=1

- it will give the value which was previously written

Recommended learning activities for the experiment: Leaning activities are designed in two stages, a basic stage and an advanced stage. Accomplishment of each stage can be self-evaluated through the given set of quiz questions consisting of multiple type and subjective type questions. In the basic stage, it is recommended to perform the experiment firstly, on the given encapsulated working module, secondly, on the module designed by the student, having gone through the theory, objective and procuder. By performing the experiment on the working module, students can only observe the input-output behavior. Where as, performing experiments on the designed module, students can do circuit analysis, error analysis in addition with the input-output behavior. It is recommended to perform the experiments following the given guideline to check behavior and test plans along with their own circuit analysis. Then students are recommended to move on to the advanced stage. The advanced stage includes the accomplishment of the given assignments which will provide deeper understanding of the topic with innovative circuit design experience. At any time, students can mature their knowledge base by further reading the references provided for the experiment.

- if value is UNKNOWN, wire color= maroon

- if value is TRUE, wire color= blue

- if value is FALSE, wire color= black

- if value is HI IMPEDENCE, wire color= green

- if value is INVALID, wire color= orange

the single bit RAM cell can be used to design large memory

- refer to the theory and circuit diagram for designing 4X3 RAM

- the behaviour can be checked as above mentioned procedure

Test plan:

- Do some read operation by properly setting the R/W', memory enable then give input and check the output.

- Do some write operation by properly setting the R/W', memory enable then give input and check the output.

- Do some read operation without setting the memory enable but properly setting the R/W' then give input and check the output.

Use Display units for checking output. Try to use minimum number of components to build. The pin configuration of the canned components are shown when mouse hovered over a component.

Assignment Statements :

- Design a binary RAM cell using a S-R flipflop, AND gates, NOT gates having select, read/write, input, output and test it by giving proper input.

- Design a 4X3 RAM memory which will have 4 words each of 3 bits using binary RAM cells, decoder with enable, OR gates and test it by giving proper input.

Design of Memory :

General guideline to use the simulator for performing the experiment:- Start the simulator as directed. For more detail please refer to the manual for using the simulator

- The simulator supports 5-valued logic

- To add the logic components to the editor or canvas (where you build the circuit) select any component and click on the position of the canvas where you want to add the component

- The pin configuration is shown when you select the component and press the 'show pinconfig' button in the left toolbar or whenever the mouse is hovered on any canned component of palette

- To connect any two components select the connection tool of palette, and then click on the source terminal and then click on the the target terminal

- To move any component select the component using the selection tool and drag the component to the desired position

- To give a toggle input to the circuit, use 'Bit Switch' which will toggle its value with a double click

- Use 'Bit Display' component to see any single bit value. 'Digital Display' will show the output in digital format

- undo/redo, delete, zoom in/zoom out, and other functionalities have been given in the top toolbar for ease of circuit building

- Use start/stop clock pulse to start or stop the clock input of the circuit. Clock period can be set from the given 'set clock' button in the left toolbar

- Use 'plot graph' button to see input-output wave forms

- Users can save their circuits with .logic extension and reuse them

- After building the circuit press the simulate button in the top toolbar to get the output

- If the circuit contains a clock pulse input, then the 'start clock' button will start the simulation of the whole circuit. Then there is no need to again press the 'simulate' button

- If you are using linux platform then click on 'Linux(32 bit)' or if you are using then click on 'Windows(32 bit)'

- Start the simulator as directed.

- To design the circuit we need 12 binary RAM cell, 9 OR gate, 7 bit switch (to give input,which will toggle its value with a double click), 3 bit display (to see the output), wires.

- The pin configuration of a component is shown whenever the mouse is hovered on any canned component of the palette. Pin numbering starts from 1 and from the bottom left corner (indicating with the circle) and increases anticlockwise.

- For a binary RAM cell input is in pin-5, output is in pin-4 and select is pin-8, Read/Write is in pin-6, for read operation give 1 input to Read/Write pin. For write operation give 0 input to Read/Write pin.

- For a 'decoder with enable', input A is in pin-6, B is in pin-5, output D0 is in pin-4, D1 is in pin-3, D2 is in pin-2, D3 is in pin-1 and Enable is in pin-8

- Click on the 'decoder with enable' component (in the Other Components drawer in the pallet) and then click on the position of the editor window where you want to add the component (no drag and drop, simple click will serve the purpose), likewise add 12 binary RAM cell (from the Other Components drawer in the pallet), 9 OR gates (from Logic Gates drawer in the pallete), 7 bit switches (which will toggle its value with a double click), 3 bit displays (from Display and Input drawer of the pallet,if it is not seen scroll down in the drawer)

- To connect any two components select the Connection menu of Palette, and then click on the Source terminal and click on the target terminal. According to the circuit diagram connect all the components, connect 2 bit switches to the inputs of the 'decoder with enable' (which will act as address input), 1 bit switch to the enable pin of the 'decoder with enable' (which will act as memory enable input), connect a bit switch to the Read/Write(R/W') line, 3 bit switches to the data inputs line, 3 bit displays to the data output line and OR gates according to the diagram shown in the circuit diagram. after athe connection is over click the selection tool in the pallete.

- To see the circuit working, Do some read or write operation by properly setting the R/W', memory enable then give input and check the output. suppose you give, R/W'=1, memory enable=1, address input=01, data input=101, then it will be a read operation and you will not see 101 as output, it will store 101 in the word-1. now again set, R/W'=0, memory enable=1, address input=01, then it will be a write operation and you will see 101 as the content of word-1 on the output display.

Click here to download the older version of simulator

Click here to download the new version of simulator

OR

Launch the older version of Simulator

Launch the new version of Simulator

Once the simulator is downloaded, open the command prompt, then go to the directory where you have saved it using cd command and then give the following command to run the simulator:

java -jar coaSimulator.jar

- Start the simulator as directed.

- To design the circuit we need 12 binary RAM cell, 9 OR gate, 7 bit switch(to give input), 3 Bit display(to see the output), wires.

- The pin configuration of a component is shown whenever the mouse is hovered on any canned component of the palette. Pin numbering starts from 1 and from the bottom left corner(indicating with the circle) and increases anticlockwise.

- For a binary RAM cell input is in pin-5, output is in pin-4 and select is pin-8, Read/Write is in pin-6, for read operation give 1 input to Read/Write pin. For write operation give 0 input to Read/Write pin.

- For a 'decoder with enable', input A is in pin-6, B is in pin-5, output D0 is in pin-4, D1 is in pin-3, D2 is in pin-2, D3 is in pin-1 and Enable is in pin-8

- Click on the 'decoder with enable' component(in the Other Components drawer in the pallet) and then click on the position of the editor window where you want to add the component(no drag and drop, simple click will serve the purpose), likewise add 12 binary RAM cell(from the Other Components drawer in the pallet), 9 OR gates(from Logic Gates drawer in the pallete), 7 bit switches(which will toggle its value with a double click), 3 bit displays(from Display and Input drawer of the pallet,if it is not seen scroll down in the drawer)

- To connect any two components select the Connection menu of Palette, and then click on the Source terminal and click on the target terminal. According to the circuit diagram connect all the components, connect 2 bit switches to the inputs of the 'decoder with enable'(which will act as address input), 1 bit switch to the enable pin of the 'decoder with enable'(which will act as memory enable input), connect a bit switch to the Read/Write(R/W') line, 3 bit switches to the data inputs line, 3 bit displays to the data output line and OR gates according to the diagram shown in the circuit diagram. after athe connection is over click the selection tool in the pallete.

- To see the circuit working, Do some read or write operation by properly setting the R/W', memory enable then give input and check the output. suppose you give, R/W'=1, memory enable=1, address input=01, data input=101, then it will be a read operation and you will not see 101 as output, it will store 101 in the word-1. now again set, R/W'=0, memory enable=1, address input=01, then it will be a write operation and you will see 101 as the content of word-1 on the output display.

Click here to download the older version of simulator

Click here to download the new version of simulator

OR

Launch the older version of Simulator

Launch the new version of Simulator

Once the simulator is downloaded, open the command prompt, then go to the directory where you have saved it using cd command and then give the following command to run the simulator:

java -jar Simulator.jar

Experiment-3 (Design of Registers and Counters) :

The web interface of the application is under development, so screenshots of the experiments are presented here.

This application is completely run under the platform independent editor frame.

As the clock input is under development, the complete simulation of registers and counters are not possible yet.

Design of Memory :

References :

Books:

- Computer Organization and Architecture - William Stallings

- Computer System Architecture - M. Morris Mano

- Computer Architecture and Organization - John P. Hayes

- Digital Logic and Computer Design - M. Morris Mano. Pearson Education - Prentice Hall.

- Digital Principles Foundation of Circuit Design and Application - Arun Kumar Singh. New Age Publishers.

- The Art of Electronics - Paul Horowitz and Winfield Hill (1989). Cambridge University Press

- Modern Dictionary of Electronics - Rudolf F. Graf (1999). Newnes

Web Sites:

Virtual Lab is an initiative of Ministry of Human Resource and Development(MHRD) under National Mission of Education through ICT to provide an interactive environment over the internet for creating and conducting different laboratory experiments by sharing the costly equipments and the resources.

For more information about the Virtual Lab,please visit http://www.vlab.co.in/

Developers of Logic Design and Computer Organization Virtual Lab

- Dr. Chittaranjan Mandal Professor, Computer Science & Engineering

- Gargi Roy Senior Project Assistant

- Devleena Ghosh

Professor, Information Technology

IIT Kharagpur

Target Audience:

Under graduate students.

Courses Aligned With:

Digital Logic and Computer organizatione.

Pre-requisite Softwares:

- 32 bit java runtime environment and java 1.6 or above

- Recommended browser: mozilla firefox, google chrome

Objectives:

The Objective is to Expose the students to the various key aspects ofLogic Design and Computer Organisation by enabling them to perform FPGA based prototyping of experiments with support of a virtual environment. The primary need for virtualisation here is multifold.

- Digital Logic and Computer Organization are core courses in most of the Undergraduate Curricula of the entire Electrical Sciences Discipline(Computer Science / Engg., Electronics, Electrical) etc.

- Many colleges/institutes cannot procure sufficient number of FPGA boards for their students.

- Even when such FPGA boards are available, making them available round the clock is difficult.

- Expert help is required to effectively use these FPGA boards and such help can be easily channeled through a virtual environment.

- Helps to standardize the set of Experiments to a large extent.

Contact Information:

Mailing Address and Contact Information:Department of Computer Science & Engineering, IIT Kharagpur

Office : +91-3222-2882255

Postal Address:

Indian Institute of Technology Kharagpur, Kharagpur - 721302, INDIA Telephone Number +91-3222-255221 | FAX : +91-3222-255303

Tutorial on UI for lab:

Introduction:

- The simulator contains a pallete on the right hand side. This pallete contains all the components and tools . Tools are used to act up on the components. Different tools:

- Selection tool- used for selecting components

- Marquee tool- used for selecting many components at a time by draggiung the mouse in the design area(editor).

- Connection tool- used for connecting components

- Components have been catagorized according to their functionality and put into different drawers in the pallete. The area under every drawer is scrallable, if you are unable to see all the components in a particular drawer just click on the area and scroll. Different drawers:

- Circuits- contains 8 and 16 terminal circuits and flow container which can hold other circuit components.

- Logic gates- contains all kinds of basic logic gates.

- Display and inputs- contains all kinds of component needed to give input to the circuit and displaying outputs of the circuit.

- Adders- contains different types of adder circuits.

- Sequential ckt- contains basic flipflops for designing sequential circuits.

- Other Components- contains different kinds of components like decoders, multiplexers, arithmetic logic units(ALU), memory elements(RAM cell) required to design combinational circuits.

- To add the components to the editor select any component(first click on the selection tool then click on the desired compoent) then finally click on the position of the editor window where you want to add the component.

- The pin configuration of a component is shown whenever the mouse is hovered on any canned component of the palette. Pin numbering starts from 1 and from the bottom left corner(indicating with the circle) and increases anticlockwise.

- To connect any two components select the Connection tool in the palette, and then click on the Source terminal and click on the target terminal(no drag and drop, simple click will serve the purpose). After the connection is over click the selection tool in the pallete.

- To move any components select the Selection Mode and drag the component after selecting it.

- If needed select any component in the editor while designing your circuit and use Undo, Redo, Delete, Zoom in, Zoom out buttons to get corresponding functionalities. Open and Save options are under development.

- As the automated clock is under development and the simulator is under modification for sequencial circuits, for the time being please use individual clock(Bit switch which toggle its value with a double click) for each flipflop.

- The simulator is currently under modification for sequential circuits, now it is working properly for combinational circuits but may not give proper output for sequential circuits.

Description of Components:

General components:- Digital display: it can be used to give input and as well as to see the output in the decimal format, its right most terminal is the LSB(least significant bit) and the left most terminal is the MSB(most significant bit), in the editor after selecting a particular digital display you can use 'Increment LED' and 'Decrement LED' buttons in the top left corner of the simulator to increment and decrement its value respectively.

- Bit display: it displays a single bit value.

- V+: it gives 1 as input.

- Ground: it gives 0 as input.

- Bit switch: it gives 1/0 input, it toggels its value with a double click.

Specific components:

Pin numbering starts from 1 and from the bottom left corner(indicating with the circle) and increases anticlockwise. Pin configurations of all the components-

- Half adder: i/p: 5,8 o/p: sum=4, carry=1

- Full adder: i/p: 5,6,8 o/p: sum=4, carry=1

- RCA 4 bit: (4 bit ripple carry adder) i/p: A0=13,A1=14,A2=15,A3=16; B0=17,B1=18,B2=19,B3=20; C0=21 o/p: S0=12,S1=11,S2=10,S3=9,Cout=8

- Wallace tree adder: (adds 3 4-bit numbers) i/p: A0=13,A1=14,A2=15,A3=16; B0=17,B1=18,B2=19,B3=20; C0=21,C1=22,C2=23,C3=24 o/p: S0=12,S1=11,S2=10,S3=9,Cout=8

- RS flipflop: i/p: R=5, S=8, Clk=7 o/p: Q=4, Q'=1

- D flipflop: i/p: D=5, Clk=8 o/p: Q=4, Q'=1

- T flipflop: i/p: T=8, Clk=7 o/p: Q=4, Q'=1

- JK flipflop: i/p: J=5, K=8, Clk=7 o/p: Q=4, Q'=1

- 2:4 Decoder: i/p: A0=5,A1=7 o/p: D0=4,D1=3,D2=2,d3=1

- 2:4 Decoder with enable: i/p: A=6,B=5, Enable=8 o/p: D0=4,D1=3,D2=2,d3=1

- 4:1 Mux: i/p: I0=9,I1=10,I2=11,I3=12,S0=13,S1=14 o/p: F=8

- Combinational Multiplier: i/p: multiplicand: A0=13,A1=14,A2=15,A3=16 Multiplier: B0=9,B1=10,B2=11,B3=12 o/p: S0=8,S1=7,S2=6,S3=5,S4=4,S5=3,S6=2,S7=1

- ALU 1 bit: i/p: A0=9, B0=10, C0=21 S0=12,S1=13 o/p: F=8, Cout=7

- 4 bit ALU: i/p: A0=13,A1=14,A2=15,A3=16; B0=17,B1=18,B2=19,B3=20; C0=21;S0=22,S1=23 o/p: F0=12,F1=11,F2=10,F3=9,Cout=8

- 16 bit ALU: i/p: A1=13,A2=15; B1=14,B2=16; Cin=9,S0=12,S1=11,S2=10 o/p: Cout=6,F2=7,F1=8

- RAM Cell: i/p=5, select=8, R/W'=6, o/p=4, R/W'=1 for read operation, R/W'=0 for write operation

- IC Memory: R/W'=16 Memory Enable=15, Address i/p=14,13 Data i/p=12,11,10 Data o/p=6,7,8 R/W'=1 for read operation, R/W'=0 for write operation

- Direct Mapped Cache:

- pin-32= S(selects whether user wants to perform cache write or cache mapping)

- pin-31= R/W'A(selects whether user wants to input the address or cache mapping)

- pin-30=A3, pin-29=A2, pin-28=A1, pin-27=A0 (thise 4 pins are used to give address input). A3 is the most significant bit and A0 is the least significant bit. A3 and A2 will be compared with the tag. A1 and A0 will select the corrsponding set.

- pin-26= R/W'D(selects whether user wants to input in the set of cache or cache mapping)

- pin-25= M1, pin-24=M0 (M1 is the most significant bit and M0 is the least significant bit). thiese two bits are used for cache writhe purpose, it selects the particular set of which user wants to give inputs to the valid bit, tag bits and data bits.

- pin-23= Den(this is an enable input which has to set for any write purpose in the cache).

- pin-21= valid bit

- pin-20= T1, pin-19=T0 (T1 is the most significant bit and T0 is the least significant bit). These are tag bits.

- pin-18= D1, pin-17=D0 (D1 is the most significant bit and D0 is the least significant bit). These are data bits.

- pin-14= Hit/Miss bit(if it gives 1 then hit otherwise miss)

- pin-15= F1, pin-16=F0 (F1 is the most significant bit and F0 is the least significant bit). These are output data bits and will be given only when there is a hit.

- Essential pin configurations for writing in cache: S=1, R/W'A=0, R/W'D=0, Den= 1

- Essential pin configurations for cache mapping: S=0, R/W'A=1, R/W'D=1, Den= 0

Testing process:

- To test your circuit give some input(through Digital display or Bit switch or V+ or Ground), if you use the Digital display or Bit switch you can then give different input to you circuit through incrementing/decrementing the Digital display or double clicking the Bit switch, the other two gives constant inputs.

- to see the output, connect Digital display or Bit display to the output terminals of your circuit.

Go to the Top

Frequently Asked Questions:

What is virtual lab?

The Virtual Laboratory is an interactive environment for creating and conducting simulated experiments: a playground for experimentation. It consists of domain dependent simulation programs, experimental units called objects that encompass data files, tools that operate on these objects.

What are the advantages of virtual lab?

Virtual Logic Design and Computer Organization lab enables students to perform FPGA based prototyping of experiments with support of a virtual environment. The primary need for virtualisation here is multifold.

- Digital Logic and Computer Organisation are core courses in most of the Undergraduate Curricula of the entire Electrical Sciences Discipline ( Computer Science / Engg., Electronics, Electrical ] etc.

- Many colleges/institutes cannot procure sufficient number of FPGA boards for their students.

- Even when such FPGA boards are available, making them available round the clock is difficult.

- Expert help is required to effectively use these FPGA boards and such help can be easily channeled through a virtual environment.

- Helps to standardize the set of Experiments to a large extent.

What is eclipse platform?

Eclipse is a Java-based, extensible open source development platform. By itself, it is simply a framework and a set of services for building a development environment from plug-in components. Eclipse comes with a standard set of plug-ins, including the Java Development Tools (JDT).

Which framework is used to develop the application?

We have used the eclipse gef framework. The Graphical Editing Framework (GEF) allows developers to take an existing application model and quickly create a rich graphical editor.

What is platform independent application?

Applications that run under particular operating systems and/or particular hardwares are called platform dependent application whereas platform independent applications can run in any operating environment.

What are the experiments which can be performed by the Virtual Logic Design and Computer Organization lab?

The experiments that will be supported by this lab are given below:

- Design of a ripple carry adder

- Design of a carry-look-ahead adder

- Design of registers and counters

- Design of a wallace tree adder

- Design of combinational multipliers

- Design of a Booth’s multiplier

- Design of an ALU

- Design of memory units

- Design of direct mapped cache

- Design of associative cache

- Design of combinational dividers

- CPU design