# **Specman Elite**<sup>™</sup>

# **Tutorial**

Version 4.0.1

#### Legal Notice

Copyright © 1999-2002 Verisity Design, Inc. All rights reserved. The contents of this document constitute valuable proprietary and confidential property of Verisity Design, Inc.

#### Trademarks

Verisity® is a trademark of Verisity Ltd or its subsidiaries (Verisity), registered in the United States and other jurisdictions. The Verisity logo, *e*VC, Invisible Specman, Lintrpt, Pure IP, Specman, Specman Elite, Specview, SureCov, SureLint, SureSight, and Verification Advisor are trademarks of Verisity Design, Inc. All other trademarks are the exclusive property of their respective owners.

#### **Confidentiality Notice**

No part of this information product may be reproduced, transmitted, or translated in any form or by any means, electronic, mechanical, manual, optical, or otherwise without prior written permission from Verisity Design, Inc.

Information in this product is subject to change without notice and does not represent a commitment on the part of Verisity. The information contained herein is the proprietary and confidential information of Verisity or its licensors, and is supplied subject to, and may be used only by Verisity's customers in accordance with, a written agreement between Verisity and its customers. Except as may be explicitly set forth in such agreement, Verisity does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy, or usefulness of the information contained in this document. Verisity does not warrant that use of such information will not infringe any third party rights, nor does Verisity assume any liability for damages or costs of any kind that may result from use of such information.

#### **Restricted Rights Legend**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraphs (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013.

#### **Destination Control Statement**

All technical data contained in this product is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

# **Table of Contents**

#### 1 Introduction

| Overview                            | . 1-1 |

|-------------------------------------|-------|

| Tutorial Goals                      | . 1-3 |

| Setting up the Tutorial Environment | .1-4  |

| Document Conventions                | .1-4  |

#### 2 Understanding the Environment

| Goals for this Chapter                   | . 2-1 |

|------------------------------------------|-------|

| What You Will Learn                      | .2-1  |

| The Design Specifications                | . 2-2 |

| The Interface Specifications             | . 2-3 |

| The Functional Test Plan                 | . 2-3 |

| Overview of the Verification Environment | . 2-5 |

#### 3 Creating the CPU Instruction Structure

| Goals for this Chapter            | 1 |

|-----------------------------------|---|

| What You Will Learn               | 1 |

| Capturing the Specifications      | 2 |

| Creating the List of Instructions | 8 |

#### 4 Generating the First Test

| Goals for this Chapter               |

|--------------------------------------|

| What You Will Learn                  |

| Defining the Test Constraints        |

| Loading the Verification Environment |

| Generating the Test                  |

#### 5 Driving and Sampling the DUT

| Goals for this Chapter | 5-1 |

|------------------------|-----|

| What You Will Learn    | 5-1 |

| Defining the Protocols | 5-2 |

| Running the Simulation | 5-5 |

#### 6 Generating Constraint-Driven Tests

| Goals for this Chapter                      | 6-1 |

|---------------------------------------------|-----|

| What You Will Learn                         | 6-1 |

| Defining Weights for Random Tests           | 6-2 |

| Generating Tests With a User-Specified Seed | 6-3 |

| Generating Tests With a Random Seed         | 6-6 |

#### 7 Defining Coverage

| Goals for this Chapter                           | 7-1 |

|--------------------------------------------------|-----|

| What You Will Learn                              | 7-1 |

| Defining Coverage for the FSM                    | 7-2 |

| Defining Coverage for the Generated Instructions | 7-4 |

| Defining Coverage for the Corner Case            | 7-5 |

#### 8 Analyzing Coverage

| Goals for this Chapter                        |

|-----------------------------------------------|

| What You Will Learn                           |

| Running Tests with Coverage Groups Defined8-2 |

| Viewing State Machine Coverage                |

| Viewing Instruction Stream Coverage           |

| Extending Coverage                            |

| Viewing Coverage Per Instance                 |

| Viewing Corner Case Coverage                  |

#### Writing a Corner Case Test 9

| Goals for this Chapter                              | 9-1 |

|-----------------------------------------------------|-----|

| What You Will Learn                                 | 9-1 |

| Increasing the Probability of Arithmetic Operations | 9-2 |

| Linking JMPC Generation to the Carry Signal         | 9-3 |

#### **10** Creating Temporal and Data Checks

| Goals for this Chapter       | 10-1 |

|------------------------------|------|

| What You Will Learn          | 10-1 |

| Creating the Temporal Checks | 10-2 |

| Creating Data Checks         | 10-4 |

| Running the Simulation       | 10-7 |

#### 11 Analyzing and Bypassing Bugs

| Goals for this Chapter  |

|-------------------------|

| What You Will Learn     |

| Displaying DUT Values   |

| Setting Breakpoints     |

| Stepping the Simulation |

| Bypassing the Bug11-8   |

| Tutorial Summary11-5    |

#### Α Setting up the Tutorial Environment

| Downloading the Required Files A        | -1 |

|-----------------------------------------|----|

| Installing the Specman Elite Software A | -3 |

| Installing the Tutorial Files A         | -4 |

#### В **Design Specifications for the CPU**

| CPU Instructions  | B-1         |

|-------------------|-------------|

| CPU Interface     | B-3         |

| CPU Register List | <b>B-</b> 4 |

# 1 Introduction

# Overview

The Specman<sup>™</sup> Elite<sup>™</sup> verification system provides benefits that result in:

- Reductions in the time and resources required for verification

- Improvements in product quality

The Specman Elite system automates verification processes, provides functional coverage analysis, and raises the level of abstraction for functional coverage analysis from the RTL to the architectural/specification level. This means that you can:

- Easily capture your design specifications to set up an accurate and appropriate verification environment

- Quickly and effectively create as many tests as you need

- Create self-checking modules that include protocols checking

- Accurately identify when your verification cycle is complete

The Specman Elite system provides three main enabling technologies that enhance your productivity:

• **Constraint-driven test generation**—You control automatic test generation by capturing constraints from the interface specifications and the functional test plan. Capturing the constraints is easy and straightforward.

- **Data and temporal checking**—You can create self-checking modules that ensure data correctness and temporal conformance. For data checking, you can use a reference model or a rule-based approach.

- **Functional coverage analysis**—You avoid creating redundant tests that waste simulation cycles, because you can measure the progress of your verification effort against a functional test plan.

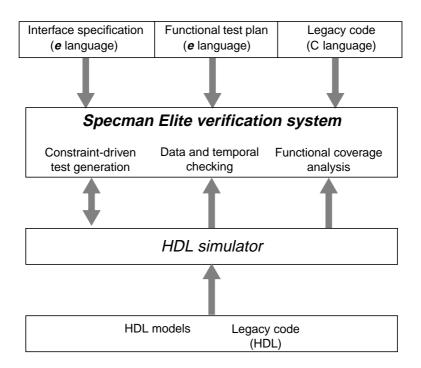

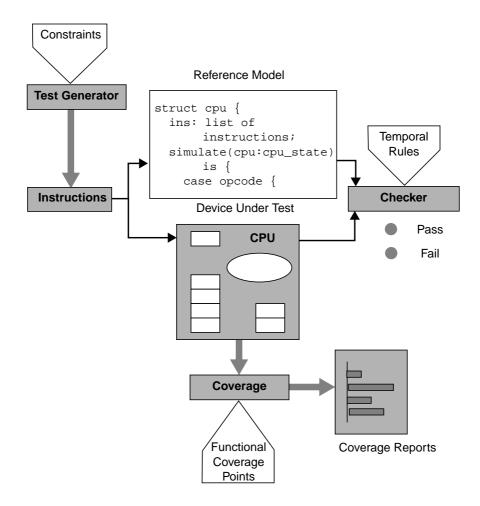

Figure 1-1 shows the main component technologies of the Specman Elite system and its interface with an HDL simulator.

#### Figure 1-1 The Specman Elite System Automates Verification

# **Tutorial Goals**

This tutorial is for use with Specman Elite version 4.0 and higher.

The goal of this tutorial is to give you first-hand experience in how the Specman Elite system effectively addresses functional verification challenges.

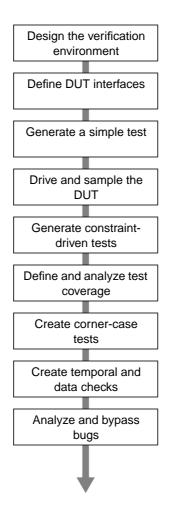

As you work through the tutorial, you follow the process described in Figure 1-2. The tutorial uses the Specman Elite system to create a verification environment for a simple CPU design.

#### Figure 1-2 Tutorial Verification Task Flow

# Setting up the Tutorial Environment

Before starting the design verification task flow shown in Figure 1-2 on page 1-3, you must set up the tutorial environment.

To set up the tutorial environment:

- 1. Download the Specman Elite software and tutorial files (see "Setting up the Tutorial Environment" on page A-1).

- 2. Install the Specman Elite software.

- 3. Install the tutorial files.

See Appendix A, "Setting up the Tutorial Environment", for detailed instructions.

**Note** Even if Specman Elite software is currently installed in your environment, you still have to download and install the tutorial files.

# **Document Conventions**

This tutorial uses the document conventions described in Table 1-1.

| Visual Cue   | Meaning                                                                                                                                                        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| courier      | Specman Elite or HDL code. For example,                                                                                                                        |

|              | keep opcode in [ADD, ADDI];                                                                                                                                    |

| courier bold | Text that you need to type exactly as it appears to complete a procedure or modify a file.                                                                     |

| bold         | In text, bold indicates Specman Elite keywords. For example, in the phrase "the <b>verilog trace</b> statement," <b>verilog</b> and <b>trace</b> are keywords. |

| %            | In examples that show commands being entered, the % symbol indicates the UNIX prompt.                                                                          |

| SN>          | In examples that show commands being entered in the Specman Elite system, SN> indicates the Specman Elite prompt.                                              |

#### Table 1-1 Document Conventions

# 2 Understanding the Environment

# **Goals for this Chapter**

This tutorial uses a simple CPU design to illustrate the benefits of using the Specman Elite system for functional verification. This chapter introduces the overall verification environment for the tutorial CPU design, based on the design specifications, interface specifications, and the functional test plan.

# What You Will Learn

Part of the productivity gain provided by the Specman Elite system derives from the ease with which you can capture the specifications and functional test plan in executable form. In this chapter, you become familiar with the design specifications, the interface specifications, and the functional test plan for the CPU design. You also become familiar with the overall CPU verification environment.

The following sections provide brief descriptions of the:

- Design specifications

- Interface specifications

- Functional test plan

- Overall verification environment

For more detailed information on the CPU instructions, the CPU interface, and the CPU's internal registers, see Appendix B, "Design Specifications for the CPU".

# The Design Specifications

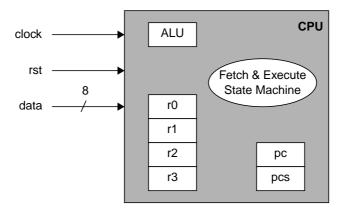

The device under test (DUT) is an 8-bit CPU with a reduced instruction set (Figure 2-1).

#### Figure 2-1 CPU Block-Level Diagram

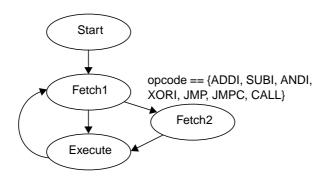

The state machine diagram for the CPU is shown in Figure 2-2. The second fetch cycle is only for *immediate* instructions and for instructions that control execution flow.

#### Figure 2-2 CPU State Machine Diagram

There is a 1-bit signal associated with each state, *exec*, *fetch2*, *fetch1*, *start*. If no reset occurs, the *fetch1* signal must be asserted exactly one cycle after entering the execute state.

# The Interface Specifications

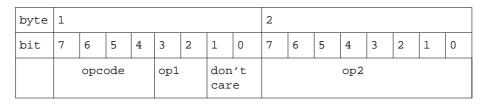

All instructions have a 4-bit opcode and two operands. The first operand is one of four 4-bit registers internal to the CPU. The second operand is determined by the type of instruction:

• **Register instructions**—The second operand is another one of the four internal registers.

#### Figure 2-3 Register Instruction

| byte | 1      |   |   |     |   |     |   |   |

|------|--------|---|---|-----|---|-----|---|---|

| bit  | 7      | 6 | 5 | 4   | 3 | 2   | 1 | 0 |

|      | opcode |   | ( | op1 | C | op2 |   |   |

• **Immediate instructions**—The second operand is an 8-bit value. When the opcode is of type JMP, JMPC, or CALL, this operand must be a 4-bit memory location.

#### Figure 2-4 Immediate Instruction

### **The Functional Test Plan**

We need to create a series of tests that will result in adequate test coverage for most aspects of the design, including some rare corner cases. There will be three tests in this series.

### Test 1

#### **Test Objective**

A simple go-no-go test to confirm that the verification environment is working properly.

#### **Test Specifications**

- Generate five instructions.

- Use either the ADD or ADDI opcode.

- Set op1 to REG0.

- Set op2 either to REG1 for a register instruction or to value 0x5 for an immediate instruction.

### Test 2

#### **Test Objective**

Multiple random variations on a test to gain high percentage coverage on commonly executed instructions.

#### **Test Specifications**

- Use constraints to direct random testing towards the more common arithmetic and logic operations rather than the control flow operations.

- Run the test 15 times, each time with a different random seed.

# Test 3

#### **Test Objective**

Generation of a corner case test scenario that exercises JMPC opcode when carry bit is asserted. Note that it is difficult to efficiently cover this scenario by purely random or purely directed tests.

#### **Test Specifications**

- Generate many arithmetic opcodes to increase the chances of carry bit assertion.

- Monitor the DUT and use on-the-fly generation to generate many JMPC opcodes when the carry signal is high.

# **Overview of the Verification Environment**

The overall test strategy, shown in Figure 2-5, is to:

- Constrain the Specman Elite test generator to create valid CPU instructions.

- Compare the program counters in the CPU to those in a reference model.

- Define temporal rules to check the DUT behavior.

- Define coverage points for state machine transitions and instructions.

Figure 2-5 Design Verification Environment Block-Level Diagram

Because the focus of this tutorial is the Specman Elite system, we do not include an HDL simulator. Rather than instantiating an HDL DUT, we model the DUT in e and simulate it in Specman Elite. The process you use to drive and sample the DUT in e is exactly the same as a DUT in HDL.

Now you are ready to create the first piece of the verification environment, the CPU instruction stream.

# 3 Creating the CPU Instruction Structure

# **Goals for this Chapter**

The first task in the verification process is to set up the verification environment. In this chapter you start creating the environment by defining the inputs to the design, the CPU instructions.

# What You Will Learn

In this chapter you learn how to create a data structure and define specification constraints that enable the Specman Elite system to generate a legal instruction stream. By the end of this chapter, you will have created the core structure for the CPU instructions. This core structure will be used and extended in subsequent chapters to create the tests.

As you work through this chapter, you gain experience with one of the Specman Elite system's enabling features—easy specification capture. Using a few constructs from the e language, you define the legal CPU instructions exactly as they are described in the interface specifications.

This chapter introduces the *e* constructs shown in Table 3-1.

| Construct | How the Construct is Head                                                                        |

|-----------|--------------------------------------------------------------------------------------------------|

| Construct | How the Construct is Used                                                                        |

| <''>      | Marks the beginning and end of <i>e</i> code.                                                    |

| struct    | Creates a data structure to hold the CPU instructions.                                           |

| extend    | Adds the data structure for the CPU instructions to the Specman Elite system of data structures. |

| list of   | Creates an array or list without having to keep track of pointers or allocate memory.            |

| type      | Defines an enumerated data type for the CPU instructions.                                        |

| bits      | Defines the width of an enumerated type.                                                         |

| keep      | Specifies rules or constraints for the instruction fields.                                       |

| when      | Implements conditional constraints on the possible values of the instruction fields.             |

#### Table 3-1 New Constructs Used in this Chapter

To create the CPU instruction structure, you must:

- Capture the interface specifications

- Create a list of instructions

The following sections explain how to perform these tasks.

# **Capturing the Specifications**

In this task, you create the data structure for the instruction stream and constrain the test generator to generate only legal CPU instructions. Individual tests that you create later can constrain the generator even further to test some particular functionality of the CPU.

For a complete description of the legal CPU instructions, refer to Appendix B, "Design Specifications for the CPU".

#### Procedure

To capture the design specifications in *e*:

- 1. Make a new working directory and copy the *src/CPU\_instr.e* file to the working directory.

- 2. Open the *CPU\_instr.e* file in an editor.

The first part of the file has a summary of the design specifications for the CPU instructions.

```

CPU_instr.e: Basic structure of CPU instructions

This module defines the basic structure of CPU instructions,

according to the design and interface specifications.

*

All instructions are defined as:

Opcode Operand1 Operand2

*

There are 2 types of instructions:

Register Instruction:

bit | 7654 | 32 | 10 |

| opcode | op1 | op2 |

(req)

Immediate Instruction:

byte | 1

2

bit | 7654 | 32 | 10 | 76543210 |

opcode | op1 | don't | op2

care

* Register instructions are:

ADD, SUB, AND, XOR, RET, NOP

* Immediate instructions are:

ADDI, SUBI, ANDI, XORI, JMP, JMPC, CALL

* Registers are REG0, REG1, REG2, REG3

```

3. Find the portion of the file that starts with the <' e code delineator and review the constructs:

| defines the legal<br>opcodes as an<br>enumerated type | <'<br>type cpu_opcode: [ // Opcodes<br>ADD, ADDI, SUB, SUBI,<br>AND, ANDI, XOR, XORI,<br>JMP, JMPC, CALL, RET,<br>NOP<br>] (bits: 4); |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| defines the<br>internal registers                     | <pre>type reg: [ // Register names<br/>REG0, REG1, REG2, REG3<br/>] (bits:2);</pre>                                                   |

| when complete,                                        | struct instr {                                                                                                                        |

| this structure<br>defines a valid                     | // defines 2nd op of reg instruction                                                                                                  |

| CPU instruction                                       | // defines 2nd op of imm instruction                                                                                                  |

| // indicates that                                     | <pre>// defines legal opcodes for reg instr</pre>                                                                                     |

| rest of line is a<br>comment                          | // defines legal opcodes for imm instr                                                                                                |

|                                                       | // ensures 4-bit addressing scheme                                                                                                    |

|                                                       | };                                                                                                                                    |

| when complete,<br>this construct                      | extend sys {                                                                                                                          |

| adds the CPU<br>instruction set to                    | <pre>// creates the stream of instructions</pre>                                                                                      |

| the Specman Elite<br>system                           | };<br>'>                                                                                                                              |

4. Define two fields in the *instr* structure, one to hold the opcode and one to hold the first operand.

Use the enumerated types, *cpu\_opcode* and *reg*, to define the types of these fields. To indicate that the Specman Elite system must drive the values generated for these fields into the DUT, place a % character in front of the field name. You will see how this % character facilitates packing automation in Chapter 5, "Driving and Sampling the DUT".

The structure definition should now look like this:

5. Define a field for the second operand.

The second operand is either a 2-bit register or an 8-bit memory location, depending on the kind of instruction, so you need to define a single field (*kind*) that specifies the two kinds of instructions. Because the generated values for *kind* are not driven into the design, do not put a % in front of the field name.

| add this line to<br>define the field<br>'kind' and define | strı | act instr {<br>%opcode<br>%op1<br><b>kind</b> | :cpu_op<br>:reg;<br>:[imm, | -      |             |

|-----------------------------------------------------------|------|-----------------------------------------------|----------------------------|--------|-------------|

| an enumerated<br>type at the<br>same time                 | };   | // defines                                    | 2nd op                     | of reg | instruction |

6. Define the conditions under which the second operand is a register and those under which it is a byte of data.

You can use the **when** construct to do this.

7. Constrain the opcodes for immediate instructions and register instructions to the proper values.

Whenever the opcode is one of the register opcodes, then the *kind* field must be *reg*. Whenever the opcode is one of the immediate opcodes, then the *kind* field must be *imm*. You can use the **keep** construct with the implication operator => to easily create these complex constraints.

```

struct instr {

.

.

.

// defines legal opcodes for reg instr

keep opcode in [ADD, SUB, AND, XOR, RET, NOP]

=> kind == reg;

// defines legal opcodes for imm instr

keep opcode in [ADDI, SUBI, ANDI, XORI, JMP, JMPC, CALL]

=> kind == imm;

// ensures 4-bit addressing scheme

};

```

8. Constrain the second operand to a valid memory location (less than 16) when the instruction is immediate.

You can use the **when** construct together with **keep** and => to create this constraint.

9. Save the *CPU\_instr.e* file.

Now you have finished defining a legal CPU instruction.

# **Creating the List of Instructions**

In this task, you create a CPU instruction structure by extending the Specman Elite system (**sys**) to include a list of CPU instructions. **sys** is a built-in Specman Elite structure that defines a generic verification environment.

### Procedure

To create the list of instructions:

1. Within the same *CPU\_instr.e* file, find the lines of code that extend the Specman Elite system:

```

extend sys {

// creates a stream of instructions

};

```

2. Create a field for the instruction data of type *instr*.

When defining a field that is an array or a list, you must precede the field type with the keyword **list of**.

```

extend sys {

// creates a stream of instructions

!instrs: list of instr;

};

```

The exclamation point preceding the field name *instrs* tells the Specman Elite system to create an empty data structure to hold the instructions. Then, each test tells the system when to generate values for the list, either before simulation (pre-run generation) or during simulation (on-the-fly generation). In this tutorial you use both types of generation.

3. Save the *CPU\_instr.e* file.

Now you have created the core definition of the CPU instructions. You are ready to extend this definition to create the first test.

# 4 Generating the First Test

# **Goals for this Chapter**

In this chapter, you will generate the first test described in "The Functional Test Plan" on page 2-3. This first test is a simple test to confirm that the verification environment is set up correctly and that you can generate valid instructions for the CPU model.

# What You Will Learn

In this chapter, you learn how to create different types of tests easily by specifying test constraints in the Specman Elite system. Test constraints direct the Specman Elite generator to a specific test described in the functional test plan. This chapter illustrates how the Specman Elite system can quickly generate an instruction stream. In the next chapter, you will learn how to drive this instruction stream to verify the DUT.

As you work through this chapter to create the first test, you gain experience with the following enabling features of the Specman Elite system:

- **Extensibility**—This enables adding definitions, constraints, and methods to a struct in order to change or extend its original behavior without altering the original definition.

- **Constraint solver**—This is the core technology that intelligently resolves all specification constraints and test constraints and then generates the desired test.

This chapter shows new uses of the e constructs introduced in Chapter 3, "Creating the CPU Instruction Structure". It also introduces the Specview menu commands shown in Table 4-1.

| Construct              | How the Construct is Used                                                                                                   |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| extend                 | Adds constraints to the <b>sys</b> and <i>instr</i> structs defined in Chapter 3, "Creating the CPU Instruction Structure". |

| keep                   | Limits the possible values of the instruction fields and the number<br>of instructions generated for this test.             |

| when                   | Defines conditional constraints.                                                                                            |

| Command                | How the Command is Used                                                                                                     |

| File>>Load             | Loads uncompiled <i>e</i> modules into the Specman Elite system.                                                            |

| File>>Modules          | Lists the <i>e</i> modules you have loaded into the Specman Elite system.                                                   |

| Test>>Test             | Generates a test based on the constraints you specify.                                                                      |

| Tools>>Data<br>Browser | Opens the Data Browser GUI, in which you view the hierarchy of generated objects and their values.                          |

| Table 4-1 | New Constructs and Specview Menu Commands Used in this |

|-----------|--------------------------------------------------------|

| Chapter   |                                                        |

**Tip** In most cases, the Specview menu commands presented in this tutorial can be issued by clicking a button. For example, clicking the Load button in the Specview main window is the same as choosing Load from the File menu. Similarly, you can click the Modules button instead of choosing Modules from the File menu or click Test instead of choosing Test from the Test menu.

The steps required to generate the first test for the CPU model are:

- 1. Defining the test constraints.

- 2. Loading the verification environment into the Specman Elite system.

- 3. Generating the test.

The following sections explain how to perform these steps.

# **Defining the Test Constraints**

The Functional Test Plan for the CPU design (see "The Functional Test Plan" on page 2-3) describes the objectives and specifications for this first test.

# **Test Objective**

The objective is to confirm that the verification environment is working properly.

# **Test Specifications**

To meet the test objective, the test should:

- Generate five instructions.

- Use either the ADD or ADDI opcode.

- Set op1 to REG0.

- Set op2 either to REG1 for a register instruction or to value 0x5 for an immediate instruction.

### Procedure

To capture the test constraints in *e*:

1. Copy the *src/CPU\_tst1.e* to the working directory and open the *CPU\_tst1.e* file in an editor.

2. Find the portion of the file that looks like this:

```

<'

import CPU_top;

extend instr {

// test constraints

};

extend sys {

// generate 5 instructions

};

.

.</pre>

```

3. Add lines below the comments as follows to constrain the opcode, operands, and number of instructions:

```

< '

extend instr {

//test constraints

keep opcode in [ADD, ADDI];

constrains the

keep op1 == REG0;

opcode and

when reg instr { keep op2 == REG1; };

operands

when imm instr { keep op2 == 0x5; };

};

extend sys {

//generate 5 instructions

constrains the

keep instrs.size() == 5;

number of

};

instructions

```

4. Save the *CPU\_tst1.e* file.

# Loading the Verification Environment

To run the first test, you need the following files:

- **CPU\_tst1.e**—imports (includes) *CPU\_top.e* and contains the test constraints for the first test.

- **CPU\_top.e**—imports *CPU\_instr.e* and *CPU\_misc.e*.

- **CPU\_instr.e**—contains the definitions and specification constraints for CPU instructions.

- CPU\_misc.e—configures settings for print and coverage display.

These files are called modules in the Specman Elite system. Before the system can generate the test, you must load all the modules.

### Procedure

To load all modules:

- 1. Copy the *src/CPU\_top.e* file to the working directory.

- 2. Copy the *src/CPU\_misc.e* file to the working directory.

The working directory should now contain four files: *CPU\_instr.e*, *CPU\_misc.e*, *CPU\_top.e*, and *CPU\_tst1.e*

3. From the working directory, type the following command at the UNIX prompt to invoke Specman Elite's graphical user interface, Specview<sup>™</sup>:

% specview &

**Tip** If the Specview main window (Figure 4-1) does not appear, make sure that you have defined the Specman Elite environment variables correctly. You can source the *install\_dir/release\_number/env.csh* file to set these variables.

#### Figure 4-1 Specview Main Window

| -                                                               | Specman Elite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | · 🗆                       |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew <u>T</u> est <u>D</u> eb | ug <u>T</u> ools <u>U</u> ser <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Support Vadvisor Verisity |

| Interrupt                                                       | n and a start and a start a st |                           |

| Welcome to Specman Elite<br>Checking license OK                 | (4.0c2.0) - Linked on Thu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Dec 27 17:01:01 2001      |

4. Choose Load from the File menu or click the Load button.

The Select A File dialog box appears.

5. In the Select A File dialog box, double-click CPU\_tst1.e in the list of files.

Specview automatically loads all four files contained in your working directory. In the Specview main window, you should see a message that looks as follows:

```

Loading CPU_instr.e (imported by CPU_top.e) ...

Loading CPU_misc.e (imported by CPU_top.e) ...

Loading CPU_top.e (imported by CPU_tstl.e) ...

Loading /tutorial/CPU_tstl.e ...

```

- **Tip** If the *CPU\_tst1.e* file name does not appear in the dialog box, you probably did not invoke Specview from the working directory. Use the list of directories in the dialog box to navigate to the working directory.

- Tip If the CPU\_tst1.e file does not load completely because of a syntax error, use the UNIX diff utility to compare your version of CPU\_tst1.e to tutorial/gold/CPU\_tst1.e. Fix the error and click the Reload button. Alternatively, you can click the blue hypertext link in the Specview main window, and the error location will be displayed in the Debugger window.

To see a list of loaded modules, choose Modules from the File menu or click the Modules button.

There should be four modules loaded:

```

CPU_instr

CPU_misc

CPU_top

CPU_tst1

```

### **Generating the Test**

To generate the test:

1. In the Specview main window, click the Test button.

You should see the following output in the Specview main window.

| -                                                                                                                                                                                                                                                                       | Spe                                                                                        | ecman Elite                           |         |                 |          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------|---------|-----------------|----------|

| <u>File E</u> dit <u>V</u> iew <u>T</u> est                                                                                                                                                                                                                             | Debug Tools User                                                                           | <u>H</u> elp                          | 1       | support advisor | Verisity |

| X<br>Interrupt Load Relo                                                                                                                                                                                                                                                | ad Restore Modules                                                                         | Test Sys Cov                          |         | Config Thread   | łs       |

| Loading CPU_instr.e<br>Loading CPU_misc.e<br>Loading CPU_top.e<br>Loading CPU_tst1.e<br>Loading CPU_tst1.e<br>Doing setup<br>Generating the test .<br>Running the test .<br>No actual running ro<br>Checking the test .<br>Checking is complete<br>Wrote 1 cover_struct | (imported by CPU<br>(imported by CPU<br><br>using seed 1<br>equested.<br>= - 0 DUT errors, | J_top.e)<br>tst1.e)<br>0 DUT warnings |         |                 |          |

| Specman >                                                                                                                                                                                                                                                               |                                                                                            |                                       |         |                 | ¥        |

| CPU_tst1                                                                                                                                                                                                                                                                |                                                                                            | Normal                                | Ready 🗆 |                 |          |

2. In the Tools menu, choose Data Browser, and then choose Show Data Sys.

The Data Browser GUI appears.

|                                         | Data Browser – sys                             |                   | L                    |

|-----------------------------------------|------------------------------------------------|-------------------|----------------------|

| File View Tools                         |                                                |                   |                      |

| Prev Next New Window Source Edit Modify | Config                                         |                   | G 💭<br>Lock Close    |

| Expression: Sys                         | 🔋 sys: sys (like any_unit) = sys-@             | 0                 |                      |

| Data Content                            | Data Details                                   |                   |                      |

| Bright Sys = sys-@0<br>                 | 📮 Fields 🖌 Events 🚺 Methods 🕒 Listit           | ana               |                      |

|                                         | 🖾 💡 况 🛛 Name                                   | Value             | Module               |

|                                         | ♀ ♀ · time 0<br>♀ · instrs 5 items             |                   | nternal<br>JPU_instr |

|                                         | Source Viewer<br>Root expression does not have | declaration sourc | ce ref               |

3. Click the blue instrs = 5 items link in the left panel.

|                                            | Data Browser – sys                                  |              |              |                 |

|--------------------------------------------|-----------------------------------------------------|--------------|--------------|-----------------|

| File View Tools                            |                                                     |              |              |                 |

| Prev Next New Window Source Edit Modify    | Config                                              |              |              | G<br>Lock Close |

| Expression: SYS                            | 亳 sys.instrs: list of instr = 5 items               |              |              |                 |

| Data Content                               | Data Details                                        |              |              |                 |

| ⊡ 19 sys = sys-@0<br>⊕ 12 instrs = 5 items | 🗀 Fields 🖉 Events 🕕 Methods 🎴 List ite              | enns         |              |                 |

|                                            | # Value                                             | opcode       | op1          | kind            |

|                                            | 0 reg instr-@1                                      | ADD          | REG0         | reg             |

|                                            | 1 reg instr-@2                                      | ADD          | REGO         | reg             |

|                                            | 2 imm instr-@3<br>3 imm instr-@4                    | ADDI<br>ADDI | REG0<br>REG0 | imm<br>imm      |

|                                            | 4 reg instr-@5                                      | ADD          | REGO         | reg             |

|                                            | Source File: CPU_instr.e<br>29<br>30<br>31 <'<br>32 |              |              |                 |

| Sys.instrs                                 |                                                     | 5 List items |              | Ready           |

| [ — ·/······                               |                                                     |              |              | , noticity      |

The list of five generated instructions appears in the top right panel.

4. Double-click the blue *reg instr-@1* link in the top right panel.

The generated values for the fields of the first instruction object appear in the right panel.

|                                                                                                              | Data Browser – sys                                                                                           |                                      | •                                                             |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------|

| File View Tools                                                                                              |                                                                                                              |                                      |                                                               |

| Prev Next New Window Source Edit Modify                                                                      | config                                                                                                       |                                      | 😚 💭<br>Lock Close                                             |

| Expression: SYS                                                                                              | 🖿 sys.instrs[0]: reg instr (lik                                                                              | <pre>ce any_struct) = reg inst</pre> | r–@1                                                          |

| Data Content                                                                                                 | Data Details                                                                                                 |                                      |                                                               |

| ⊡ 13 sys = sys-@0                                                                                            | Fields S Events () Methods                                                                                   | List items                           |                                                               |

| instrs = 5 items                                                                                             | 🔄 🖁 况 🛛 Name                                                                                                 | Value                                | Module                                                        |

| instre[1] = reg instr-@2<br>instre[2] = imm instr-@3<br>instre[3] = imm instr-@4<br>instre[4] = reg instr-@6 | <ul> <li>% орососе</li> <li>% ор1</li> <li>. Kind</li> <li>. % ор2</li> </ul>                                | ADD<br>REG0<br>reg<br>REG1           | CPU_instr<br>CPU_instr<br>CPU_instr<br>CPU_instr<br>CPU_instr |

| sys.instrs[0]                                                                                                | Source File: CPU_instr.e<br>30 Creates the stre<br>31 // creates the stre<br>32 !instrs: list of in<br>33  ; |                                      | Ready                                                         |

- **Tip** If the results you see are significantly different from the results shown here, use the UNIX diff utility to compare your version of the *e* files to the files in *tutorial/gold/*.

- 5. Click each of the other *instrs[n]* lines in the left panel and review their contents in the right panel to confirm that the instructions follow both the general constraints for CPU instructions and the constraints for this particular test.

Based on the definition, specification constraints, and test constraints that you have provided, the Specman Elite generator quickly generated the desired instruction stream. Now you are ready to drive this instruction stream into the DUT and run simulation.

# 5 Driving and Sampling the DUT

# **Goals for this Chapter**

In this chapter, you will drive the DUT with the instruction stream you generated in the last chapter.

In a typical verification environment, where the DUT is modeled in an HDL, you need to link the Specman Elite system with an HDL simulator before running simulation. To streamline this tutorial, we have modeled the DUT in e.

# What You Will Learn

In this chapter, you learn how to describe in e the protocols used to drive test data into the DUT. Although this tutorial does not use an HDL simulator, the process of driving and sampling a DUT written in HDL is the same as the process for a DUT written in e.

As you work through this chapter, you gain experience with these features of the Specman Elite verification system:

- **DUT signal access**—You can easily access signals and variables in the DUT, either for driving and sampling test data or for synchronizing TCMs.

- **Simulator interface automation**—You can drive and sample a DUT without having to write PLI (Verilog simulators) or FLI/CLI (VHDL simulators) code. The Specman Elite system automatically creates the necessary PLI/FLI calls for you.

• **Time consuming methods (TCMs)**—You can write procedures in *e* that are synchronized to other TCMs or to an HDL clock. You can use these procedures to drive and sample test data.

This chapter introduces the *e* constructs shown in Table 5-1.

| Construct           | How the Construct is Used                                                                                                                                                                                  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| emit                | Triggers a named event from within a TCM.                                                                                                                                                                  |  |

| @                   | Synchronizes the TCMs with an event.                                                                                                                                                                       |  |

| event               | Creates a temporal object, in this case a clock, that is used to synchronize the TCMs.                                                                                                                     |  |

| 'hdl_signal_name'   | Accesses a signal in the DUT.                                                                                                                                                                              |  |

| method () <b>is</b> | Creates a procedure (method) that is a member of a struct and<br>manipulates the fields of that struct. Methods can execute in a<br>single point of time, or they can be time consuming methods<br>(TCMs). |  |

| pack ()             | Converts data from higher level <i>e</i> structs and fields into the bit or byte representation expected by the DUT.                                                                                       |  |

| wait                | Suspends action in a TCM until the expression is true.                                                                                                                                                     |  |

#### Table 5-1 New Constructs Used in this Chapter

The steps for driving and sampling the DUT are:

- 1. Defining the protocols.

- 2. Running the simulation.

The following sections describe how to perform these steps.

# **Defining the Protocols**

There are two protocols to define for the CPU:

- **Reset protocol**—drives the *rst* signal in the DUT.

- **Drive instructions protocol**—drives instructions into the DUT according to the correct protocol indicated by *fetch1* and *fetch2* signals.

Drive instructions protocol has one TCM for *pre-run generation*, where the complete list of instructions is generated and then simulation starts. There is another TCM for *on-the-fly generation*, where signals in the DUT are sampled before the instruction is generated. The test in this chapter uses the simple methodology of pre-run generation, while subsequent tests in this tutorial use the more powerful on-the-fly generation.

All the TCMs required to drive the CPU are described briefly in Table 5-2. A complete description of one of the TCMs follows the table. You can also view the  $CPU\_drive.e$  file in the *src* directory, if you want to see the complete description of the other TCMs in *e*.

| Name                   | Function                                                                                                                                                                                                            |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| drive_cpu()            | Calls <i>reset_cpu</i> (). Then, depending on whether the list of CPU instructions is empty or not, calls <i>gen_and_drive_instrs</i> () or <i>drive_pregen_instrs</i> ().                                          |  |

| reset_cpu()            | Drives the <i>rst</i> signal in the DUT to low for one cycle, to high for five cycles, and then to low.                                                                                                             |  |

| gen_and_drive_instrs() | Generates the next instruction and calls <i>drive_one_instr()</i> .                                                                                                                                                 |  |

| drive_pregen_instrs()  | Calls <i>drive_one_instr()</i> for each generated instruction.                                                                                                                                                      |  |

| drive_one_instr()      | Sends the instruction to the DUT. If the instruction is an immediate instruction, also waits for the <i>fetch2</i> signal to rise and sends the second byte of data. Then waits for the <i>exec</i> signal to rise. |  |

Table 5-2 TCMs Required to Drive the CPU

Figure 5-1 shows the *e* code for the *drive\_one\_instr* () TCM. The CPU architecture requires that tests drive and sample the DUT on the falling edge of the clock. Therefore, all TCMs are synchronized to *cpuclk*, which is defined as follows:

```

extend sys {

event cpuclk is (fall('top.clk')@sys.any);

};

```

Driving and Sampling the DUT

#### Figure 5-1 The drive\_one\_instr () TCM

```

drive_one_instr(instr: instr) @sys.cpuclk is {

var fill0 : uint(bits : 2) = 0b00;

wait until rise('top.fetch1');

emit instr.start_drv_DUT;

if instr.kind == req then {

'top.data' = pack(packing.high, instr);

} else {

// immediate instruction

'top.data' = pack(packing.high, instr.opcode,

instr.op1, fill0);

wait until rise('top.fetch2');

'top.data' = pack(packing.high, instr.imm'op2);

};

wait until rise('top.exec');

// execute instr in refmodel

//sys.cpu_refmodel.execute(instr, sys.cpu_dut);

};

```

The assignment statements in Figure 5-1 show how to drive and sample signals in an HDL model. Each pair of single quotation marks identifies an object as an HDL signal.

The *start\_drv\_DUT* event emitted by *drive\_one\_instr* is not used by any of the TCMs that drive the CPU. You will use it in a later chapter to trigger functional coverage analysis.

The last line shown in Figure 5-1 executes the reference model and is commented out at the moment. You will use it in a later chapter to trigger data checking.

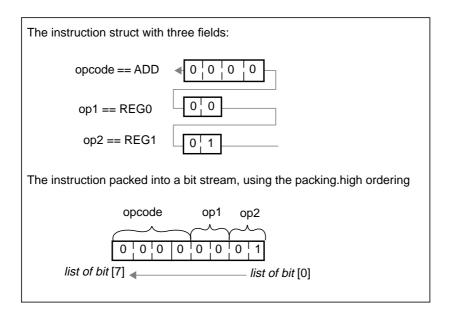

The **pack**() function is a Specman Elite built-in function that facilitates the conversion from higher level data structure to the bit stream required by the DUT. In Chapter 3, "Creating the CPU Instruction Structure", you used the % character to identify the fields that should be driven into the DUT. The **pack**() function intelligently and automatically performs the conversion, as shown in Figure 5-2.

#### Figure 5-2 A Register Instruction as Received by the DUT

## **Running the Simulation**

This procedure, which involves loading the appropriate files and clicking the Test button, is very similar to the procedure you used in the last chapter to generate the first test.

The difference is that this time you are including the DUT (contained in *CPU\_dut.e*) and TCMs that drive it (contained in *CPU\_drive.e*).

### Procedure

To run the simulation:

- 1. Copy the *src/CPU\_dut.e* to the working directory.

- 2. Copy the *src/CPU\_drive.e* to the working directory.

- 3. Open the working directory's copy of the *CPU\_top.e* file in an editor.

4. Find the lines in the file that look like this:

```

// Add dut and drive:

//import CPU_dut, CPU_drive;

```

5. Remove the comment characters in front of the *import* line so the lines look like this:

```

// Add dut and drive:

import CPU_dut, CPU_drive;

```

- 6. Save the *CPU\_top.e* file.

- 7. Click the Reload button to reload the files for test 1.

- **Tip** If you have exited Specview, you must reinvoke it and load *CPU\_tst1.e* again. To do so, enter the **specview** command at the UNIX prompt, click on the Load button, and choose *CPU\_tst1.e*.

- **Tip** If you see a message such as

\*\*\* Error: No match for 'CPU\_dut.e'

you need to check whether the working directory contains the following files:

| CPU_instr.e | CPU_drive.e |

|-------------|-------------|

| CPU_misc.e  | CPU_top.e   |

| CPU_dut.e   | CPU_tst1.e  |

Add the missing file and then click the Reload button.

8. Click the Modules button to confirm that six modules are loaded:

| CPU_instr | CPU_drive |

|-----------|-----------|

| CPU_misc  | CPU_top   |

| CPU_dut   | CPU_tst1  |

**Tip** If some of the modules are missing, first check whether you are loading the *CPU\_top.e* file that you just modified. The modified *CPU\_top.e* file must be in the working directory. Once the modified *CPU\_top.e* file is in the working

Specman Elite Tutorial

directory, click the Restore button. This action should remove all the currently loaded modules from the session. Then click Load and choose *CPU\_tst1.e* in the Select A File dialog box.

9. Click Test to run the simulation.

You should see the following messages (or something similar) in the Specview main window.

```

Doing setup...

Generating the test using seed 0x1...

Starting the test...

Running the test...

DUT executing instr 0 : ADD REG0x0, REG0x1

DUT executing instr 1 : ADD REG0x0, @Ox05

DUT executing instr 2 : ADDI REG0x0, @Ox05

DUT executing instr 3 : ADDI REG0x0, @Ox05

DUT executing instr 4 : ADD REG0x0, REG0x1

Last specman tick - stop_run() was called

Normal stop - stop_run() is completed

Checking the test...

Checking is complete - 0 DUT errors, 0 DUT warnings.

Wrote 1 cover_struct to CPU_tst1_1.ecov

```

You can see from the output that five instructions were executed and no errors were found. It looks like the verification environment is working properly, so you are ready to generate a large number of tests.

## 6 Generating Constraint-Driven Tests

## **Goals for this Chapter**

In this chapter, you will run the second test described in "The Functional Test Plan" on page 2-3. To meet the objective of the second test, you must run the same test multiple times using constraints to direct random testing towards the more common operations of the CPU. Through this automatic test generation, we hope to gain high test coverage for the CPU instruction inputs.

## What You Will Learn

In this chapter, you learn how to quickly generate different sets of tests by simply changing the seed used for constraint-driven test generation. You also learn how to use weights to control the distribution of the generated values to focus the testing on the common CPU instructions.

As you work through this chapter, you gain experience with two of the Specman Elite verification system's enabling features:

- **Directed-random test generation**—This feature lets you apply constraints to focus random test generation on areas of the design that need to be exercised the most.

- **Random seed generation**—Changing the seed used for random generation enables the Specman Elite system to quickly generate a whole new set of tests.

This chapter introduces the e constructs and Specview menu commands shown in Table 6-1.

| Construct                      | How the Construct is Used                                                                                                                              |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| keep soft                      | Specifies a soft constraint that is kept only if it does not conflict with other hard <b>keep</b> constraints.                                         |  |

| select                         | Used with <b>keep soft</b> to control the distribution of the generated values.                                                                        |  |

| Command                        | How the Command is Used                                                                                                                                |  |

| Tools>>Config                  | Used to access the Generation tab of the Specman Elite<br>Configuration Options window for creating a user-defined seed<br>for random test generation. |  |

| File>>Save                     | Saves the current test environment, including the random seed, to a .esv file. You can load this file with the File>>Restore command.                  |  |

| Test>>Test with<br>Random Seed | Generates a set of tests with a new random seed.                                                                                                       |  |

| Table 6-1 | New Constructs and Specview Menu Commands Used in this |

|-----------|--------------------------------------------------------|

| Chapter   |                                                        |

The steps for generating random tests are:

- 1. Defining weights for random tests.

- 2. Generating and running tests with a user-specified seed.

- 3. Generating and running tests with a random seed.

The following sections describe these tasks in detail.

## **Defining Weights for Random Tests**

Because of the way that CPUs are typically used, arithmetic and logical operations comprise a high percentage of the CPU instructions. You can use the **select** construct with **keep soft** to require the Specman Elite system to generate a higher percentage of instructions for arithmetic and logical operations than for control flow.

#### Procedure

To see how weighted constraints are created in *e*:

- 1. Copy the *src/CPU\_tst2.e* file to the working directory.

- 2. Open the *CPU\_tst2.e* file in an editor.

- 3. Find the portion of the file that looks as follows and review the keep soft constraint.

| puts equal weight<br>on arithmetic and<br>logical operations | <'<br>extend instr {              |

|--------------------------------------------------------------|-----------------------------------|

| and less weight                                              | keep soft opcode == select {      |

| on control flow                                              | 30 : [ADD, ADDI, SUB, SUBI];      |

| operations                                                   | 30 : [AND, ANDI, XOR, XORI];      |

|                                                              | 10 : [JMP, JMPC, CALL, RET, NOP]; |

|                                                              | };                                |

|                                                              | };                                |

|                                                              |                                   |

|                                                              | '>                                |

## **Generating Tests With a User-Specified Seed**

You can specify the random seed that the Specman Elite system uses to generate tests.

#### Procedure

This procedure shows how to create a random seed:

- 1. In the Specview main window, click Restore to remove all the *e* modules from the current session.

- 2. Click Load. Then double-click the *CPU\_tst2.e* file.

The Specman Elite system loads the CPU\_tst2.e file along with its imported modules.

3. Click Modules and confirm that the following modules are loaded:

| CPU_instr | CPU_drive |

|-----------|-----------|

| CPU_misc  | CPU_top   |

| CPU_dut   | CPU_tst2  |

4. Click the Config button or choose Config from the Tools menu.

The Specman Elite Configuration Options window opens.

- 5. Choose the Generation tab and then enter a number of your choice in the text box under Seed.

- 6. Click OK to save the settings and close the window.

- 7. Click the Test button on the Specview main window.

The Specman Elite system runs the test with the your seed and reports the results.

8. In the Tools menu, choose Data Browser and then choose Show Data Sys.

The Data Browser GUI appears.

9. Click the blue *instrs* = 59 *items* link in the left panel.

Instructions are listed in the top right panel. By default, only the first 25 instructions are listed. You can click the Config button in the Data Browser, and then change the number of list items to 59 to list all of the instructions.

You should see an approximately equal distribution of arithmetic and logical operations, and about one-third as many control flow operations as there are either arithmetic or logical operations.

| - Data Browser - sys                    |                                             |                               |           |

|-----------------------------------------|---------------------------------------------|-------------------------------|-----------|

| File View Tools                         |                                             |                               |           |

| Prev Next New Window Source Edit Modify | config                                      |                               | G 💭       |

| Expression: Sys                         | 🔄 sys.instrs: list of instr = 59 item       | ns (first 25 items)           |           |

| Data Content                            | Data Details                                |                               |           |

| ⊡ 🗐 sys = sys-@1                        | 🗀 Fields 🖉 Events 🕕 Methods 🕒 Lie           | stitems                       |           |

| 庄 🖳 instrs 😑 59 items                   |                                             |                               |           |

| 庄 🗀 cpu_env = cpu_env-@2                | # Value                                     | opcode op1                    | kind      |

| apu dut = cpu_dut-@0                    | 0 imm instr-@3                              | ADDI REG3                     | imm 🖉     |

|                                         | 1 imm instr-@4                              | XORI REG1                     | imm       |

|                                         | 2 reg instr-@5                              | ADD REG1                      | reg       |

|                                         | 3 reginstr-@6                               | ADD REG2                      | reg       |

|                                         | 4 imm instr-@7                              | ADDI REG3                     | imm       |

|                                         | 5 reginstr-@8                               | ADD REG2                      | reg       |

|                                         | 6 imm instr-@9                              | XORI REGO                     | imm       |

|                                         | 7 imm instr-@10                             | SUBI REGO                     | imm       |

|                                         | 8 reginstr-@11                              | RET REG2                      | reg       |

|                                         | 9 imminstr-@12                              | ANDI REG2                     | imm       |

|                                         | 10 imm instr-@13                            | ADDI REG2                     | imm       |

|                                         | 11 imm instr-@14                            | ANDI REG3                     | imm       |

|                                         | 12 imm instr-@15                            | XORI REGO                     | imm       |

|                                         | 13 reginstr-@16                             | ADD REG2                      | reg       |

|                                         | 14 imm instr-@17<br>15 imm instr-@18        | CALL REG2<br>ANDI REG2        | imm       |

|                                         |                                             | ANDI REGZ                     | Imm       |

|                                         | ▲ <b>▼</b>                                  |                               |           |

|                                         | Source File: CPU_instr.e                    |                               |           |

|                                         | 29                                          |                               |           |

|                                         | 30 ====================================     |                               |           |

|                                         | 31 <'                                       |                               |           |

|                                         | 32                                          |                               |           |

|                                         | 33 type cpu_opcode: [                       | // Opcodes                    |           |

|                                         | 34 ADD, ADDI, SUB, SUBI,                    |                               |           |

|                                         | 35 AND, ANDI, XOR, XORI,                    |                               |           |

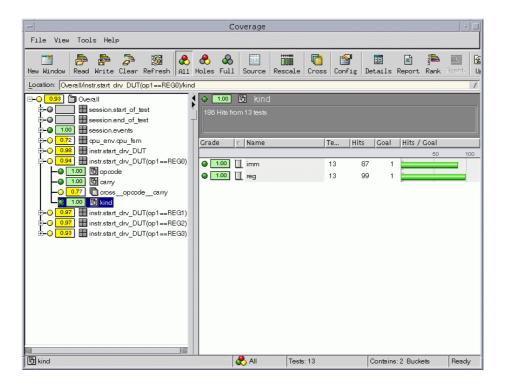

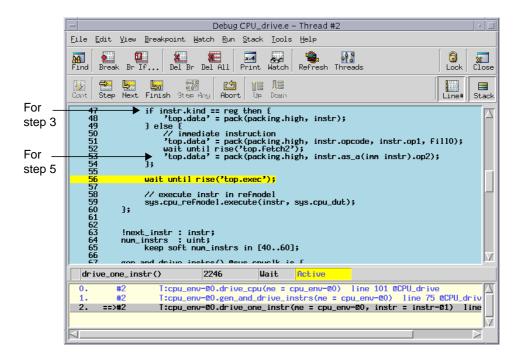

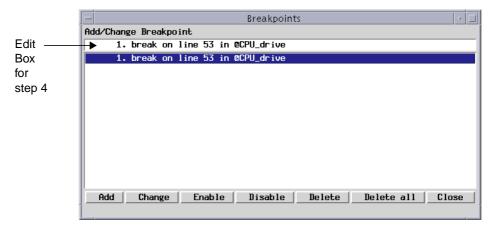

|                                         | 36 JMP, JMPC, CALL, RET,                    |                               |           |