# RESEARCH SCHOLARS' DAY

100101010

**DEPARTMENT OF COMPUTER SCIENCE & ENGINEERING**

February 6, 2010

00

**INDIAN INSTITUTE OF TECHNOLOGY KHARAGPUR**

# **Department of Computer Science & Engineering**

The Department of Computer Science & Engineering was initiated in 1980 and the first B. Tech. batch graduated in 1982. Apart from being the department producing the first batch of graduates in Computer Science and Engineering amongst the Indian Institutes of Technology, this is one of the most reputed centres for Computer Science education and research in the country.

The hallmarks of the department are in the breadth of its academic curricula and diversity in fundamental research and industrial collaborations. Collaborative research is ongoing with researchers in internationally acclaimed universities and research institutions abroad and in India such as UCLA, USC, TIFR Mumbai, ISI Kolkata, RRI Bangalore, Perimeter Institute of Theoretical Physics, and SAC Bangalore. The Department has long-term research partnerships with leading companies such as Intel, National Semiconductors, Microsoft, General Motors, Synopsys, Sun Microsystems and Texas Instruments.

The alumni of this department are well established all over the globe achieving excellence in professional fields as well as in academics and research, and holding positions of rare distinction in leading industries and academic institutions of the world.

# Message from the head

It is indeed a matter of great pleasure for me that my department is going to host the Research Scholar's Day on 6th February, 2010. On this day, the research scholars of the department will present their research activities in the form of technical presentations and posters. This will not only give them an opportunity to demonstrate their latest research findings to peers and colleagues in the institute but also act as a forum to highlight the diverse research activities of the department. Interactions with students and faculties will surely motivate the scholars to develop and improve their research work.

The success of an event like this depends largely on the collective participation and I note with great satisfaction how every faculty and research student of the department have worked hand in hand to make the event successful. I congratulate them all for their effort and wish them and the event a grand success.

Indranil Sen Gupta

# List of Current Ph.D. Scholars

Arnab Sarkar **Bibhas Ghosal Bivas** Mitra Bodhisatwa Majumdar Chandan Karfa Chester Rebeiro Chhabi Rani Panigrahi Debi Prosad Dogra **Dinesh Dash** ESF Najumudheen Gopal Paul Ishani Chakraborty Joydeep Chandra Kallol Mallick Kamalesh Ghosh Mahesh Raghunath Shirole Manjira Sinha Manoj Dixit Maunendra Sankar Desarkar Plaban Kumar Bhowmick Prasenjit Mandal Pravanjan Choudhury Priyankar Ghosh Rajarshi Pal

R Rajendra Prasath Rajib Maiti Rajiv Ranjan Suman Rishiraj Saha Roy Sanjay Chatterji Santosh Ghosh Saptarshi Ghosh Satya Gautam Vadlamudi Shyamosree Pal Sk. Subidh Ali Soma Saha Soumen Bag Soumyadip Banerjee Soumyajit Dey Sourav Dandapat Sourav Das Srobona Mitra Subhankar Mukherjee Subhasish Dhal Subhendu Bhadra Subrata Nandi Sudip Roy Sumanta Pyne Tapas Samanta

#

# **RESEARCH ABSTRACTS**

Arnab Sarkar

Email: arnab@cse.iitkgp.ernet.in

Arnab Sarkar received the B.Sc. degree in Computer Science in 2000 and B.Tech degree in Information Technology in 2003 from University of Calcutta, Kolkata, India. He received the M.S. degree in Computer Science and Engineering at the Indian Institute of Technology (IIT), Kharagpur, India in 2006 and is currently pursuing his PhD in the same institute. He received the National Doctoral Fellowship (NDF) from AICTE, Ministry of HRD, Govt. of India, in 2006 and the MSR India PhD fellowship from Microsoft Research Lab India, in 2007. He is currently pursuing his research as a Microsoft Research Fellow. His current research interests include real-time scheduling, system software for embedded systems and computer architectures.

Supervisor: Prof. Sujoy Ghose

# Low Overhead Real-time Proportional Fair Scheduling

The plethora of different types of embedded systems today has initiated the emergence of various complex realtime applications which require operating under stringent performance and resource constraints. Today's powerconstrained hand held devices simultaneously executing a mix of applications like real-time signal processing, Continuous media (audio and video streams), email, web browsing, etc. provide an interesting example. Another example is provided by the automotive control systems which concurrently execute a mix of hard, soft and non real-time applications on a distributed platform composed of heterogeneous multi-processors.

In recent years, proportional fair scheduling (Pfair, ERfair, Completely Fair Scheduler (CFS), etc.) is being accepted as an effective resource management strategy for the integrated scheduling of these different applications with various degrees of timeliness criticality. This is primarily because of its ability to provide temporal isolation to each client task from the ill-effects of other "misbehaving" tasks attempting to execute for more than their prescribed shares of a resource. Moreover, many applications such as multimedia audio and video streams not only demand meeting deadlines, but also demand CPU reservation to ensure a minimum guaranteed Quality of Service (QoS). These demands are of the form: reserve X units of time for application A out of every Y time units. Proportional fair schedulers with their ability to provide well-defined rate specifications form a more flexible and suitable scheduling strategy in the design of these systems.

However, in spite of its theoretical importance and usefulness, actual implementations of these fair schedulers are limited mainly due to the high scheduling, inter-processor task migration and cache-miss related overheads incurred by them. Scheduling overheads refer to the delay incurred in selecting the next task for execution. As proportional fair schedulers generally need to sort operation deadlines of tasks, they suffer scheduling complexities that are at least logarithmic in the number of tasks. Migration related overheads refer to the time spent by the operating system to transfer the complete state of a thread from the processor where it had been executing to the processor where it will execute next after a migration. Obviously, the more loosely-coupled a system, the higher will be this overhead.

Cache-miss related overheads refer to the delay suffered by resumed threads of execution due to compulsory and conflict misses while populating the caches with their evicted working sets. Therefore, processors are affined to tasks whose working sets currently exist in cache and are valid (non-dirty) since their execution results in cache hits. Obviously, the more recently a task was executed in a particular processor, higher is the probability of its working set to be present in that processor's cache. Proportional fair schedulers are usually ignorant of the affinities between tasks and their executing processors which may cause unrestricted inter-processor task migrations and heavy cache-misses.

This research endeavors to develop a framework for fast, flexible algorithms that can work effectively under a variety of practical situations like limited power, overload, faults, etc. over a wide range of architectures. The proposed fair scheduling framework is based on the following four principal mechanisms:

- (1) Frame-based Scheduling (periodic partitioning followed by global resynchronization) to guarantee bounded fairness in O(1) time and restrict migrations,

- (2) Intelligent Partition-Merge Techniques to minimize global scheduling and migrations

- (3) Effective use of Processor Slack to manage power, overloads, faults, etc. and

- (4) Awareness of Task-to-Processor Mutual Affinity for overhead management.

The methods are founded on a set of theoretical bounds and experimental analysis to provide scope for developing application-specific schedulers under various fairness-speed-power-overload requirements.

We have been able to remove the O(lg n) scheduling complexity barrier of typical proportional fair schedulers by the O(1) frame-based proportional fair algorithm Frame Based Proportional Round-Robin (FBPRR) which provides good bounded fairness guarantees. The multiprocessor counterpart of this algorithm called Partition Oriented Frame Based Fair Scheduler (POFBFS) is able to reduce the number of migrations in current ERfair schedulers by upto 100 times. Proportional round-robin scheduling strategies and clustering techniques have been employed within frames to further improve the fairness properties of these schedulers. We have developed Sticky-ERfair, a strictly ERfair global algorithm that reduces both the number of migrations and cache-misses by upto 40 times. Work on a partition-merge scheduling strategy with strict ERfairness guarantees is in progress. Our algorithm ERfair Scheduling with Processor Shutdown (ESPS) attempts to reduce processor energy consumption in ERfair systems by locally maximizing processor shut-down intervals through a novel procrastination scheme. Currently, we are developing its multi-processor systems using efficient low-overhead admission control. Development of a fault tolerance methodology to handle single transient software faults in ERfair systems is in progress. As a future plan, we intend to develop fault-tolerant techniques (mainly for the automotive domain) to handle distributed and heterogeneous multi-processor systems by appropriate static characterization followed by partition-oriented on-line scheduling.

# **Bivas Mitra**

Email: bivasm@cse.iitkgp.ernet.in

**Bivas Mitra** received his B.Tech. from Haldia Institute of Technology, Vidyasagar University in 2001, and M.Tech. from IIT Kharagpur in 2003 both in Computer Science and Engineering. During February 2003 to January 2006, he worked as a lecturer in the department of Computer Science and Engineering at Haldia Institute of Technology. In January 2006, he joined as a research scholar in the department of Computer Science and Engineering, IIT Kharagpur. In his PhD tenure, he has received various fellowships like national doctoral fellowship, SAP Labs India doctoral fellowship etc. and several student travel grants to participate in different international conferences. His research interests include peer-to-peer networks, complex networks, networks modeling, optical networks, wireless internet etc.

#### Supervisors: Prof. Niloy Ganguly and Prof. Sujoy Ghose

## Analyzing the Dynamics behind the Emergence of Stable Peer-to-Peer Networks

In this research, we primarily focus on understanding the dynamics of large scale peer-to-peer (p2p) networks. Two different aspects, namely 'network stability' and 'network emergence' are taken into consideration.

**Network stability**: Nodes in the peer-to-peer network join and leave the network frequently without any central coordination. This churn of peer nodes can partition the network into smaller components and can breakdown the communication among peers. The stability of the network can also get severely affected through intended attack targeted towards the important peers. Denial of Service (DoS) attack, eclipse attack, sybil attack, file poisoning are some of the important attacks that affect the stability of the p2p networks. Hence performing comprehensive theoretical analysis of stability of the peer-to-peer networks against peer churn and attack and subsequently deciding upon the optimal network is an important research problem.

**Network emergence**: Peer-to-peer networks are formed mainly as a result of the bootstrapping protocols followed by incoming nodes, peer churn and rewiring of the existing links. Discovering the relationship between the node dynamics and emergence of superpeer networks is an interesting and nontrivial research problem. The classical studies have shown the emergence of scale free networks as a result of the preferential attachment of incoming nodes with the `good' existing nodes. However, we observe that the superpeer networks follow bimodal degree distribution that sharply deviates from the power law behavior of scale free networks. Hence the classical theories related to preferential attachment and its variations need to be modified to explain such deviation.

Methodologies followed to analyze network stability and to explain the emergence of superpeer networks are mainly drawn from complex network theory.

**Stability analysis**: Our research concentrates on the application of classical concepts of statistical mechanics like percolation theory, generating function formalism, condensation theory etc to develop an analytical framework to measure stability of p2p networks. We characterize the topology of the network by degree distribution pk (fraction of nodes having degree k) and node dynamics by another probability distribution fk (probability of removal of a node of degree k). The stability of networks is primarily measured in terms of a fraction of nodes called percolation threshold removal of which disintegrates the network into large number of small, disconnected components. We propose an analytical framework to measure the stability of peer-to-peer networks against peer churn and attack. During churn, nodes in the networks are removed randomly (random failure). During attack, important nodes are removed and the importance of a node is mainly characterized by its connectivity and bandwidth. Experimental validation of the theoretical results is done in two folds depending upon the generation of the peer-to-peer networks (simulating the network and using topological snapshot of Gnutella network). Next we report some of the significant observations of p2p networks in face of peer churn and attack.

**Peer churn: 1.** It is important to observe that for the entire range of peer fractions, the percolation threshold is greater than 0.7 which implies that superpeer networks are quite robust against churn. **2.** Small fraction of superpeers in the network (specifically when it is below 5%) results in a sharp fall of percolation threshold, which shows that the vulnerability of the network drastically increases when the fraction of superpeers is low.

Attack: 3. In networks with peer degree 1, 2 and 3, the removal of only a fraction of superpeers causes breakdown of the network. 4. However as peer degree increases beyond 4, a fraction of peers is required to be removed even after removal of all the superpeers to dissolve the network.

**Network emergence:** We develop an analytical framework to explain the appearance of bimodal degree distribution in superpeer networks. The evolution of the network is mainly driven by the joining of incoming nodes through the bootstrapping protocol, departure of peers due to peer churn and rewiring of existing links. We review different bootstrapping protocols followed by the peer 'servents' like limewire, mutella etc and show that they can be easily modeled by various node attachment rules. Each incoming node joins the network with some finite bandwidth which restricts its maximum/cutoff degree. On the other hand, peers may leave the network randomly without any central coordination. This may result in the change in topological structure, increase in the network diameter and subsequently disintegration of the networks into small size components. In order to prevent network breakdown and to maintain the quality of service, rewiring of existing links takes place at the regular interval. Our framework shows that the interplay of finite bandwidth with node property and node dynamics plays key role in the emergence of bimodal distribution. We find that **1.** Increase in the cutoff degree reduces the amount of superpeers in the network. **2.** The analysis of the emerged network shows that the joining of the resourceful nodes initially increases the amount of superpeers in the network, but after a threshold level, the amount does not increase. **3.** A small churn results in a sharp reduction in the superpeer fraction in the network. More specifically, after a threshold amount of churn, the bimodality in the degree distribution disappears.

In stability analysis, we have assumed that the network is uncorrelated in nature. However, most of the real world technological networks like Internet, web network, peer-to-peer network (like Gnutella) exhibit degree-degree correlation in their network structure. We aim to incorporate this degree correlation in our analytical framework so that the theoretical results can able to provide exact results for real world networks also. Analyzing the emergence of superpeer networks is our ongoing research work. We believe that the rigorous analysis of the framework can reveal interesting conclusions regarding the topology of the emerging network. Subsequently, performing comparative analysis between the theoretical results with the real world network like Gnutella can provide us the `self-organizing' local rules behind the emergence of the Gnutella network.

Chandan Karfa

**Chandan Karfa** received the B.Tech. degree in Information Technology from University of Kalyani, Kalyani, India in 2004 and the MS (by research) degree in Computer Science and Engineering from Indian Institute of Technology (IIT), Kharagpur, India in 2007. Since January 2008, he has been a research scholar in the Department of Computer Science and Engineering in IIT, Kharagpur. He received the Best Student Paper Award for his paper in ADCOM conference in 2007, Microsoft Research India PhD fellowship from Microsoft Research India in 2008, Innovative Student Projects Award (Master Level) from Indian National Academy of Engineering (INAE) in 2008, first prize in EDA contest in 22<sup>nd</sup> International Conference on VLSI Design 2009 and third prize in PhD poster contest in TechVista 2010 organized by Microsoft Research India. His current research interests include formal verification of circuits and systems and CAD for VLSI.

#### Supervisors: Prof. C. R. Mandal and Prof. D. Sarkar

# Equivalence Checking in Embedded System Design Verification

Present day embedded systems synthesis consists in application of several sophisticated transformation techniques on the input 0 to improve its performance in terms of execution time, energy consumption, etc. Parallelizing code transformations are becoming increasingly important for multi-core/multiprocessor embedded systems. Sequential optimizing code transformations, human optimizations and transformations involved for design synthesis are also routinely applied. In this context, verification of the overall transformation is crucial for the reliability provided it meets the acceptable design cycle time. Formal verification is an attractive alternative to traditional methods of testing and simulation which, for embedded systems, tend to be expensive, time consuming, and hopelessly inadequate. While model checking and theorem proving based methods suit property verification, equivalence checking is the most natural choice for verification; it shows that executions depicted by the input 0 are equivalent to those depicted by the transformed behaviour. The objective of our research is to show the correctness of several transformations applied during embedded system synthesis primarily by equivalence checking techniques. In the following, transformation techniques along with our of to verify them are discussed.

The input behaviour is in the form of a sequential code. Several code motion techniques such as speculation, reverse speculation, branch balancing, conditional speculation, etc., may be applied at the preprocessing stage of embedded system synthesis. The input behaviours are transformed significantly due to these transformations. We have developed an FSMD (finite state machines with datapath) model based method for checking equivalence between these sequential behaviours, i.e. the input behaviour and the transformed behaviour. Unlike many other reported techniques, this method is strong enough to handle both uniform and non-uniform types of code motions and the cases of control structure modifications of the original behaviours. Correctness and complexity of the method have been dealt with.

A high-level behaviour may be mapped to register transfer level (RTL) description during the synthesis process. The RTL consists of a description of the datapath net-list and a controller FSM. Towards establishing equivalence between

a high-level behaviour and its corresponding RTL behaviour, we have proposed a rewriting based method to extract the high-level behaviour from RTL description and then apply our FSMD based equivalence checking method. Unlike many other reported techniques, our method is capable of validating pipelined and multicyle operations, if any, spanning over several states. The correctness and complexity of the presented method have been treated formally.

The functional specification, which relies on a single-threaded sequential code, is not easy to deploy on highly concurrent heterogeneous multi-processor systems. A parallel model of computation (MoC) may be used as the programming model. However, writing an application depicting concurrency is time consuming and error prone which conflicts with the low time-to-market requirement of the present day embedded systems. An automated tool that will convert a sequential code to its equivalent concurrent behaviour is employed. In the case of streaming applications, Kahn process network (KPN) model of computation is often used. We consider KPN for modelling the concurrent behaviours in this work. The proposed method consists of the following steps: The consistency of FIFO communications in the KPN behaviour is modelled as two properties the correctness of which can be checked using any theorem prover such as YIECS. The KPN behaviour is then linearized so that it can be modelled as an array data dependence graph (ADDG). Finally, an ADDG based method, proposed in this work, is used to establish the equivalence. This work is in progress.

The parallel process network model, obtained from the sequential behaviour in an automated way or manually, may not be suitable for the target architectural platform. In this case, it is necessary to manipulate the amount of concurrency in the functional model. The transformation techniques like, process splitting, channel merging, process clustering, and unfolding and skewing, may be used to control the concurrency in the KPN behaviour according to the architectural constraints. The verification task of this phase, therefore, is to show the equivalence between two KPN behaviours. We plan to extend our ADDG based method to handle those transformations.

**Chester Rebeiro**

Email: chester@cse.iitkgp.ernet.in

Chester Rebeiro received his MS(2009) degree in Computer Science and Engineering from IIT Madras and BE (1998) in Instrumentation and Electronics from Bangalore University. From July 1999 to May 2009 he worked for the Centre for Development of Advanced Computing. Since May 2009, he is a research scholar and a senior research fellow in the Department of Computer Science and Engineering, IIT Kharagpur. His research interests are in Cryptography, Computer Architecture, and VLSI.

#### Supervisor(s) : Prof. Debdeep Mukhopadhyay and Prof. Indranil Sengupta

# Recent Trends in Side-Channel Attacks and Formal Modeling of Side-Channel Information Leakage

Most cryptographic algorithms used now-a-days are robust against a computationally bounded adversary. However in 1996 it was discovered that although the cryptographic algorithms are computationally secure, an implementation of the algorithm may leak secret information through covert channels such as power consumption, timing, and behavior in presence of faults. Such attacks are known as Side Channel Attacks. Many cryptographic algorithms in use today, like NIST's Advanced Encryption Standard (AES) have fallen prey to such forms of attack. A naive implementation would require just a small amount of side channel information to compromise the security of the entire system. It is therefore important to not only have robust cryptographic algorithms but to also have leakage proof implementations. However handcrafting such implementations and guaranteeing their security is difficult. This research focuses on developing tools and techniques that would provide users a platform to develop security infrastructure that is safe against classical cryptanalysis as well as side channel attacks.

Side channel attacks are broadly classified as active or passive attacks. Active attacks such as fault attacks tamper with the proper functioning of the system while passive attacks glean information from monitoring system's parameters such as power, timing, and radiation. The most common passive attacks are on VLSI chips and on devices that use cache memory. A simple power analysis of a VLSI chip can reveal the secret key with just a few power traces. Such attacks are easily preventable, but preventing the more deadly differential power analysis is not as straight forward. Encryptions that are run on devices that use cache memory have unequal encryption time. The variations in encryption time is dependent on the key. Thus simply monitoring the encryption timing is sufficient to obtain information about the secret key. The cheapest of all side channel attacks is the fault attack. An adversary can deliberately inject fault in the cryptographic device. By monitoring the cryptographic device under fault, the attacker can retrieve the secret key. The goal of the research is to develop a tool or to provide techniques that would notify the user about possible side channel leaks in the implementation. However the characteristics and attack algorithms used in each of the three side channels considered are different, making such a unified tool difficult to implement. As

the first step each of the three side channels are considered independently, and techniques would be developed to prevent leakages in each side channel.

When key recovery from side channel information is feasible, the security of the implemented cryptographic algorithm solely depends on the quantity of information about the key which can be extracted from the side channel measurements. The research involves building an information-theoretic model for side-channel leakage of cryptographic devices. In this, the device containing a secret key is modeled as a black box with a leakage function (which depends on the state transitions within the device) whose output is captured by an adversary as an observable parameter. This uses a theoretical concept of Mutual Information between the observed measurements and a hypothetical leakage to rank key guesses called Mutual Information Analysis (MIA). In other words, it studies the reduction in uncertainty on the guessed leakage function due the knowledge of a physical observable for a key hypothesis.

To counter side channel attacks targeting cache memory, the first step is to produce a generalization of the existing attacks and determine the cause of the leakages. The reason for cache attacks is due to the difference in the memory access time for a cache hit and a cache miss. It was found that the encryption time depends on the number of cache misses which in turn depends on the secret key. Another more subtle reason for cache attacks is in the distribution of cache misses with respect to the structure of the cipher. In modern processors cache misses are interleaved and parallelized therefore misses that occur together in a single round result in a lower miss penalty compared to cache misses occurring in different rounds where such accelerations cannot be done. To prevent such leakages, it is sufficient to protect only the first few rounds. These initial rounds are to be implemented such that the number of cache misses and the distribution of the misses should be uniform. This may require specifically designed encryption algorithms or tools which would alter the code at compile time to thwart leakages.

Fault attack is based on deliberate injection of fault in the cryptographic system. To thwart this attack the fault in the system needs to be detected. But it could be the case that while detecting fault, the countermeasures could open space for other kind of side channel attacks. So our current research in this area is to measure the robustness of existing countermeasures by exposing them to fault attack and other side channel attacks like cache attack and power attack. As a first phase of our research we are currently measuring the robustness of existing countermeasures on AES.

A unified tool to prevent all possible side channel attacks requires incorporation of all individual counter measures keeping in mind the performance overhead and the compatibility between the countermeasures.

Debi Prosad Dogra

**Debi Prosad Dogra** received a B.Tech degree in Computer Science from Haldia Institute of Technology, Haldia in 2001, and an M.Tech degree in Computer Science from Indian Institute of Technology Kanpur in 2003. From June 2003 till July 2006, he worked as a lecturer in Computer Science department of Haldia Institute of Technology, Haldia. From October 2006 till May 2007, he worked in the multimedia research team of Electronics & Telecommunication Research Institute, Daejeon, South Korea as a researcher. Since July 2007, he has been a research scholar in the department of Computer Science and Engineering at IIT Kharagpur. His research interests are in the areas of Image Segmentation and Video Surveillance.

Supervisors: Prof. A. K. Majumdar and Prof. S. Sural

# A Computer Vision Based Approach for Conducting Hammersmith Infant Neurological Examination

Nowadays, application of computer vision to improve the efficacy of telemedicine and health-care systems is being considered as a good alternative. Advancement in image and video processing technology has accelerated its usage for betterment of daily livelihood of the mankind. For example, to help in the process of measuring exact postures of an infant while medical examinations are being conducted, a video based approach can be utilized. Certainly, it increases the efficiency and quality of experiments.

The work proposed in this article tries to address one such application where a computer vision based scheme can greatly increase the efficacy of the system. A widely used experiment that is carried out upon infants of less than two years of age is Hammersmith infant neurological examination. It is used for recording neurological development of the baby. While examination is going on, postures and reactions of the infant under consideration are recorded. An overall score that quantifies the neurological development index at the time of experiment is assigned to the infant. The experiment is carried out repetitively at different ages of the baby e.g. 3, 6, 9, 12 months and so on. Accurate measurement of posture, arm recoil, arm traction, leg recoil, leg traction, popliteal angle, head control, reflexes and reactions are parts of the experiment that are essential for estimating the overall neurological development index.

A computer vision based approach can be of great help in this regard. In this work, we propose a semi-automatic methodology to conduct the experiments. Some parts of the experiments can be carried out in a fully automatic manner while a semi-automatic scheme is proposed for remaining experiments. A complete description of the proposed scheme is as follows. The infant under consideration is placed on a mattress of white background. Cloths, hats or other objects for covering head are not used during experiments. This is done upon recommendation of physician. Two digital cameras used for capturing images / videos. Cameras are fixed such that one of it captures the top view of the infant (in supine posture) and the other one captures the front view (in sitting posture). We have used CIF frame format (frame size 352 X 288 pixels) for recording images. Illumination of the environment is kept

unchanged during the entire period of experiment. First frame is captured without any foreground object. It is used to eliminate background parts. A pixel-wise difference is calculated between current and background frames to obtain the foreground parts. Next, a morphological operator that performs erosion and dilation operations with a 3X3 structuring element is applied to remove any noise present. Even after morphological operations, however, some noise remains. To eliminate those noisy regions, contours of isolated regions are detected. The region with highest contour length is assumed to be the infant object. In order to cluster the foreground object into segments having similar characteristics, a clustering algorithm is applied. It is found that after initial classification many insignificant regions of tiny size are produced. Those segments are regarded as noise with respect to larger ones. To remove such insignificant segments, a region processing algorithm based on boundary sharing is proposed and used. Once initial classification of pixels is done, higher level of processing can be applied for object extraction.

Next, to extract the shape and boundary of the infant object, a model based approach is proposed. It is found through observations that different shapes of the infant can be parameterized using distinguishable features. For example, during posture estimation experiment, a method of skeletonization can be used to extract the skeleton of the baby and later it can be matched with some pre-existing models for assigning score. Images from the camera that is placed for capturing the top view of the infant at supine posture are used for this. Similarly, for arm and leg recall experiments, its output can be used to measure the final positions of the arms and legs after extension. In future, we have plan to use images from both cameras for extraction of experiment specific features e.g. location of head, position and dimensions of arms, legs and torso.

An image or video based semi-automatic scheme is always considered as a good alternative to many conventional approaches of conducting medical experiments. It can greatly increase the efficacy and accuracy of the experiments. In this work, we aim to propose a method for conducting the Hammersmith neurological examination. It is found that the tool can reduce the work load of the persons involved with such jobs. The problem is still a tough one and it is yet to receive enough attention. Our approach is convincing one and it can further be examined for a full scale implementation.

# **Dinesh Dash**

Email: dineshd@cse.iitkgp.ernet.in

**Dinesh Dash** received his B.Sc. degree in Computer Science from University of Calcutta, Kolkata, India in 2000. He also received his M.Sc. in Computer and Information Science in 2002 and M.Tech. in Computer Science and Engineering in 2004 from the same institute. Dinesh worked as a lecturer at Asansol Engineering College, Asansol, West Bengal, India from 2004 to 2007. He is currently working towards his Ph.D. degree at the department of Computer Science and Engineering at Indian Institute of Technology Kharagpur. His research interests are in the applications of geometry in the field of sensor networks.

#### Supervisors: Prof. Arobinda Gupta and Prof. Arijit Bishnu (ISI Kolkata)

## Geometric Problems in Wireless Sensor Networks

Wireless sensor networks have become an important area of research in recent years. A wireless sensor network (WSN) consists of a number of tiny devices with sensors to sense some parameters such as temperature, motion etc. A sensor has limited computation power, ability to communicate with nearby sensors, and limited battery power. Each sensor has a sensing range within which it can sense the parameter, and a communication range over which it can communicate with other sensors. The sensor nodes form an ad-hoc network capable of sending the sensed data to base stations for further processing. Sensor networks have been used in different applications such as habitat monitoring, intruder detection, target tracking etc. The challenges in designing protocols for wireless sensor networks usually stem from the limited resources (processing power, transmission bandwidth, memory, battery, etc.) available to each node. Most solutions requiring centralized processing or global information are likely to be wasteful for wireless sensor networks.

Geometric algorithms are used in different areas of sensor networks such as localization, topology control, coverage etc. Localization is the technique by which sensors can find their own coordinates in some coordinate system. Topology control is a technique by which sensors form and maintain network connectivity with certain desired properties. Coverage defines the quality of surveillance provided by the sensor network. We are working on the problem of coverage in sensor networks where a target region is to be covered by a set of sensors. There exist various definitions of coverage depending upon the application, such as area coverage, breach, support, barrier coverage etc. We are currently working on two problems related to coverage in sensor networks, as described next.

Let  $X = \{s_1, s_2, ..., s_N\}$  denote a set of N sensors, A denote a region of interest,  $P = \{p_1, p_2, ..., p_N\}$  denote the position of the sensors, and  $d(p_i, p_j)$  denote the Euclidean distance between  $p_i$  and  $p_j$ . Given two points  $i = (x_i, y_i), f = (x_i, y_j)$  in A, the support value  $\psi_p$  of a path P between i and f is the maximum distance of any point in P from its closest sensor. Formally,  $\psi_p = max_{p \in P} (min_{s_i \in X} d(p, s_i))$ . The maximal support path  $P_{max}$  between the pair of points (i, f) is a path whose support value is minimum among all paths between i and f. A path with a good support value is desirable

as it provides good coverage to an entity traveling along the path. In our first work, we focus on maintaining the support value of a path within some acceptable range on failure of sensors.

On failure of a sensor, the support maintenance algorithms try to move a small number of other sensors locally to establish a new path with an *acceptable* support value. We have presented two centralized approximation algorithms for support maintenance. The first algorithm allows the sensors to move in any arbitrary direction. The second algorithm allows the sensors to move only in one of the four directions - north, south, east, and west; the direction to move is chosen once and not changed after that. Support maintenance is actually a combination of two algorithms - an initialization algorithm that is called only once at the beginning to compute the maximal support path, and a maintenance algorithm that is called whenever the failure of a sensor is detected. The aim of the algorithm is to maintain a path with an acceptable support value. At each failure, the second algorithm establishes a new support path with support value close to that of the old support path by migrating a single sensor to a new location. Note that the new support path may not be the maximal support path corresponding to the final positions of the sensors. So far we have implemented the centralized as well as the distributed versions of the algorithms. We have shown that after the initialization phase, the support value of the maximal support path may change only if some sensor in the maximal support path fails. We have also shown that the new support value of the modified path after the first failure from the maximal support path is a constant factor approximation of the initial maximal support value. The amount of displacement of the sensor moved is also a constant factor approximation of initial support value. We have performed detailed experiments to evaluate the algorithm and shown that the actual performance of the algorithm is much better than the bounds given by the approximation factor.

In our second work we have defined a new type of coverage called *line coverage*. A line segment *l* is said to be *k*-covered if it is within the sensing range of at least *k* sensors. The input to this problem is a set of line segments  $L = \{l_{i}, l_{2}, ..., l_{N}\}$  and an initial deployment of a set of sensors  $X = \{s_{1}, s_{2}, ..., s_{M}\}$ . The problem is to *k*-cover all the line segments by moving a minimum number of sensors to some new locations. To solve this problem, we are evaluating the minimum number of sensors required to *k*-cover the lines in *L*. If the number of sensors required is less than or equal to *M*, then there exists a rearrangement. Initially, we are focusing on finding the minimum number of sensors to *k*-cover the lines in *L* are account of finding the minimum number of sensors to *k*-cover all the line segments in *L* is *NP*-hard. We have also designed a constant factor approximation algorithm for a special case of the problem when all the line segments in *L* are axis parallel. We are now working on the design and evaluation of good heuristic solutions to solve this problem.

Joydeep Chandra

Joydeep Chandra completed B.Tech (Computer Science and Engineering) from Haldia Institute of Technology, India in 2000 and M.Tech (Computer Science & Engineering) from Indian Institute if Technology, Kharagpur in 2002. From March 2002 till April 2008, he worked as lecturer in SLIET, Punjab and in Punjab Engineering College, Chandigarh. Since May 2008, he has been a research scholar at Indian Institute of Technology, Kharagpur. His research interests include p2p networks, distributed algorithms and complex networks. His website is http://joydeep.chandra.googlepages.com

Supervisor: Prof. Niloy Ganguly

# **Dissecting Peer-to-Peer Topologies Using Complex Network Theory**

The enormous popularity of p2p applications - due to certain inherent benefits like, ability to share large contents directly from personal devices, enhanced scalability and robustness - has led to the formation of a pool of vast information and digital contents with entirely distributed set of entities and resources. However, to maintain the effectiveness of these networks, i.e. provide good quality of service, search performance, scalability and robustness, certain major issues need to be considered.

- 1. A major issue is the overlay or topology formation, the major objective being to obtain required contents with low bandwidth consumption. Since, there has been an unbridled growth in the p2p traffic and the ISP's are already facing huge problem of bandwidth and congestion, hence topology management has already become a major issue. An improper topology can increase p2p traffic at the ISP gateways. Moreover topologies also determine the robustness of the network, as an improper topology is susceptible to breakdown during network churn.

- 2. Another important issue that determines network efficiency is the search performance; because of the distributed nature of these networks, developing suitable search mechanisms is a big challenge. In p2p networks, many resources might be present that lack suitable computation power, hence we cannot implement search strategies that are computation intensive. Hence a major challenge is to implement simple and efficient search strategies.

Although, apart from these issues, there are certain other important issues like, service discovery, indexing and replication, and security that are being considered; however, the focus of my research is centered on improving performance like search, bandwidth wastage and bottleneck in heterogeneous p2p networks through better topology management schemes. In our approach, we would initially attempt to gain insight into the existing super-peer based network topologies like Gnutella, Kazaa etc. and analyze the effects of these topologies on the above stated parameters through suitable analytical models. Much of these models are influenced by the recent developments, in classical

physics, of network-theoretic models for analyzing the dynamics of large networks, typically termed as Complex Networks. These models help us to predict the behavior of the network under given conditions of growth and topology formation; further, these also provide directions to modify these topology formation mechanisms so as to improve the behavior of the network in terms of the above stated parameters. Hence, based on these findings we would attempt to propose suitable topology optimization mechanisms and validate their improvement in performance using simulations.

In this direction, we have initially studied the impact of topology on coverage and traffic redundancy in unstructured p2p networks that use flooding as the underlying search mechanism. In our work, based on models by Newman et al. [1] for finding neighbor distribution in large networks with given arbitrary degree distribution, we initially build up a basic analytical model to obtain probabilistic bounds on the network coverage of the peers in p2p networks that use TTL(2) (numeric value inside parenthesis represents the number of hops to search with) based search and query mechanisms. We limit our study to TTL(2) based networks, as search and query in popular networks like Gnutella mostly use TTL(2). However, our models and results can easily be generalized for TTL(n) searches as well. We observed that the basic model makes a simplified assumption that the underlying topology is tree-like; in contrast real networks contain certain cycle forming edges, which we referred as back and cross edges. We perform a rigorous analysis of bounds assuming the presence of back/cross edges. It is observed that the number of back/cross edges upon a node depend on its current degree. Based on this observation, we derive models to estimate the back/cross edge probabilities of the peers, with respect to their degrees, for random networks with any arbitrary degree distribution. The proposed refinement thus derives the TTL(2) network coverage of the peers with respect to their current degree. The accuracy of the models is validated on several types of networks, like Erdos Renyi networks, scale-free networks and also on a simulated Gnutella network, using extensive simulations. We further generalize the concept of back and cross edges for any TTL values and derive the TTL(n) network coverage of the peers in the network. The results indicate that the probability of occurrence of these edges increases enormously with increasing distance from the source nodes, which can result in huge traffic redundancy, thus questioning the effectiveness of larger TTL based search.

Based on these findings, we propose a modified bootstrap protocol for Gnutella networks, named HPC5 that avoids the formation of these back and cross edges. We analyze the performance of the proposed protocol and compare the same with an existing topology optimization mechanism named DCMP using simulations. The simulation results reflect that the proposed bootstrap protocol improves network coverage and reduces message complexity and traffic redundancy in Gnutella.

#### **References:**

1. M. E. Newman, S. H. Strogatz, and D. J. Watts. Random Graphs with Arbitrary Degree Distributions and Their Applications. Phys Rev E Stat Nonlin Soft Matter Phys, 64(2 Pt 2), August 2001.

Kamalesh Ghosh

Email: kghosh@cse.iitkgp.ernet.in

Kamalesh Ghosh received a B.Tech. (Hons) degree in Computer Science and Engineering from IIT Kharagpur in 1998. From July 1998 to April 1999 he worked as a software engineer with Wipro Infotech Ltd. (Bangalore) on e-commerce products. From April 1999 to Dec 2000, he worked as a senior software engineer in Delsoft India Pvt. Ltd. (Noida) on Electronic Design Automation (EDA) software. From Jan 2001 to Oct 2004 he worked as senior R&D engineer at Synopsys Inc. (Marlboro, MA) on verification tools for VLSI design. From Nov 2004 to Nov 2007 he worked at Synopsys India Pvt. Ltd. (Bangalore) as senior R&D Engineer, continuing in the same area of work. From Dec. 2007 till now, he has been working as a Research Consultant in the department of Computer Science and Engineering at IIT Kharagpur, pursuing a Ph.D. degree simultaneously. His research interests are in the area of Artificial Intelligence and Formal Verification with particular focus on application to component based design of safety critical real-time systems.

#### Supervisor: Prof. Pallab Dasgupta

# Formal Methods for Top Down Component Based Development

Component based Software Engineering (CBSE) is a very popular paradigm in modern software engineering. The CBSE approach focuses on building software systems with commercial-off-the-shelf (COTS) components or existing in-house components rather than ground-up development. When safety critical systems with real-time requirements (e.g. automotive) are built using this paradigm, sources of failures can be many. For example - the timing and logical properties of the built system are inherently difficult to predict or verify. Our work is focused on finding novel techniques that may help in closing some of these sources of failure.

To give a proper definition to our task, we visualize three abstract layers across which the design and implementation of the system is distributed. The topmost layer is named the Feature Layer in which the requirements of the built system are captured from a user's perspective. This layer is the most idyllic view of the system which will just list desirable features and have no connection to lower level concerns. The second layer, named Interaction Layer, is a cluster of various "subsystems" which coalesce together to build up the system. Each "subsystem" may be thought of as a component in our CBSD paradigm, which is being bought as a COTS component or developed independently in-house by the manufacturer, e.g. the braking subsystem or the powertrain subsystem for a car. Though this layer is still not giving a complete picture of the working of the whole system, it is more grounded towards reality and detailed. The lowermost layer, called the Component Layer, is where the real implementation is captured. This layer takes into account all the implementation details - like the actual hardware platform and physical interconnection -- into account. This 3-layer visualization mimics the phases in the design of a real-life system quite realistically. Based on the above framework, we define some point problems which are inherently interesting, challenging and potentially useful in producing a whole solution eventually.

In our first problem, the interaction layer specifications are formally written as sets of preconditions and postconditions. Each precondition-postcondition pair is called an action and either defines what the controller must do when the preconditions hold or defines what the environment (driver, road etc.) may do if it chooses to. In the former case the actions are called control actions while in the latter case we call them environment actions. Thus our formalism includes the operational environment and control specification of the system as its core elements. The feature layer is simply modeled (for now) as a set of logical statements which indicate desired properties (checks) for the system. The control should never allow any of these to be violated (intermittent violations are allowed, but the control should never allow the system to sustain such a violated state). We model the environment and control as two adversaries in a game-like scenario. The environment makes moves to violate a property representing a vehicle feature requirement, while the control interrupts at every move of the environment and executes pre-specified actions. The property is verified if the environment has no winning strategy. This model allows us to do a logical evaluation of the software control logic at a stage when few low level details are available. The benefit of this analysis is that we may detect "logic bombs" at a very early stage of design.

In our second problem, building up on the same formalism above we aim to catch contradictions or inconsistencies in the specification through automatic detection of loops consisting of control actions. Loops in the high level specification of a control naturally arouse suspicion as it can be indicative of contradictions. We have demonstrated this point through examples in our related paper.

Further building up on the work done till now we are looking at methods to expand the semantics of our formalism to consider loops in a more realistic manner. We assumed in the above problem that loops in control are indicative of an inconsistency. In reality, this need not be the case. For example, many automotive features may require components to continuously interact with each other till a particular event happens in the environment. This can naturally lead to loops in the control action definitions. We are exploring further enhancements to our existing semantics in order to consider these loops in a smart and realistic way. This work requires us to define new semantics and devise new algorithms.

Specifications for real-time reactive systems often need to refer to numerical value of physical quantities such as speed, acceleration etc. Any formalism without this basic expressive power may be considered too limited for practical use. However, allowing for expressions with numerical variables under standard operations like addition, multiplication etc. often causes the verification problem to become undecidable. Our future research will explore limited enhancements in expressive power in the numeric domain to find a good tradeoff between expressive power and ease of verification.

This research is supported by a grant from General Motors under the GM-IITKGP Collaborative Research Lab.

# Maunendra Sankar Desarkar

Maunendra Sankar Desarkar received B.E. degree in Computer Science and Engineering from the University of Burdwan in 2004, and M.Tech. degree in Computer Science and Engineering from Indian Institute of Technology Kanpur in 2006. From July 2006 till July 2008, he worked for Sybase India Pvt. Ltd. as a Software Developer. Since July 2008, he has been a research scholar in the department of Computer Science and Engineering in IIT Kharagpur. He was awarded the Microsoft Research India PhD Fellowship in 2009. His research interests are in the areas of Data Mining and Information Retrieval.

Supervisor: Prof. Sudeshna Sarkar

# **Aggregation of Rankings and Ratings in Information Retrieval Applications**

Several problems in web domain require aggregation of opinions obtained from multiple sources. The opinions can be human or system generated. System generated opinions can be outputs for the same problem obtained by employing different algorithms, for example, rankings of documents by search engines, scoring of documents or objects based on multiple features etc. Human generated opinions include ratings assigned to movies/news/products by users, free text reviews in blogs, forum etc. We tried to focus on the problems of meta-search and collaborative recommendation, two applications which require aggregation of opinions.

The number of pages in the web has increased manifold in the recent years. The contents have become richer, and also the linkage pattern between pages has changed a lot. The changes are posing major challenges to the Information Retrieval problems that work on web data. For web search, which is one of the most widely used Information Retrieval applications, the problem is more severe as it is inherently difficult for the search engines to capture the user intent and the context of the documents. Under the circumstances, it might be helpful to combine the outputs of multiple search engines for getting the final output to be displayed to the user.

Meta-search engines are special kind of search engines that take help of other search engines for producing search results. Upon receiving a query from a user, it passes the query to multiple other search engines and obtains the search results from them. The search results are given in the form of ranked list of documents. The meta-search engine combines these ranked lists to generate an aggregated ranked list. This ranked list is then displayed to the user. The first problem that we tried to address is the Rank aggregation problem, where the task is to aggregate the ranked lists obtained from multiple different sources. The problem has applications in text mining as well, where documents are scored based on multiple features or criteria. For each criterion, the documents in consideration can be ordered in the form of a list. The final ordering of the documents can be constructed by combining the lists obtained for the individual criteria or features.

We propose a two-phase approach for solving the rank aggregation problem. Each ranklist is represented by a preference graph. The first phase of our algorithm assigns weights to the input ranklists. We want to assign higher weights to better rankers, so that poor rankers do not have much influence on the aggregated result. The input preference graphs are combined to produce a weighted aggregate preference graph. The second phase of the algorithm induces a linear ordering from this aggregate preference graph. We have tested our algorithm on synthetic data. Currently we are in the process of evaluating the algorithm on a benchmark dataset.

Another problem that we are simultaneously working on is related to collaborative recommender systems. The web has evolved into a platform where users can share their thoughts and discuss ideas. Introduction of e-commerce services and sharing of customer experiences through product review sites or even personal blogs are providing the potential customers with a huge pool of information. Since the judgments are provided as a conscious effort to let the other users know about the experiences of the customer/reviewer/author, these are extremely valuable sources of information. However, the sheer size of such data often makes it difficult for an individual to draw any meaningful conclusion out of it. Systems able to aggregate such opinions can be immensely beneficial to the users.

Recommender systems aim to solve this problem of information overload by presenting the users a small subset of products that he might be interested in. Effective recommendation helps both sides of the business, the customer as well as the merchant, and has emerged as an important research area. Users in recommender systems often express their opinions about different items by rating them on a fixed rating scale. The rating scale can have two categories - like/dislike, or multiple categories where higher categories denote higher level of user satisfaction. Primary task of such recommender systems is to predict the rating that a user would give to an item he has not rated yet. Based on the assumption that users with similar tastes rate items similarly, collaborative recommendation systems first find a group of users having similar interests. Opinions of the users from that group are used to predict the unknown rating. We have proposed a memory-based collaborative filtering approach that uses preference relations between items instead of absolute ratings.

Use of preference relations allows the rating of an item to be influenced by other items. This is in contrast with weighted-average approaches of the existing techniques. This is certainly desirable, especially when the data is sparse. We carried out experiments with sparse data to verify this claim. The step for finding similar users requires assigning similarity weights to the users. Possible extensions of the work may be to update the similarity weights dynamically as new ratings are added to the rating database, or to try different similarity measures for determining the similarity weights.

# Plaban Kumar Bhowmick

**Plaban Kumar Bhowmick** received BTech degree in computer science and engineering from University of Calcutta in 2002 and the MS degree in computer science from Indian Institute of Technology, Kharagpur in 2006. He is currently a research scholar in the Department of Computer Science & Engineering, IIT Kharagpur. His research interests include natural language processing, information retrieval, information and communication technology.

Supervisors: Prof. Anupam Basu and Prof. Pabitra Mitra

# **Reader Perspective Emotion Analysis of Text in Multi-Label Classification Framework**

The Internet has been one of the primary media for information dissemination after the advent of Word Wide Web. The advent of new technologies makes way of new interaction possibilities and provides people to perform different social activities on platforms like blog, chat, social network, news etc. As compared to traditional keyword based or topical access to the information, social interactions require the information to be analyzed in social and humanistic dimensions like emotion, sentiment, attitude, belief etc.

Opinion mining or sentiment analysis focuses on investigating the views of the users towards a particular entity. This task judges the entity in the dimension of positivity or negativity, i.e., whether a particular movie is liked by the users or not. In contrast to sentiment analysis, emotion recognition goes beyond positive-negative dimension to discrete emotion categories like happiness, disgust etc.

Expression or change of behavior is the most visible and prominent clues for recognizing emotion. Facial expressions, speech expressions have widely been used in detecting emotion. Emotion is not a linguistic entity. However, language is one of the most common modes for expressing emotion whether it is day-to-day speech communications (spoken language) or published communications (written language). Emotion can be studied from two perspectives.

- a) From the writer/speaker perspective, where we need to understand the emotion that the writer/speaker intended to communicate and

- b) from the reader's perspective, where we try to identify the emotion that is triggered in a reader in response to a language stimulus.

In this work, we intend to perform sentence level emotion recognition from a reader's perspective. The challenges included in this task are as follows.

• Data Preparation: Appropriate data set for emotion analysis is to be collected and annotated by human judges with proper annotation scheme.

- Corpus Reliability: As Emotion is a subjective entity, the emotion tagging may vary with judges. So, annotation by multiple judges may be required to test the reliability of the corpus before using it as a gold standard in classification task.

- Multi-Label Characteristics: On encountering a sentence as stimulus, a blend of multiple emotions can be triggered in a reader. For example, the following sentence may evoke fear and sad emotion in readers mind.

#### Militant attack kills over 30 persons in Nigeria.

Hence, a sentence may be labeled with multiple emotions from the reader's perspective.

- Feature: Since research on emotion elicitation from text is in its infancy, the appropriate feature set required for emotion elicitation needs investigation.

- Sparseness of features: While emotion elicitation from a discourse or paragraph may provide larger number of cues as features, the number of features available from a single sentence is less and hence the feature space becomes sparse.

The emotion text data collected by us consists of 1350 sentences extracted from Times of India news paper archive. The sentences were collected from headlines as well as from the bodies of articles belonging to political, social, sports and entertainment domain. The corpus has been annotated by five human judges. The annotation scheme considers fuzzy annotation. Two different measures have been formulated in order to compute agreement among the annotators. The crisp reliability measure considers crisp belongingness of a sentence in an emotion category whereas the fuzzy agreement measure considers fuzzy belongingness. Gold standard data sets have been prepared by aggregating the views of all the annotators. As each sentence may evoke multiple emotions simultaneously, multilabel classification frameworks have been used to classify sentences into emotion categories. Multi-label k Nearest Neighbor and Random k Label Set algorithms have been provided. Four different types of features have been considered, namely, word occurrence, polarity (subject, object and verb phrase), semantic frame, emotion elicitation context. The same set of features has been considered for developing fuzzy classification model with Fuzzy k Nearest Neighbor algorithm.

Priyankar Ghosh

**Priyankar Ghosh** received B.E. degree in Computer Science & Engineering from Jadavpur University, Kolkata, in 2003 and M.Tech degree in Computer Science & Engineering from Indian Institute of Technology Kharagpur, in 2006. He also has industry experience of approximate two years. Since April 2007, he has been a research scholar in the Department of Computer Science & Engineering in Indian Institute of Technology Kharagpur. His research interests are in the areas of Verification, Artificial Intelligence and Knowledge Representations and Interoperability among them.

Supervisors: Prof. Pallab Dasgupta and Prof. P. P. Chakrabarti

# Formal Methods for Planning and Verification of Integrated Semantic Web Services

With the recent advances in internet technology, Service Oriented Architectures (SOA) have gained widespread acceptance. Typically web services that implement SOA, represent functionalities that are offered by some organizations in the web. These functionalities can be accessed through internet by some client, which may be an individual or an organization. Web services resemble remote procedure calls, which are accessed using HTTP/ HTTPS protocol.

The web service requester does not need to know about any implementation details of the web service provider. Therefore the interoperability among different organizations increases greatly. Web services are published, described, and accessed by certain machine processable descriptions developed on top of XML. Moreover existing web services can be combined in a loosely coupled fashion to develop complex applications.

Semantic web is an ongoing extension of traditional web where the semantics of the service is defined. The main goal of semantic web is to enable the machine to interpret this information. Semantic web services are a component of the semantic web activity where machine-readable markups are used to describe a service. The objective of semantic web services is to automate the discovery and invocation of the services.

Since the origin of the World Wide Web, the development and growth of web services has taken place typically in an uncoordinated and unstructured way. Consequently the protocols followed by different web services are vastly different, not only in terms of the protocol structure but also in terms of the semantic interpretation of the data they exchange. This makes the task of developing applications which automatically interact with multiple web services, a significantly challenging task.

In the current work we study modeling techniques and investigate the usage of the high level semantic models for solving the following problems.

- Usage of High Level Model in Protocol Verification: Web service providers typically publish a high level model of the service to describe the behavior of the web service. Typically these models are written in English language and may have some graphical representation as well. In this work our goal is to formalize the model, and generate a set of test cases using the model in order to verify the correctness of the implementation. These test cases will include positive as well as negative test cases. This published model is also used during the integration with the client. During the integration with the server, the client side writes test cases to check the protocol compliance. Diagnosing the reason of the mismatch in message exchange between the client and the server plays a crucial role in debugging the client applications. Our goal is to develop and formalize a debug mode based testing methodology which will assist the client to detect reason of interaction failure during the integration with server and provide useful information regarding the test cases developed by the client.

- Modeling Semantic Information Exchange and Detecting Conflicts: Interaction between the client and the server may also fail due to the difference in the interpretation of the exchanged data. The semantics of data play a major role in semantic web services which goes beyond simple type checking. Therefore the protocol that defines the interaction has to be verified in order to check the presence of semantic conflict. It is possible that the knowledge base of the server has some conflict with the knowledge base of the client, but the protocol does not sensitize the conflict.

- Planning Based Approach to Compose Web Services: It is quite common to use multiple web services in order to achieve a goal. Since the overall goal may be achieved only when these web services are invoked in a particular order, it is often needed to undo the effect of one service. For example hotel reservation may be cancelled due to the unavailability of flight booking. However these cancellations may incur penalty. Moreover alternative web services may be available for the same goal. For a given goal, the objective is to find out a schedule of invoking the web services so that the penalty in this schedule is minimized.

This research is partially supported by a research grant from Google.

Rajarshi Pal

**Rajarshi Pal** received a B. Tech. degree in Information Technology from Kalyani Govt. Engineering College in 2004, and an *M. Tech. degree in Software Engineering from Jadavpur University in 2006. Since July 2006, he has been a research scholar in the Department of Computer Science & Engineering in IIT Kharagpur. His research interest is in the area of Computer Vision.*

#### Supervisors: Prof. Jayanta Mukhopadhyay and Prof. Pabitra Mitra

## **Modeling Visual Attention for Image**

Machine vision tasks enable the computer to understand what it "sees". Hence, any machine vision based task that works with images needs to analyze the captured image. Often the next step of processing is determined by this analysis or understanding of the image. As still now computers are much slower compared to primate brain, they take a lot of time to analyze the captured media. Instead of analyzing the whole image, if analysis from some selected portions of it gives comparable result, then computational time is saved. The concern is which portions of the image will be analyzed and which portions will be ignored. Obviously, in order to be not distorted from the analytical result, important portions of the image have to be analyzed. Here comes the urge of deriving a computational model that conveys to the machine about the important portions of the image. In other words, the model will direct the machine to attend the selected portions, like the primates do.

Without doubt, primates are remarkably faster to comprehend and analyze visual scenes in real time. It is observed that in a time interval that is short enough to comprehend the whole scene, primates tend to attend some selected areas or objects that can be easily distinguished (salient) from a cloud of other objects. In order to perform computer vision based tasks faster, researchers in this field are trying to mimic primate vision.

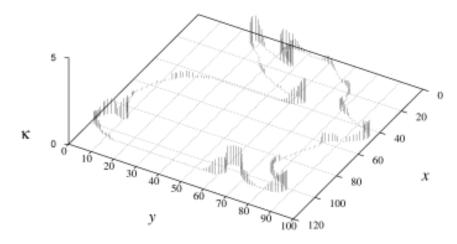

A complex network based approach is adopted to determine the visually salient locations in the image. A network is constructed where nodes represent accumulation of similar pixels and the dissimilarity between any pair of such accumulations is encoded as edge-weight between the corresponding nodes. Dissimilarity is in terms of features modulated by their positional proximity. Modulation by positional proximity ensures that difference with neighboring locations gets more weightage. Such networks are constructed over multiple features (color, intensity and orientation) across multiple scale representation of the image. Certain location is salient if it is dissimilar from all other locations and specially, with its surroundings. The network, termed as ViSaNet (Visual Saliency Network), constructed here is a suitable choice for determining salient locations as it combines both local and global conspicuity of a location. Incorporation of degree centrality analysis with this type of network suggests that a centrally situated node belongs to a salient location. Potential of other node centrality measures (eigenvector, closeness, and betweenness) to model saliency of an image is also studied.

Selection of appropriate features is an important task in computer vision problems. It reduces the computational burden and improves the end result. Important features for visual saliency models are identified by estimating the amount of errors contributed by them. Analysis for monochrome and color images is carried out separately. Experimental results suggest that selection of appropriate features improves the model's performance. Principal component analysis (PCA) on selected features is also performed. Usage of only the first principal component as potential feature in degree centrality based saliency computation performs better than well-known saliency models.

Evaluation is a key part while proposing a new model. To evaluate models of visual saliency, one needs to compare the model's output with salient locations in an image. An approach to find out the salient locations, i.e., ground truth for experiments with visual saliency models, is derived purely based on human hand-eye coordination. It is found that the proposed technique can be an alternative to costly human pupil-tracking based systems. Moreover, an evaluation metric is also proposed that suits the necessity of the saliency models.

Red, orange and yellow are termed as warm colors. Role of warm colors on visual saliency is studied. Distributions of chromatic features (hue and saturation) are found to be different for warm colors that draw attention and those that do not. It is also observed that likelihood of drawing attention by a warm color depends on both of its hue and saturation component. Interestingly, this dependency is not related to the absolute hue and saturation, but relative to these chromatic components of other warm color pixels. Warm colors with hue relatively closer to red and/or with high saturation are more likely to guide attention.

So far, various issues related to modeling of visual saliency have been discussed. Beside the works that tune up model of saliency step-by-step towards perfection, we have also worked in a few application areas of visual saliency.

Image downsizing to show it in a small display reduces recognizability of the image. The standard practice is to crop around the important locations and display the cropped portion only. A cropping algorithm has been proposed that uses localized thresholding to retain the overall subject matter of the image. This method also does aspect ratio adjustments to prevent any distortion due to mismatch in aspect ratio of the cropped portion and that of the display.

Continuous inventions of modern cameras are making the act of good photography easier. We have proposed a methodology that makes a camera even smarter by converting the objects of interest to the photographer more salient. This results in maximization of viewers' attention on intended objects. The captured photo can be taken as a media of communicating photographer's mind to the potential viewers. In that sense, the proposed methodology reduces the communication gap between them.

Rajiv Ranjan Suman

**Rajiv Ranjan Suman** received a B.E. degree in Computer Science & Engineering from Birsa Institute of Technology, Sindri, Dhanbad (Jharkhand) in 1991, and an M.Tech. degree in Computer and Information Technology from IIT Kharagpur in 2002. From Mar 1992 to Dec 1995, he worked in BIT Sindri as a part-time Lecturer. From Jan 1996 to till date, he has been working as a Lecturer in the department of Computer Science & Engineering at NIT Jamshedpur. In July 2007, he joined the department of Computer Science & Engineering, as a research scholar as a sponsored candidate under QIP scheme. His research interests are in the areas of Software Engineering.

Supervisor: Prof. R. Mall

# **Construction of State Model of Software Components**

We propose a novel black-box approach to reverse engineer state models of software components. We assume that in di erent states, a component supports di erent subsets of its services and that the state of the component changes solely due to invocation of its services. To construct the state model of a component, we track the changes (if any) to its supported services that occur after invoking various services. Case studies carried out by us show that our approach generates state models with sufficient accuracy and completeness for components with services that either require no input data parameters or require parameters with small set of values.

In component-based software development paradigm, a large software is built by assembling pre-built and independently developed "plug and play" type of executable units, called software components. Components are usually integrated to applications through an application program interface (API). Only a brief description of the functionality of a component is provided by the component vendor. Developers of the component-based software have to rely on vendor's capability and inadequate documentation available regarding correctness of the functionality and quality of the components. However, developers of critical applications cannot risk using components of incorrect functionality and they need to ensure that the components are trustworthy and would function as per the expectation. In addition to validating the functional behavior, dynamic behavior of the components need to be validated.