## AMBA APB – Case Study

#### Testing & Verification Dept. of Computer Science & Engg, IIT Kharagpur

#### Pallab Dasgupta

Professor, Dept. of Computer Science & Engg., Professor-in-charge, AVLSI Design Lab, Indian Institute of Technology Kharagpur

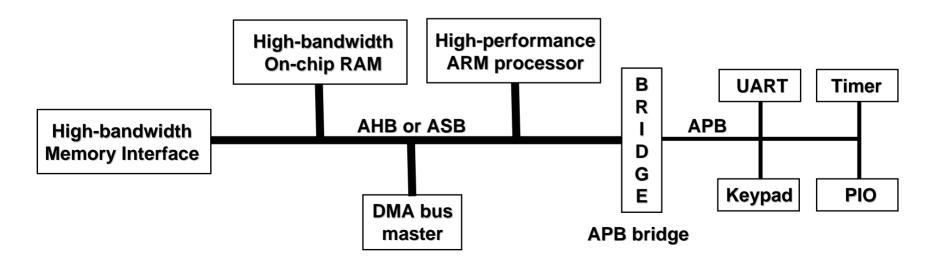

#### **Advanced Microcontroller Bus Architecture (AMBA)**

Defines an on-chip communications standard for designing highperformance embedded microcontrollers

#### □ Three Components:

- Advanced High-performance Bus (AHB)

- Advanced System Bus (ASB)

- Advanced Peripheral Bus (APB)

#### © Pallab Dasgupta, Dept. of Computer Sc & Engg, IIT Kharagpur

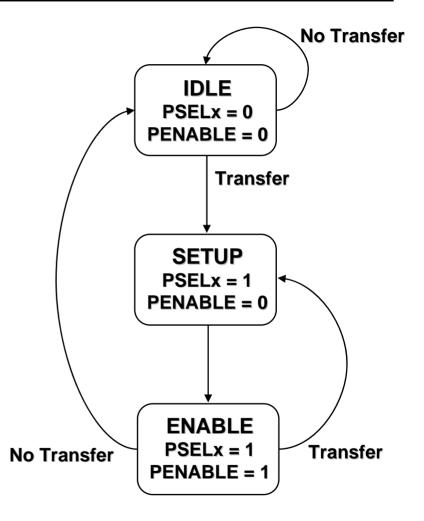

### **APB & Its State Diagram**

APB is used to interface to any peripherals which are of low bandwidth and do not require high performance of pipelined bus interface

#### □ Salient Features:

- Low power consumption

- Reduced interface complexity

- Latched address & control

- Suitable for many peripherals

#### **APB State Diagram**

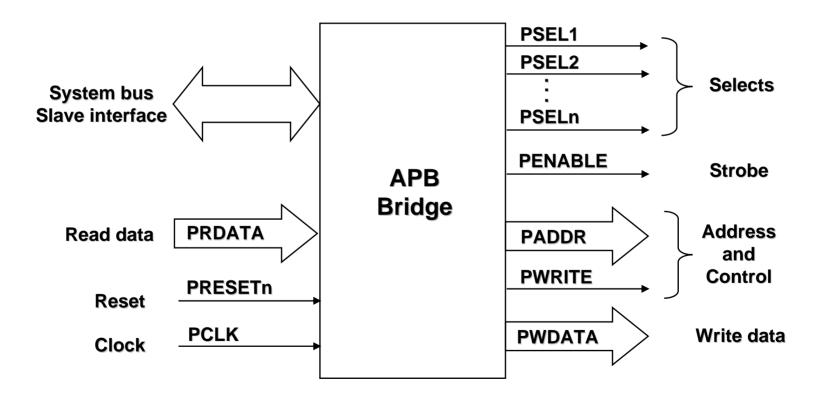

### **APB Bridge Interface**

□ APB bridge is the only bus master on the AMBA APB.

□ APB bridge is also a slave on the higher-level system bus.

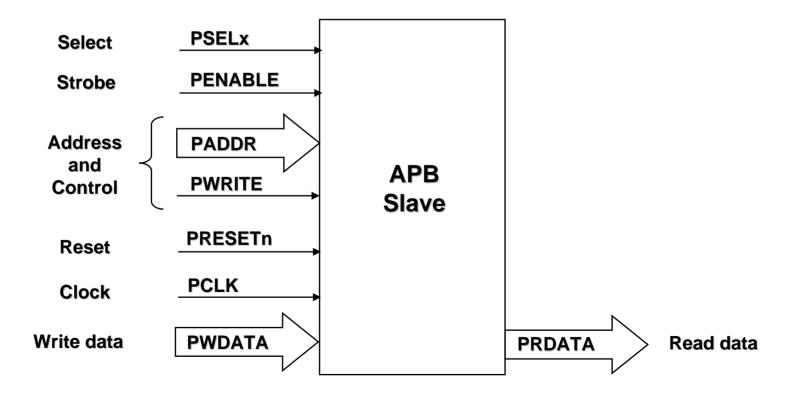

### **APB Slave Interface**

□ APB slaves have a simple, yet flexible, interface.

Exact implementation of the interface will be dependent on the design style employed and many different options are possible.

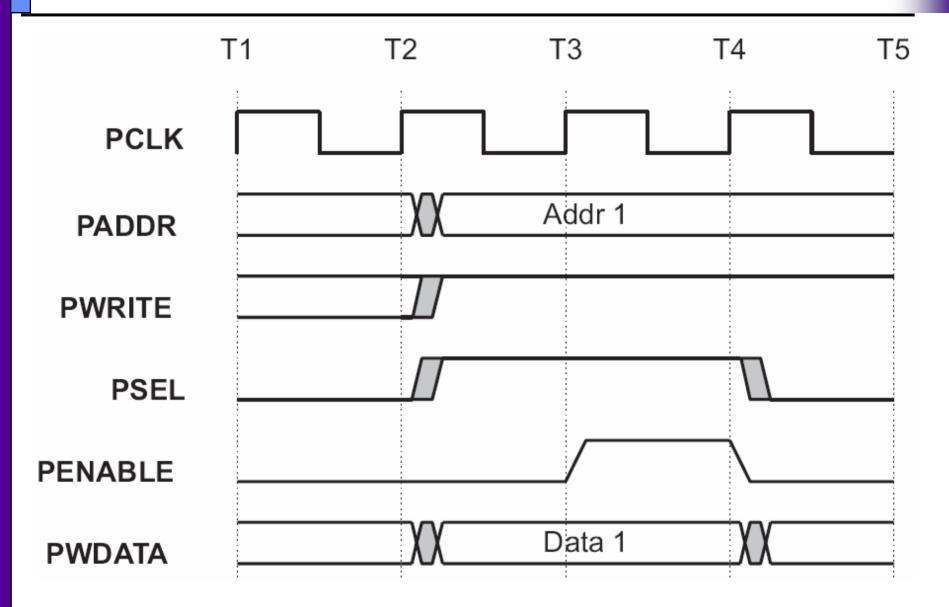

### **APB Write Transfer**

© Pallab Dasgupta, Dept. of Computer Sc & Engg, IIT Kharagpur

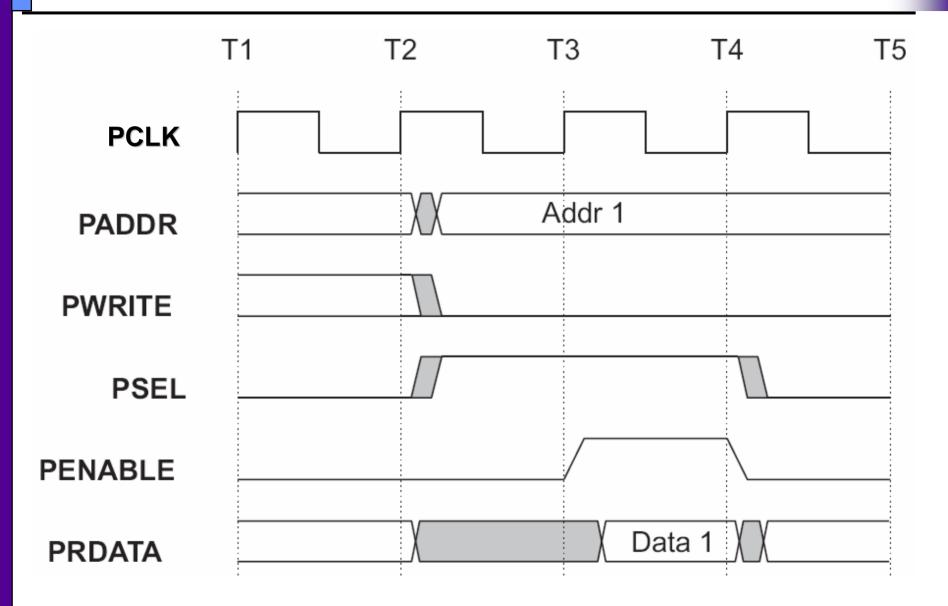

### **APB Read Transfer**

© Pallab Dasgupta, Dept. of Computer Sc & Engg, IIT Kharagpur

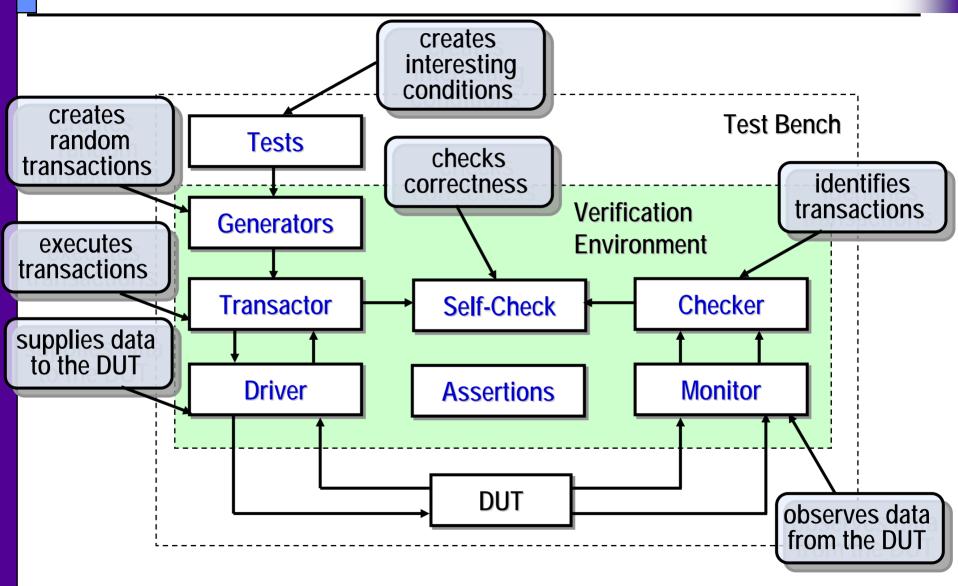

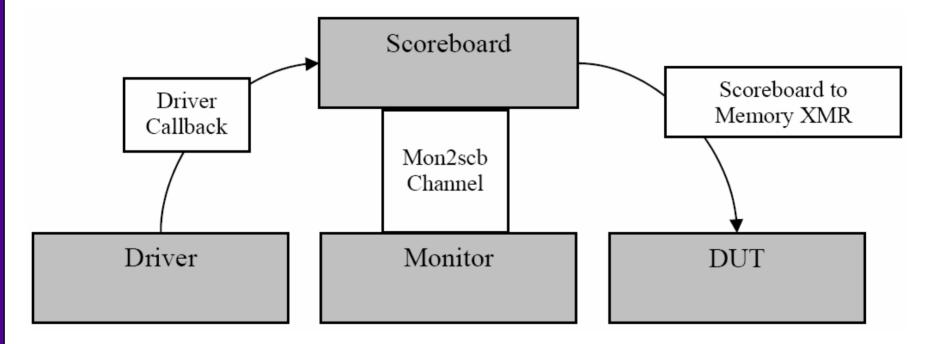

### **Layered Random Test Architecture**

### **Environment Setup & Execute**

- Top-level test bench instantiates the DUT environment, builds it and runs all steps in layered architecture by executing this environment

- □ The test environment structure is as follows:

### **Components of Environment**

#### □ Test bench Top-level components include:

- APB Atomic Generator

- APB Master

- APB Monitor

- Scoreboard

#### **Overall Execution Flow**

© Pallab Dasgupta, Dept. of Computer Sc & Engg, IIT Kharagpur

### **Signal Layer**

#### □ Specifies DUT interface signals

```

interface apb_if(input PClk);

logic [`APB_ADDR_WIDTH-1:0] PAddr;

logic PSel;

logic [`APB_DATA_WIDTH-1:0] PWData;

logic [`APB_DATA_WIDTH-1:0] PRData;

logic PEnable;

logic PWrite;

logic Rst;

/* master & monitor clocking blocks */

```

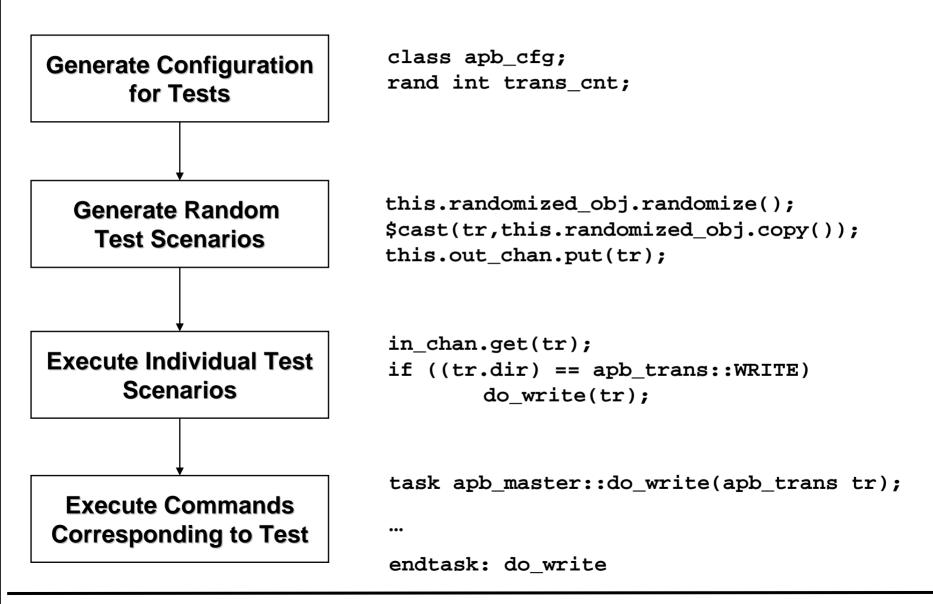

### **Command Layer**

APB master implements driver routines named do\_read(), do\_write() and do\_idle()

task apb\_master::do\_write(apb\_trans tr);

// Drive Control bus

`APB\_MASTER\_IF.PAddr <= tr.addr;

`APB\_MASTER\_IF.PWData <= tr.data;

`APB\_MASTER\_IF.PWrite <= 1'b1;

`APB\_MASTER\_IF.PSel <= 1'b1;</pre>

// Assert Penable

##1 `APB\_MASTER\_IF.PEnable <= 1'b1;

// Deassert it

##1 `APB\_MASTER\_IF.PEnable <= 1'b0;

endtask: do write</pre>

#### **Functional Layer**

Functional layer (APB master) receives the transaction generated by the scenario layer from the channel.

```

apb_trans tr;

in_chan.get(tr);

case (tr.dir)

apb_trans::READ: do_read(tr);

apb_trans::WRITE: do_write(tr);

default: do_idle();

endcase

```

### **Scenario Layer**

Scenario layer (APB atomic generator) creates individual transaction object & sends to the functional layer through channel

```

apb_trans tr;

```

```

apb_trans_atomic_gen::new(...);

```

```

this.addr = 0; this.data = 0; this.dir=IDLE;

```

```

endfunction:new

```

```

apb_trans_atomic_gen::main(...);

```

this.randomized\_obj.randomize();

```

$cast(tr, this.randomized_obj.copy());

```

this.out\_chan.put(tr);

```

endfunction:main

```

#### **Test Layer**

env creates an object of apb\_cfg which contains the configuration for the tests for APB VIP

```

class apb cfg;

rand int trans cnt;

constraint basic {

trans cnt > 5;

trans_cnt < 10;</pre>

endclass: apb cfg

apb cfg cfg;

cfg.randomize();

```

#### **Monitor Execution Flow**

### **Functional Layer (Monitor)**

- dut\_env creates an object of dut\_sb which implements the checker component

- □ Implements check\_read, check\_write etc.

- scoreboard waits for a transaction to be generated then waits for the monitor to notify that this transaction occurred.

- determines the transaction correctness by applying the following:

- Each generated WRITE transactions are stored to a register file (which acts as a reference model in this case).

- Each generated READ transactions get their data field filled from the register file (so to provide an expected result).

- each transactions is then compared on a first-come firstserve basis.

### **Functional Layer (code snippet for checker)**

#### **Executes the following code in infinite loop:**

```

mon2scb.get(mon_tr);

```

```

mas_tr = from_master_q.pop_front();

```

```

exp_data = top.ml.memory_read(mas_tr.addr);

```

```

case(mas_tr.dir)

```

endcase

if(match >= max\_trans\_cnt) begin

`vmm\_verbose(this.log, \$psprintf("Done scorboarding found %d matches", match));

this.notify.indicate(this.DONE);

end

### **Command Layer (Checker)**

# APB-Monitor uses callbacks to monitor the bus before and after the transaction

```

while(1) begin

$cast(tr, randomized obj.copy());

// Pre-Rx Callback

`vmm callback(apb monitor callbacks ,monitor pre rx(this, tr));

// Sample the bus using the apb sample() task

sample apb(tr);

// Put the trans into the output channel

out chan.put(tr);

// Add a Post-Rx Callback. Typically for Coverage or Scoreboard

`vmm_callback(apb_monitor_callbacks ,monitor_post_rx(this, tr));

`vmm debug(log, tr.psdisplay("Monitor ==>"));

end

```

### **AMBA APB Property Set**

#### D PSEL:

- If PSELx is LOW for some slave x in the present cycle (1ST) and in the next (2nd) cycle it goes HIGH, it must be also HIGH in the next (3rd) cycle.

- At a time only one PSEL can be high i.e. only 1 slave can be selected at a time.

#### PENABLE:

If PENABLE is HIGH in the present cycle, it must go LOW in the next cycle.

### AMBA APB Property Set (contd..)

#### PSEL & PENABLE:

- If PSELx is LOW for some slave x in the present cycle (1st) and in the next cycle (2nd) it becomes HIGH then one more cycle later (3rd) PENABLE must also be HIGH.

- If all of the PSEL is LOW in the present cycle (1st) then in the same cycle (1st) & also in the next cycle (2nd) PENABLE must also be LOW.

- If PENABLE is HIGH (1st) and in the next cycle (2nd) PSEL is HIGH, then one more cycle (3rd) later PSEL & PENABLE are both HIGH.

### AMBA APB Property Set (contd..)

#### PENABLE & PWDATA:

If PENABLE is HIGH in the present cycle then PWDATA will hold the same value as the previous cycle.

#### PSEL & PWRITE:

■ If PWRITE changes one of the PSEL must be HIGH.

#### PENABLE & PWRITE:

If PENABLE is HIGH in the present cycle then PWRITE will hold the same value as the previous cycle.

#### PENABLE & PADDR:

If PENABLE is HIGH in the present cycle then PADDR will hold the same value as the previous cycle.