# **Design Verification –** *Overview*

Testing & Verification Dept. of Computer Science & Engg, IIT Kharagpur

#### Pallab Dasgupta

Professor, Dept. of Computer Science & Engg., Professor-in-charge, AVLSI Design Lab, Indian Institute of Technology Kharagpur

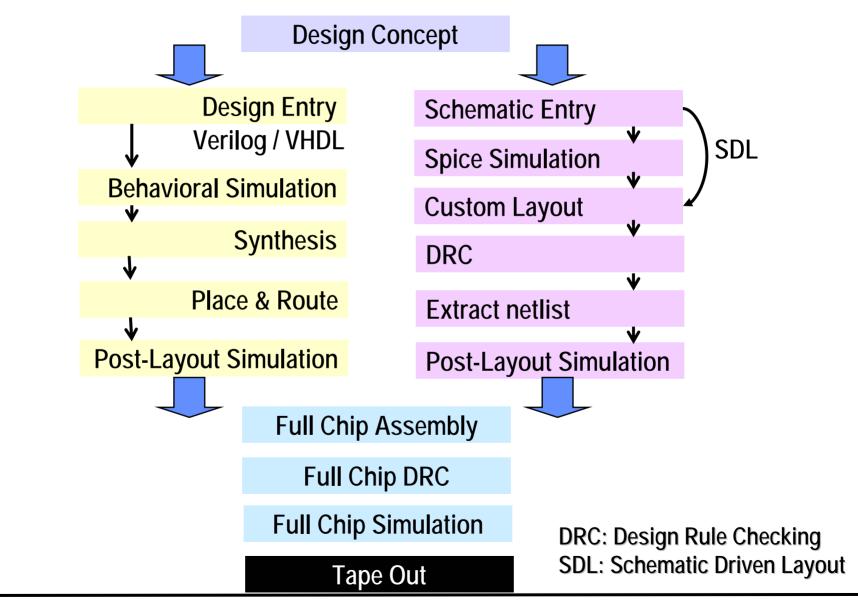

### **Design Flows: Digital versus Analog**

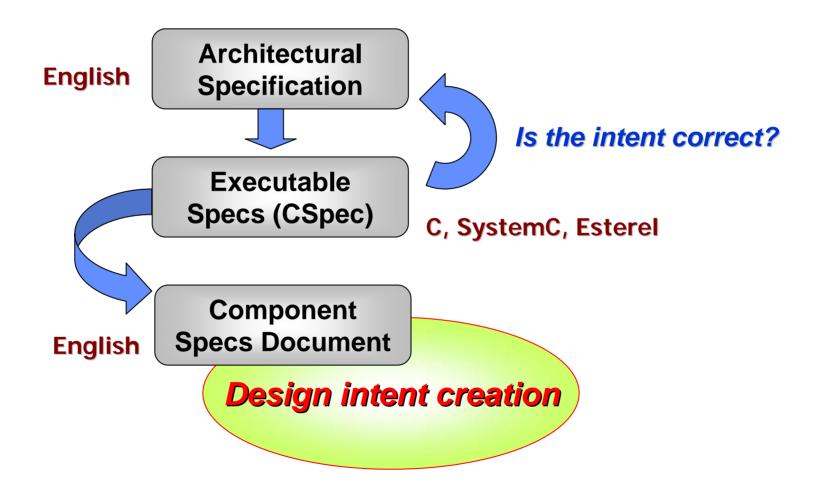

### **Design Cycle:** Intent Creation

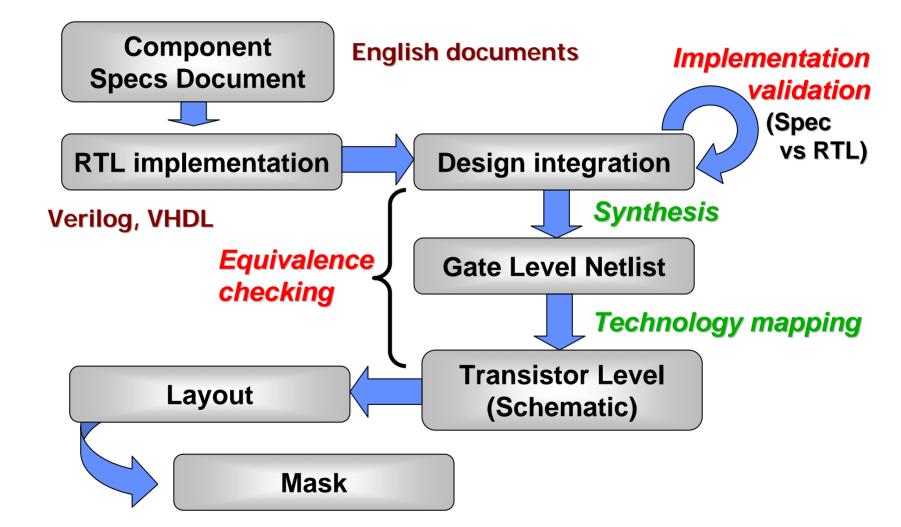

# **Design Cycle:** Implementation

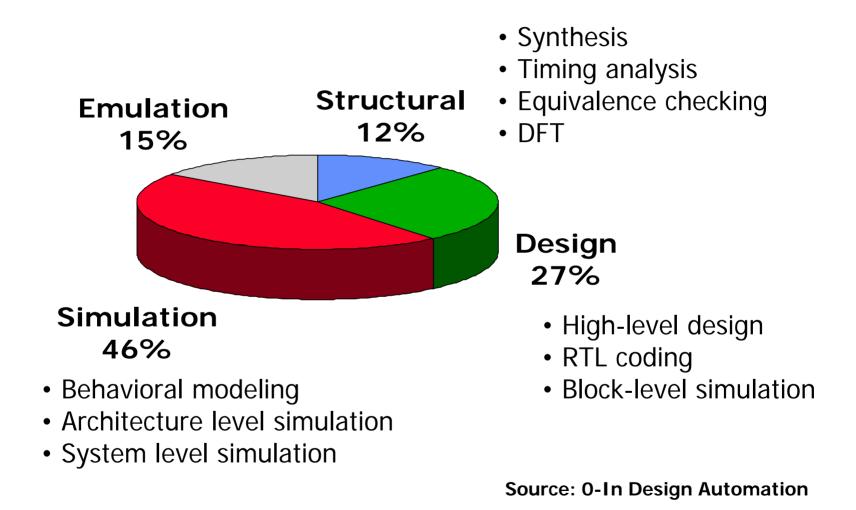

### **Verification Dominates Design**

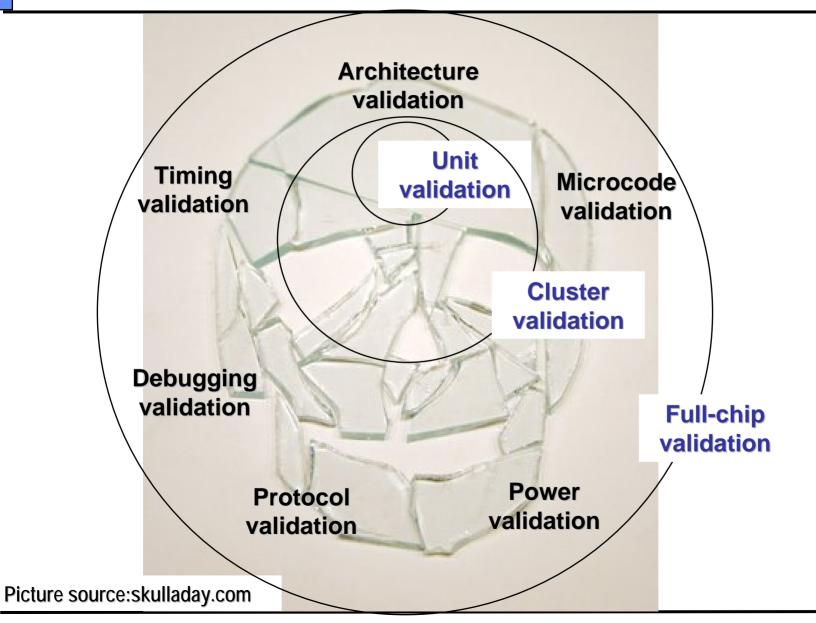

#### **Pieces of the verification puzzle**

### **Functional Verification Challenge**

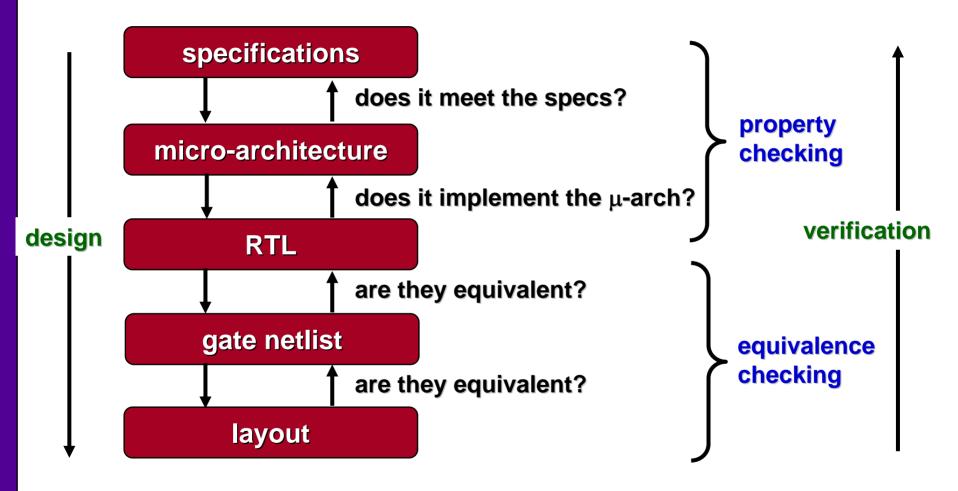

- □ Is the implementation correct?

- How do we define *correct*?

- Classical: Simulation result matches with golden

output

- Formal: Equivalence with respect to a golden model

- Property verification: Correctness properties (assertions) expressed in a formal language

- Formal: Model checking

- Semi-formal: Assertion-based verification

- Trade-off between computational complexity and exhaustiveness

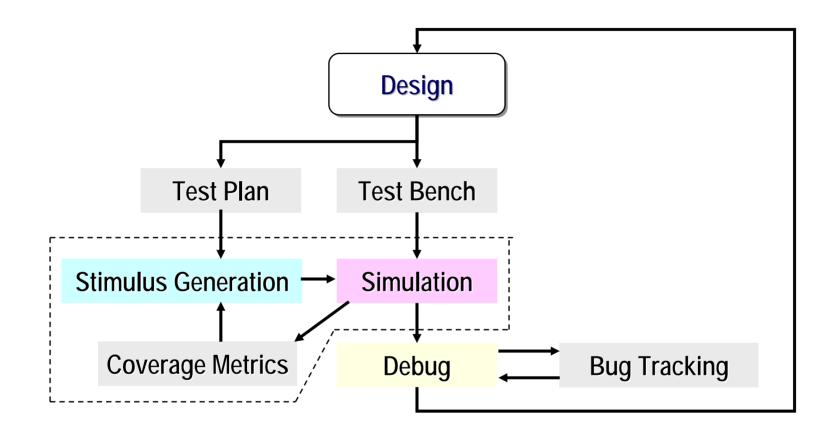

# Simulation

#### Advances:

- Test bench languages are richer (such as SystemVerilog)

- Coverage monitors and assertions

- Layered test benches and Transaction Level Modelling

# **Advent of Formal Methods in EDA**

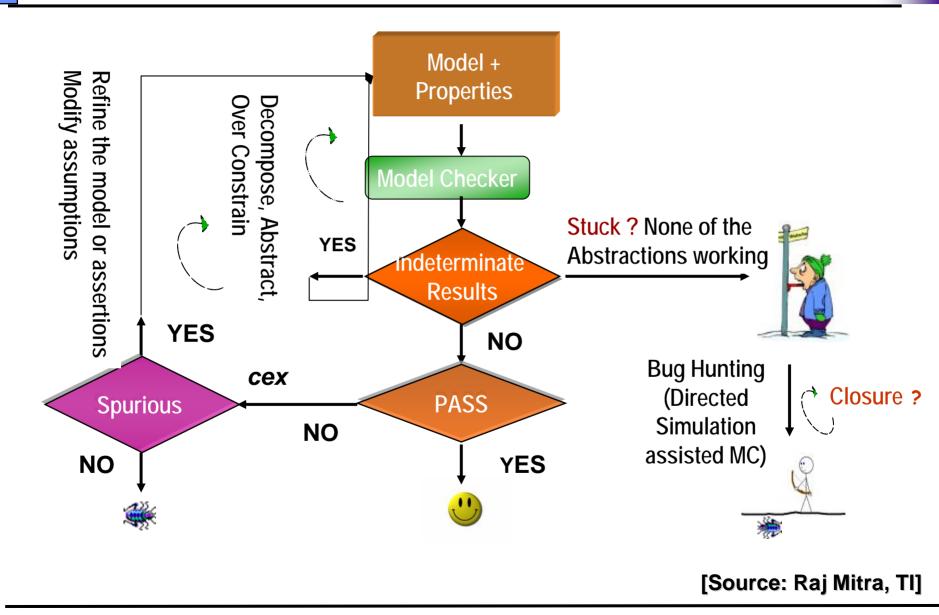

Goal: Exhaustive verification of the design intent within feasible time limits

<u>Philosophy:</u> Extraction of formal models of the design intent and the implementation and comparing them using mathematical / logical methods

| Formal Properties                                                                       | Design Intent                | Model                                          | <ul> <li>Temporal Logics         <ul> <li>(<i>Turing Award: Amir Pnueli</i>)</li> <li>Adopted by Accelera / IEEE</li> <li>Integrated into SystemVerilog</li> </ul> </li> </ul> |

|-----------------------------------------------------------------------------------------|------------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| always @( posedge clk )<br>begin<br>if (!rst) begin a1 <= a2;<br>a2 <= ~a1; end;<br>end | Register Transfer (<br>Level | Checking<br>Logical<br>Equivalence<br>Checking | <ul> <li>Tools:<br/>Academia: NuSMV, VIS<br/>Industry: Magellan (Synopsys)<br/>IFV (Cadence)</li> <li>2008: Clarke &amp; Emerson get<br/>Turing Award</li> </ul>               |

|                                                                                         | Gate Level                   |                                                |                                                                                                                                                                                |

|                                                                                         | Transistor Level             |                                                |                                                                                                                                                                                |

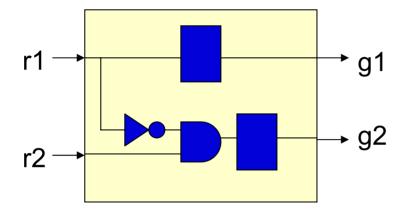

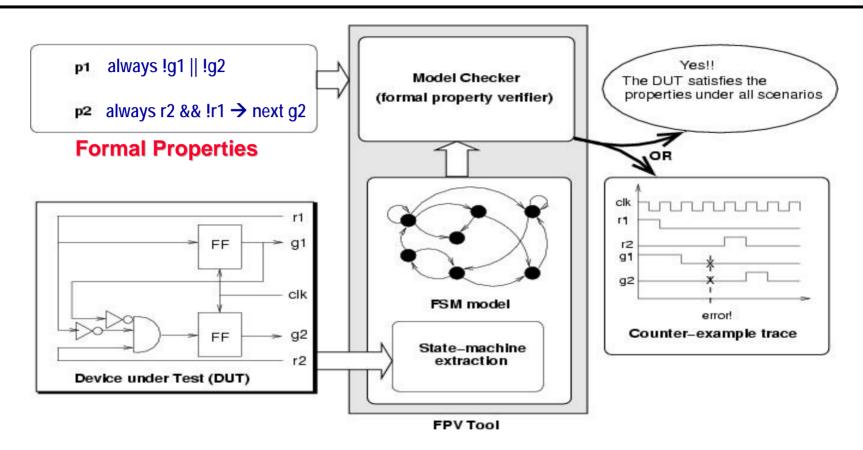

### **Toy example: Priority Arbiter**

# • Either g1 or g2 is always false (mutual exclusion)

$$G[\neg g1 \lor \neg g2]$$

When r2 is the sole request, g2 comes in the next cycle

G[ (

$$\neg$$

r1  $\land$  r2)  $\Rightarrow$  Xg2 ]

• When none are requesting, the arbiter parks the grant on g2

$$G[(\neg r1 \land \neg r2) \Rightarrow Xg2]$$

Violation!!

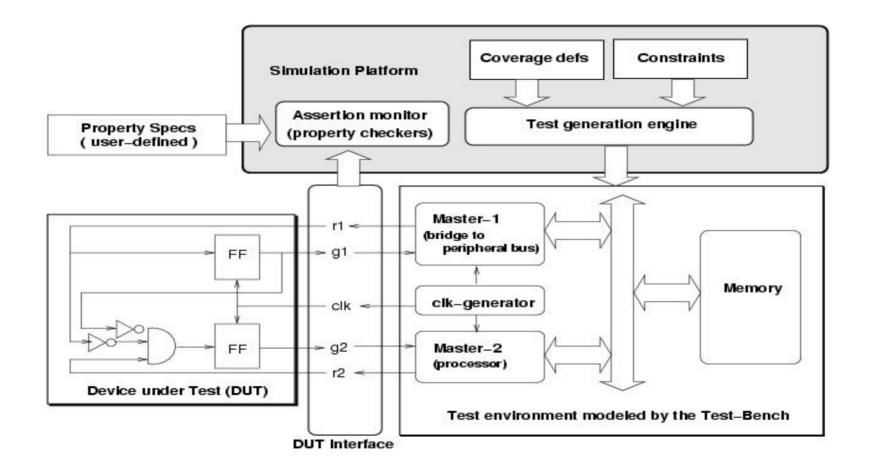

## **Dynamic Property Verification (DPV)**

[Source: A Roadmap for Formal Property Verification, Springer, 2006]

# **Formal Property Verification (FPV)**

Temporal Logics (Timed / Untimed, Linear Time / Branching Time): *LTL, CTL*

Early Languages: Forspec (Intel), Sugar (IBM), Open Vera Assertions (Synopsys)

Current IEEE Standards: SystemVerilog Assertions (SVA), Property Specification Language (PSL)

#### **Assertion Based Verification Flow**

## **Course Agenda: Verification Track**

- Design Entry: Brief overview of Verilog

- □ Simulators: How they work

- Test Scenarios and Coverage

- Static Checks

- Symbolic Representation of Logic and State Spaces: BDDs, SAT

- Equivalence Checking

- Assertions

- **Given Service Service**

- Formal Verification Coverage

# **Verification Group Profile**

The verification research group focuses on providing industrially relevant methods for the verification of various designs – ranging from digital and mixed-signal chip designs to complex software and embedded systems such as automotive control systems. Areas of strength include:

- Design Intent Verification

- Formal Verification Coverage

- Mixed-signal Design Verification

- Coverage-driven Semi-Formal Verif.

- Verification of Automotive Systems

- Verification of Web Interfaces

Home: http://www.facweb.iitkgp.ernet.in/~pallab/forverif.html

# **The Family**

#### PhD Students:

J.K. Deka (Completed) Prasenjit Basu (Submitted) Sayantan Das (Completed) Ansuman Banerjee (Submitted) Suchismita Roy (Submitted) Bhaskar Pal (Submitted) Arijit Mondal (Ongoing) P.V. Rajkumar (Ongoing) Manoj Dixit (Ongoing) Srobona Mitra (Ongoing) Priyankar Ghosh (Ongoing) Chandan Karfa (Ongoing) Subrat Panda (Ongoing) Dipankar Das (Ongoing)

#### MS Students:

Ansuman Banerjee (Completed) Bhaskar Pal (Completed) Pritam Ray (Completed) Arijit Mondal (Completed) Sayak Ray (Submitted) Anindyasundar Nandi (Submitted) Rajdeep Mukhopadhyay (Ongoing) Aritra Hazra (Ongoing) Sourashis Das (Ongoing) Kamalesh Ghosh (Ongoing) Antara Ain (Ongoing)

#### Some Alumni:

Shuvendu Lahiri (CMU), Pankaj Chauhan (CMU) Sagar Chaki (CMU), Arindam Chakraborty (UC Berkeley), Krishnendu Chakraborty (UC Berkeley), S Sriram (Stanford), Jayanta Bhadra (U Texas, Austin)

Home: http://www.facweb.iitkgp.ernet.in/~pallab/forverif.html