# Design Verification – An Introduction

#### Testing & Verification Dept. of Computer Science & Engg, IIT Kharagpur

#### Pallab Dasgupta

Professor, Dept. of Computer Science & Engg., Professor-in-charge, AVLSI Design Lab, Indian Institute of Technology Kharagpur

### **Main References**

Hardware Design Verification: *Simulation and Formal Method-Based Approaches* William K Lam Prentice Hall Modern Semiconductor Design Series

A Roadmap for Formal Property Verification A Roadmap for Formal Property Verification Pallab Dasgupts Springer

Course Web: <u>http://www.facweb.iitkqp.ernet.in/~pallab</u> and follow link to courses

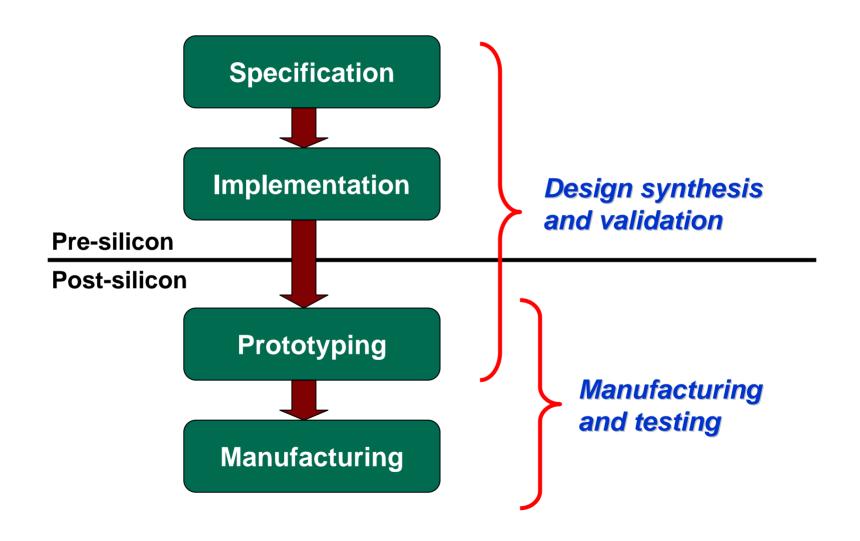

## **Design, Validation and Testing**

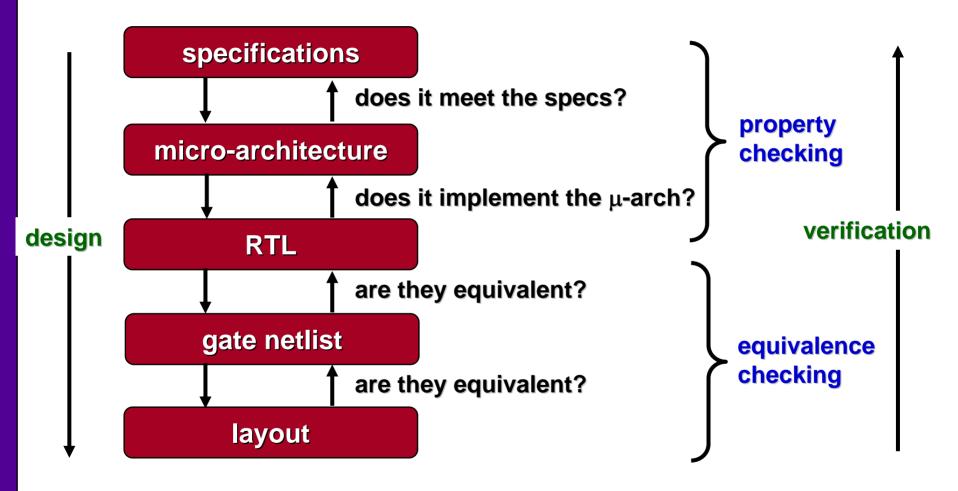

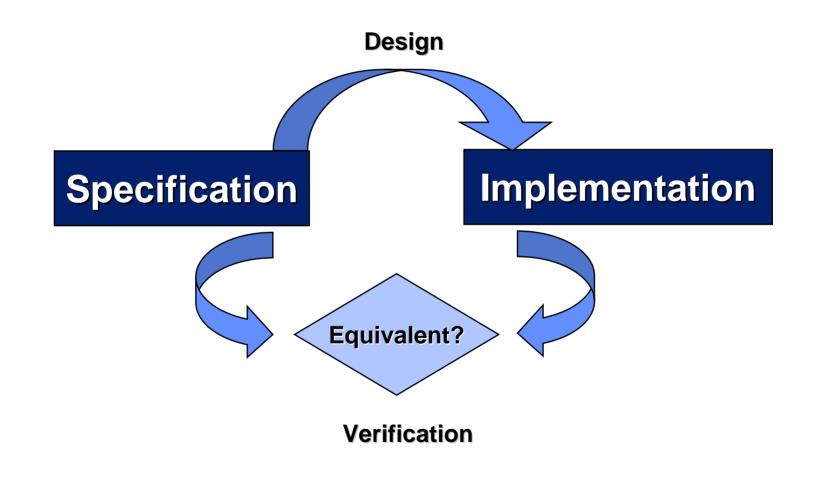

## **Design and Verification**

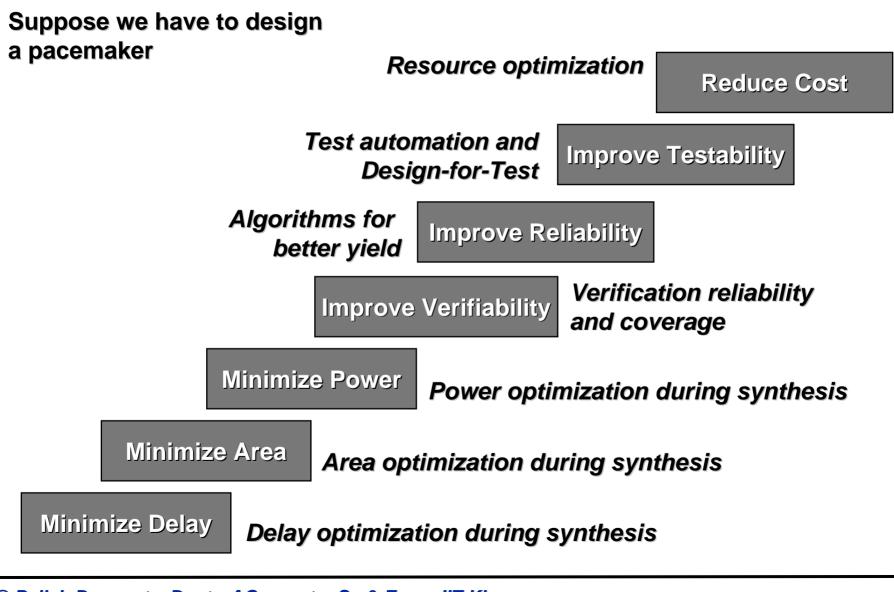

## **Design Challenges**

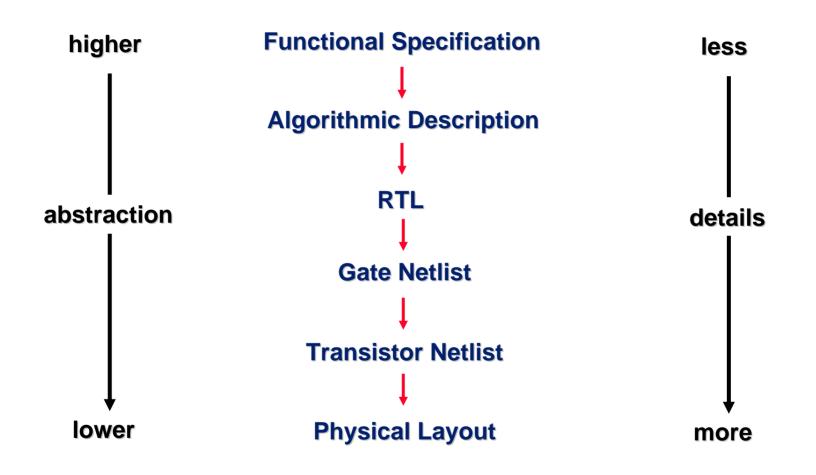

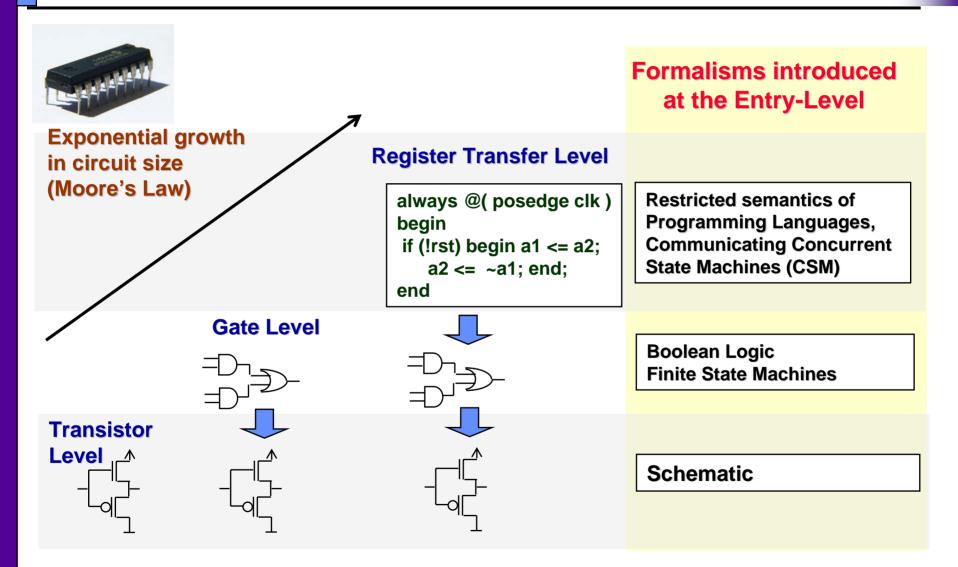

## **Digital Design: Abstraction Levels**

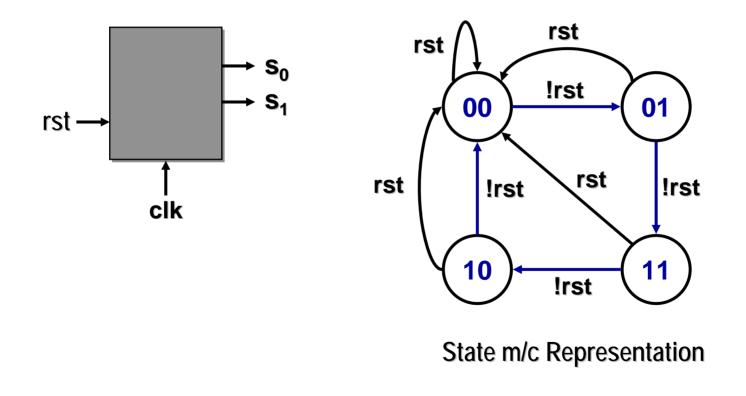

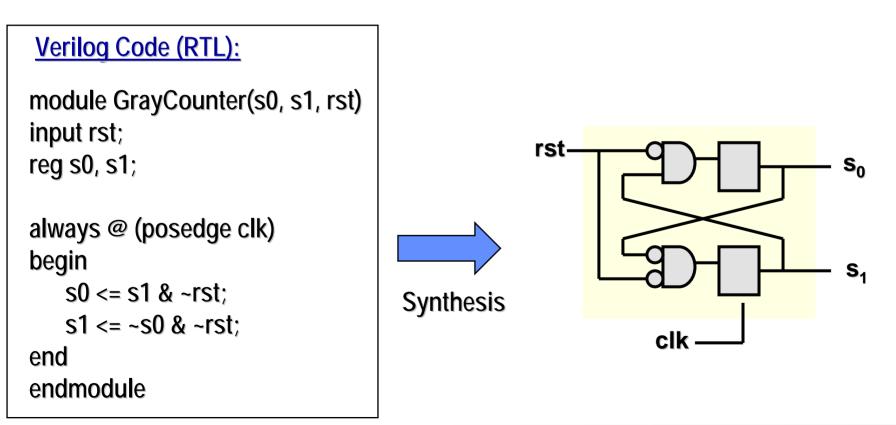

<u>Gray Counter</u>: Successive values should differ only in one bit. Reset signal resets the counter to zero.

State Transition Table

| (s <sub>0</sub> s <sub>1</sub> ) | rst | (n <sub>0</sub> n <sub>1</sub> ) |

|----------------------------------|-----|----------------------------------|

| 00                               | 0   | 01                               |

| 00                               | 1   | 00                               |

| 01                               | 0   | 11                               |

| 01                               | 1   | 00                               |

| 10                               | 0   | 00                               |

| 10                               | 1   | 00                               |

| 11                               | 0   | 10                               |

| 11                               | 1   | 00                               |

State m/c Representation

| (S <sub>0</sub> S <sub>1</sub> ) | rst | (n <sub>0</sub> n <sub>1</sub> ) |

|----------------------------------|-----|----------------------------------|

| 00                               | 0   | 01                               |

| 00                               | 1   | 00                               |

| 01                               | 0   | 11                               |

| 01                               | 1   | 00                               |

| 10                               | 0   | 00                               |

| 10                               | 1   | 00                               |

| 11                               | 0   | 10                               |

| 11                               | 1   | 00                               |

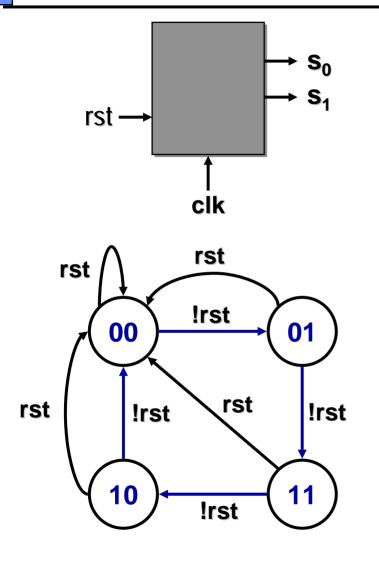

State Transition Table

#### State Transition Functions:

$$n_0 = S_0'S_1r' + S_0S_1r'$$

$$n_1 = S_0'S_1'r' + S_0'S_1r'$$

After Logic Minimization:

$$n_0 = s_1 r'$$

$n_1 = s_0' r'$

#### **State Transition Functions:**

$n_0 = S_1 r'$  $n_1 = S_0' r'$

#### © Pallab Dasgupta, Dept. of Computer Sc & Engg, IIT Kharagpur

#### **Abstractions in Design Flow**