Instructions and Addressing

### ISA vs. Microarchitecture

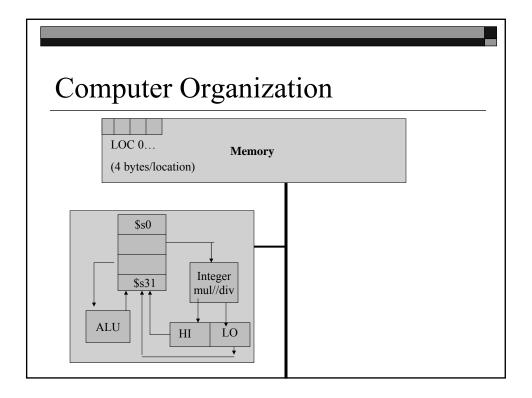

□ An ISA or Instruction Set Architecture describes the aspects of a computer architecture visible to the low-level programmer, including the native datatypes, instructions, registers, addressing modes, memory architecture, interrupt and exception handling, and I/O organization.

□ISA is a logical address.

□ <u>Microarchitecture</u> is the set of <u>internal processor</u> <u>design techniques</u> used to implement the instruction set (including microcode, pipelining, cache systems etc.)

| Anistara      | and da          | ta sizes in MIPS                   |

|---------------|-----------------|------------------------------------|

| Legisiers     | anu uc          | ita sizes ili iviti s              |

|               |                 |                                    |

| Symbolic Name | Number          | Usage                              |

| zero          | 0               | Constant 0.                        |

| at            | 1               | Reserved for the assembler.        |

| v0 - v1       | 2 - 3           | Result Registers.                  |

| a0 - a3       | 4 - 7           | Argument Registers $1 \cdots 4$ .  |

| t0 - t9       | 8 - 15, 24 - 25 | Temporary Registers $0 \cdots 9$ . |

| s0 - s7       | 16 - 23         | Saved Registers $0 \cdots 7$ .     |

| k0 - k1       | 26 - 27         | Kernel Registers $0 \cdots 1$ .    |

| gp            | 28              | Global Data Pointer.               |

| sp            | 29              | Stack Pointer.                     |

| fp            | 30              | Frame Pointer.                     |

| ra            | 31              | Return Address.                    |

## Compiling using a variable Index

- $\square$  g=h+A[i]

- □ Assume A is an array of 100 elements whose base is in register \$s3 and the compiler associates the variables g, h, and i with the registers \$s1, \$s2 and \$s4. What is the MIPS assembly code?

- add \$t1,\$s4,\$s4

- add \$t1,\$t1,\$t1

- add \$t1,\$t1,\$s3 #address of A[100]

- lw \$t0,0(\$t1)

- add \$s1,\$s2,\$t0

| e Instru             | actions                                                  | 5                                                                                                                             |                                                                                                                              |                                                                                                                                                                                                                                  |

|----------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |                                                          |                                                                                                                               |                                                                                                                              |                                                                                                                                                                                                                                  |

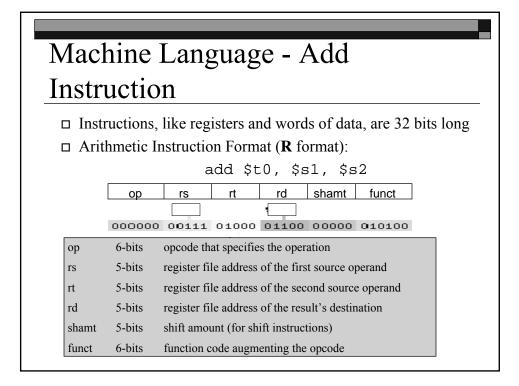

| 5 bits               | 5 bits                                                   | 6 bits                                                                                                                        | 5 bits                                                                                                                       | 6 bits                                                                                                                                                                                                                           |

| Source<br>register 1 | Source<br>register 2                                     | Destination<br>register                                                                                                       | Shift<br>amount                                                                                                              | function                                                                                                                                                                                                                         |

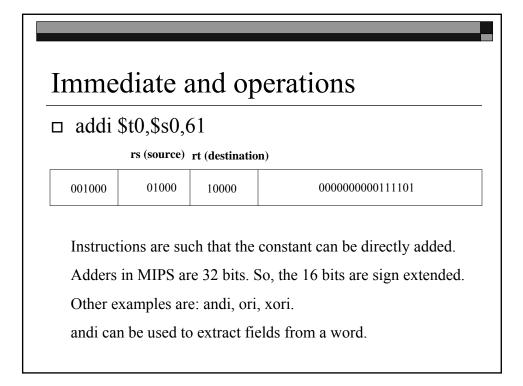

| e (Imme              | diate) In                                                | struction                                                                                                                     | S                                                                                                                            |                                                                                                                                                                                                                                  |

| 5 bits               | 5 bits                                                   |                                                                                                                               | 16 bits                                                                                                                      |                                                                                                                                                                                                                                  |

| Source               | Destination                                              |                                                                                                                               | offset                                                                                                                       |                                                                                                                                                                                                                                  |

|                      | 5 bits<br>Source<br>register 1<br>Source (Imme<br>5 bits | 5 bits   5 bits     5 bits   5 bits     Source   Source     register 1   register 2     De (Immediate) In     5 bits   5 bits | 5 bits 5 bits 6 bits   Source Source Destination   register 1 register 2 register   De (Immediate) Instruction 5 bits 5 bits | The Instruction     5 bits   5 bits   6 bits   5 bits     Source   Source   Destination   Shift     register 1   register 2   register   amount     Destination   Shift   Shift   16 bits     5 bits   5 bits   5 bits   16 bits |

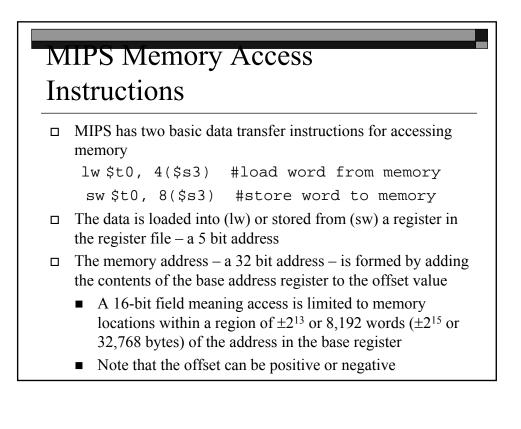

| Load           | and St    | tore In  | structions                                           |

|----------------|-----------|----------|------------------------------------------------------|

| opcode         | base reg  | data reg | offset (16 bit signed value)                         |

|                | t0,A(\$s3 | /        | mem[40+(\$s3)] into \$t0<br>\$t0 into mem[40+(\$s3)] |

| 10x011         | 10011     | 01000    | offset (16 bit signed value)                         |

| 1w=35<br>sw=43 | Base Reg  | Data Reg | Offset relative to base                              |

### Obtaining the Machine Code

- □ A[300]=h+A[300]

- assume that \$t1 has the base address of the array A and \$s2 stores the value of h

- opcodes for lw: 35, add:0, sw: 43

- $\square$  Assembly:

- lw \$t0,1200(\$t1)

- add \$t0,\$s2,\$t0

- sw \$t0,1200(\$t1)

- □ Write the machine language instructions?

op

26

31

Jump Target Address

0

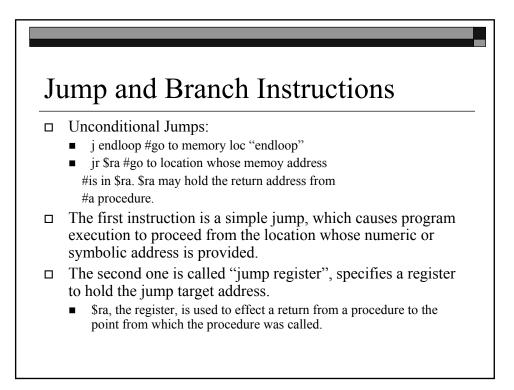

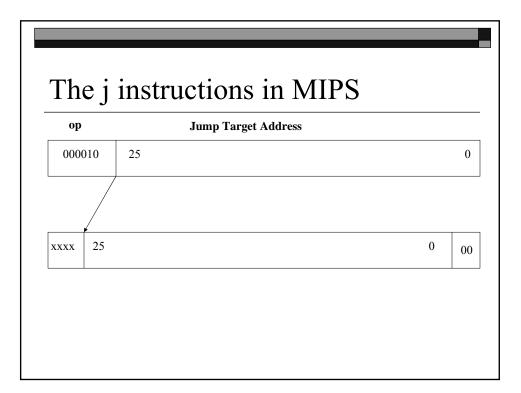

□ For the j instructions, the 26-bit address field in the instruction, is augmented with:

• 00 to the right

25

- 4 higher order bits of the program counter to the left

- □ Called as Pseudodirect-addressing.

| 000000 | 11111                     | 00000  | 00000  | 00000  | 001000           |

|--------|---------------------------|--------|--------|--------|------------------|

| OpCode | Source<br>register (\$ra) | Unused | Unused | Unused | function<br>jr=8 |

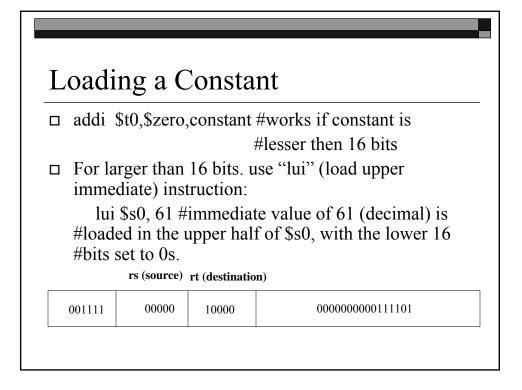

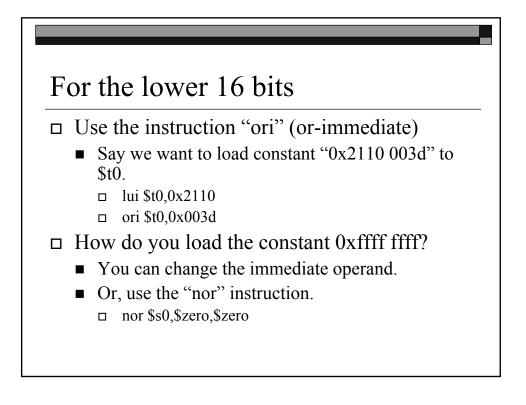

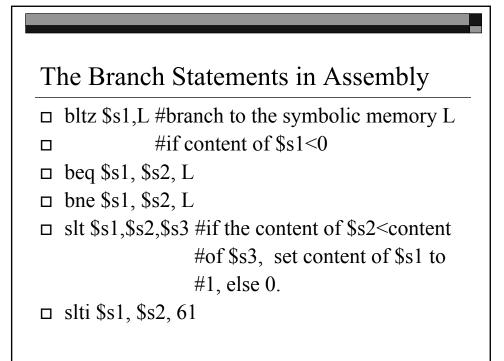

| Mach   | ine La         | nguag           | e (M/L) Formats                                                                   |

|--------|----------------|-----------------|-----------------------------------------------------------------------------------|

| ор     |                | rt (destination |                                                                                   |

| 000001 | 10001          | 00000           | 000000000111101                                                                   |

| bltz=1 | Source<br>\$s1 |                 | Relative Branch Distance in words                                                 |

| ор     | rs (source)    | rt (destination | ) offset                                                                          |

| 00010x | 10001          | 10010           | 000000000111101                                                                   |

| beq=4  | 1              | II              | Relative Branch Distance in words                                                 |

| r      | -              | (why?) and ac   | essing: the 16-bit signed offset is<br>Ided to the 32 bit PC, to get a 32 bit bra |

| Other Branch Statements in M/L |                              |                                   |                                 |                      |                    |  |

|--------------------------------|------------------------------|-----------------------------------|---------------------------------|----------------------|--------------------|--|

| ⊐ slt:                         |                              | slt \$s1,\$s2,\$s3                |                                 |                      |                    |  |

| 000000                         | 10010                        | 10011                             | 10001                           | 00000                | 101010             |  |

| OpCode<br>□ <b>slti:</b>       | Source<br>register<br>(\$s2) | Source<br>register<br>(\$s3)      | Destination<br>Register<br>\$s1 | Unused               | function<br>slt=42 |  |

| 001010                         | 10010                        | 10001                             | 000000000111101                 |                      |                    |  |

| OpCode<br>slti=10              | Source<br>register<br>(\$s2) | Destination<br>Register<br>(\$s1) | Imm<br>slti \$s1,\$s2           | ediate Operar<br>,61 | ıd                 |  |

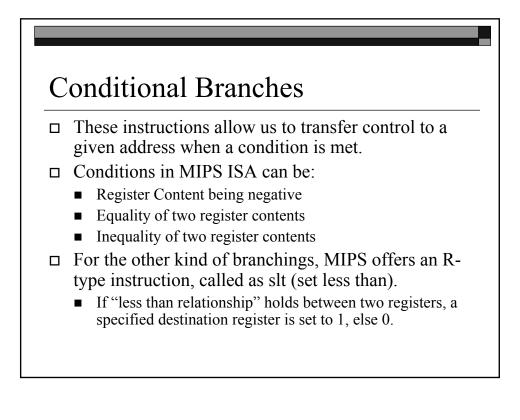

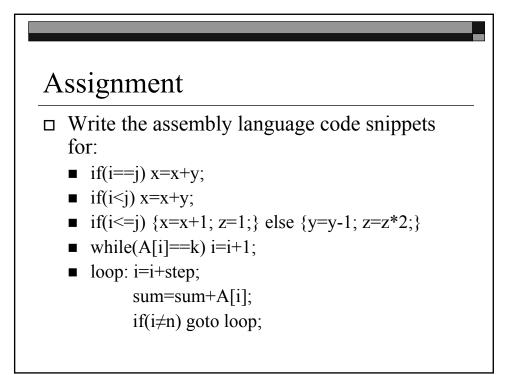

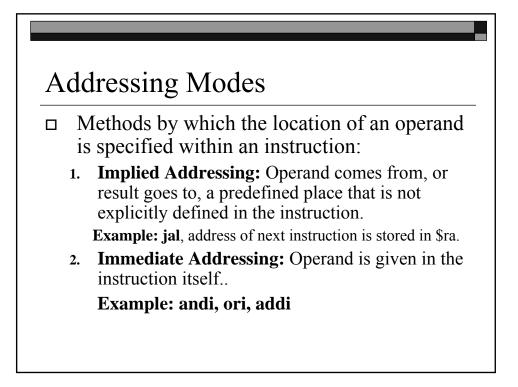

## Addressing Modes

- Register Addressing: Operand is taken from, or result placed in, a specified register. Example: R-type Instructions.

- 4. **Base Addressing:** Operand is in memory and its location is computed by adding a 16-bit signed integer, the offset, with the contents of the base register, specified in the instruction.

Example: lw, sw

# Addressing Modes

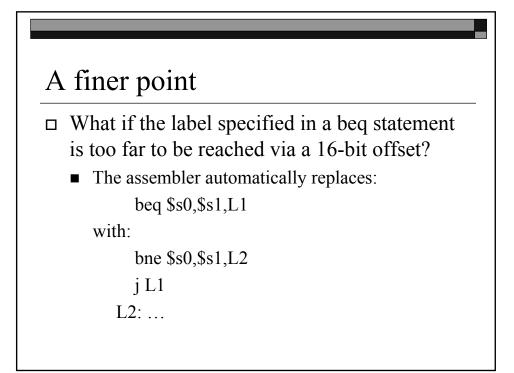

5. **PC-relative addressing:** Same as base addressing, but the register is always the Program Counter (PC).

#### Example: beq, bne

6. **Pseudo-direct addressing:** In direct addressing, the operand address is part of the instruction. However this is not possible in MIPS, as we have 32 bit instruction, and address also of 32 bits. Hence, we have pseudo-direct addressing.

#### **Example: j instruction**

## **MIPS** Instructions

□ Please refer text book for the list.

### Summary

- MIPS has a load/store architecture => operands must be in registers before they are executed.

- MIPS instructions for accessing memory: load, store, jump/branch

- □ MIPS has limited addressing modes:

- efficient hardware design is possible.

- Adequate for programming.