# Transistor Parameter Determination for Digital Circuits

Sukriti Dhang

### Transistor Parameter Determination for Digital Circuits

Thesis submitted to Indian Institute of Technology Kharagpur for the award of the degree

of

### Master of Science

(by research)

by

### Sukriti Dhang

under the guidance of

**Professor Chittaranjan Mandal** (Department of Computer Science and Engineering)

and

**Professor Indrajit Chakrabarti** (Department of Electronics and Electrical Communication Engineering)

Advanced Technology Development Centre INDIAN INSTITUTE OF TECHNOLOGY KHARAGPUR October 2020

### **CERTIFICATE OF APPROVAL**

Certified that the thesis entitled "**Transistor Parameter Determination for Digital Circuits**" submitted by **Sukriti Dhang** to the Indian Institute of Technology, Kharagpur for the award of the degree of Master of Science (by research), has been accepted by the external examiners and that the student has successfully defended the thesis in the viva-voce examination held date.

Prof. Chittaranjan Mandal (Supervisor)

Prof. Indrajit Chakrabarti (Co-supervisor)

Prof. Santanu Chattopadhyay (Chairman of the DSC)

Prof. Pralay Mitra (Member of the DAC)

Prof. Rajib Mall (Member of the DAC) Prof. (External Examiner)

Advanced Technology Development Centre Indian Institute of Technology Kharagpur Kharagpur, India-721302

### Certificate

This is to certify that this thesis entitled **Transistor Parameter Determination for Digital Circuits** submitted by **Sukriti Dhang**, to the Indian Institute of Technology Kharagpur, is a record of bona fide research work carried out under our supervision and is worthy of consideration for award of Master of Science (by reasearch) of the Institute.

**Prof. Chittaranjan Mandal** Department of Computer Science Engineering Indian Institute of Technology Kharagpur India - 721302.

Chakrabark 08.11.2020

**Prof. Indrajit Chakrabarti** Department of Electronics and Electrical Communication Engineering Indian Institute of Technology Kharagpur India - 721302.

I.I.T. Kharagpur October 2020

### **Declaration**

#### I certify that

- a. the work contained in the thesis is original and has been done by me under the guidance of my supervisor;

- b. the work has not been submitted to any other institute for any other degree or diploma;

- c. I have followed the guidelines provided by the Institute in preparing the thesis;

- d. I have conformed to ethical norms and guidelines while writing the thesis;

- e. whenever I have used materials (data, models, figures and text) from other sources, I have given due credit to them by citing them in the text of the thesis, and giving their details in the references, and taken permission from the copyright owners of the sources, whenever necessary.

Sukriti Shang Sukriti Dhang

### Acknowledgment

I am profoundly grateful to my supervisors **Prof. Chittaranjan Mandal** and **Prof. Indrajit Chakrabarti** for their guidance and continuous encouragement throughout the thesis work. Secondly, I would like to thank my fellow classmates for their support and also to all my professors. Finally, I express my sincere heartfelt gratitude to my parents and my beloved sister for supporting and encouraging me with their best wishes, during the course of the work.

Sukriti Dhang

October 2020 Indian Institute of Technology Kharagpur

### Abstract

Transistor sizing to achieve desired performance parameters is an important design challenge. Accurate modelling is essential for parameter optimisation. This thesis presents hybrid modelling of CMOS circuits at level 2 and modelling complex CMOS circuits at a higher level i.e. level 49, parameter optimisation and determination of performance parameters (rise time, fall time and power dissipation).

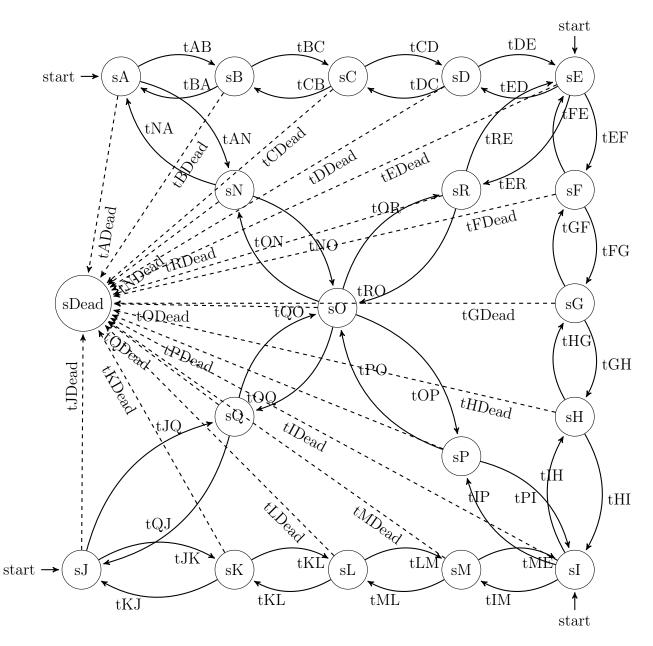

The work in this thesis first models the circuit to be analysed through a set of differential equations based on the behaviour of the transistors and their interconnections. Simple ODE modelling isn't adequate as the transistors may be in various states (cutoff, linear, saturation). Accordingly, a circuit with n transistors may have up to  $3^n$  states. As the circuit operates, it makes transitions between these states (also called locations). ODE modelling is inadequate to capture this kind of situation. To handle this, the modeling of CMOS circuits have been done as a Stateflow model in Matlab Simulink. The standard equations which govern nMOS and pMOS transistors and involve the transistor geometries as parameters have been used.

As a number of locations corresponding to the regions of operations of the transistors are involved, it is important to check that all relevant transitions are adequately covered. This may be called the completeness of the model. In this thesis a mechanism is also presented to determine the completeness of the modelling of the circuit.

In each location, corresponding to the regions of operation of the transistors, Spice Level 2 model equations have been considered which include second-order effects. These equations are directly related to the specification of different parameters of the transistors. To describe different operating regions of the transistors, the differential equations have been formulated. The mechanism has been successfully demonstrated on a CMOS inverter, a CMOS NAND2 and CMOS NOR2 gate. An efficient modeling technique has been developed for CMOS circuits with separate networks of pMOS/nMOS transistors for pull-up/pull-down operations. The output waveform of the Stateflow model is displayed in a display box with respect to the imulation time. The advantage of the present modeling technique is that Stateflow models are comparable with respect to real circuit simulation results and the model evaluation time is comparatively fast.

The thesis then presents complex CMOS circuit modeling in MATLAB Simulink as Stateflow model. Modeling of a precharge based circuit using higher level model equations has been done. To determine the accuracy of the model that depends on the equations governing the behaviour of the MOSFETs, BSIM3v3 level49 equations have been considered. It also depends on the influence of the various model parameters. An efficient modeling technique has been developed for CMOS circuit with a precharge based circuit with separate pMOS/nMOS networks. The model's completeness and circuit performance requirements are formulated and reachability analysis has been performed on the model. The benefit of the present modeling technique is that Stateflow model is comparable with respect to real circuit simulation results. Though the model uses complex circuit equations, evaluation time is comparatively fast.

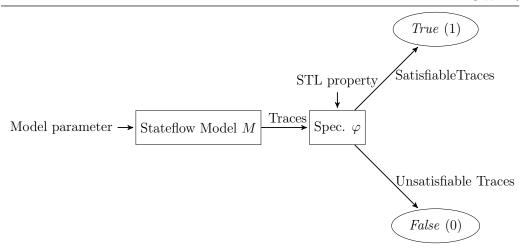

This thesis then presents an application of SAT based tool to find optimal values of the relevant parameters to achieve a specified circuit performance. Signal temporal logic (STL) formulas are used to specify the desired properties of continuous signals determining the parameters of the underlying model. Two optimisation algorithm have been used Nelder Mead (NM) algorithm of Breach tool and a 2D search algorithm. The circuit performance is optimised through finding a range of admissible circuit parameters. Results obtained from Breach can be visualised through Matlab Simulink. An efficient optimisation technique has been developed for CMOS circuits that determine the transistor parameters. The advantage of the optimisation technique is that a range of admissible circuit parameters are obtained.

This thesis finally presents experimentations on CMOS inverter, NAND2, NOR2 and precharge based circuit. The effectiveness of the above modeling technique has been demonstrated with a set of experimental results. The CMOS circuits have been redesigned using Spice simulator with synthesized transistor size values obtained using optimisation algorithms. Results obtained from NM and 2D search algorithms are comparable with the Spice results.

**Keywords** : CMOS transistor sizing, Stateflow model, precharged CMOS logic, level 49 BSIM3 MOSFET model, reachability analysis, signal temporal logic, Nelder Mead algorithm, 2D search algorithm

# Contents

| Lis | st of                            | Abbreviations and Symbols                                                                                                                                                                                                                                                                                                                                                                                                 | $\mathbf{v}$                                        |

|-----|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Lis | st of                            | Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                | vii                                                 |

| Lis | st of                            | Equations                                                                                                                                                                                                                                                                                                                                                                                                                 | ix                                                  |

| Lis | st of                            | Figures                                                                                                                                                                                                                                                                                                                                                                                                                   | xi                                                  |

| Lis | st of                            | Tables                                                                                                                                                                                                                                                                                                                                                                                                                    | xiii                                                |

| 1   | <b>Intr</b><br>1.1<br>1.2<br>1.3 | Poduction         Motivation         Overview and Contributions of the Thesis         1.2.1         Contribution         Organization of the rest of the Thesis                                                                                                                                                                                                                                                           | 1<br>2<br>3<br>3<br>4                               |

| 2   | Lite<br>2.1<br>2.2<br>2.3        | erature Survey         Modelling of Digital Circuits         Rise Time and Fall Time and Power Dissipation         Optimisation techniques                                                                                                                                                                                                                                                                                | 7<br>7<br>8<br>10                                   |

| 3   |                                  | delling and Analysis of Transistor Operation using Spice         S Level 2 Model         Modelling Mechanism and Completeness         3.1.1 Stateflow         3.1.2 Rechability Analysis and Completeness         Transistor Operation Modelling         3.2.1 Description of MOSFET Parameters at SPICE Level 2         3.2.2 MOSFET Level 2 Model Eequations         3.2.2.1 DC Model         3.2.2.2 Capacitance Model | <b>11</b><br>11<br>15<br>16<br>16<br>19<br>19<br>24 |

|     | $3.3 \\ 3.4$                     | Stateflow Modelling of CMOS Inverter                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{25}{28}$                                     |

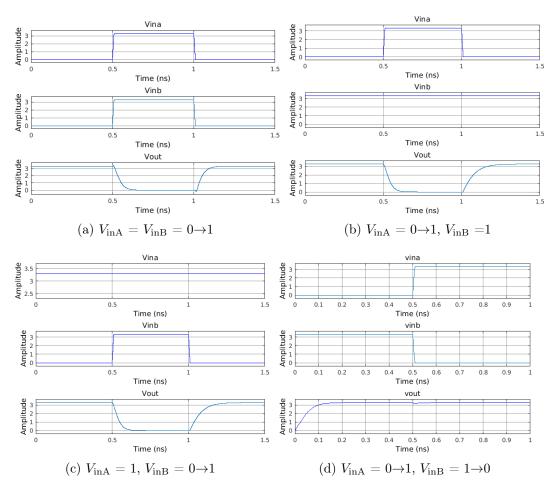

|          |                                                                                                                                                            | 3.4.1 Case 1 : $V_{inA} = V_{inB} = 0 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                                                            | 3.4.2 Case 2: $V_{inA} = 1$ , $V_{inB} = 0 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                               |

|          |                                                                                                                                                            | 3.4.3 Case 3: $V_{inB} = 1, V_{inA} = 0 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                                                                                                                                                            | 3.4.4 Case 4 : $V_{inA} = 0 \rightarrow 1$ , $V_{inB} = 1 \rightarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                |

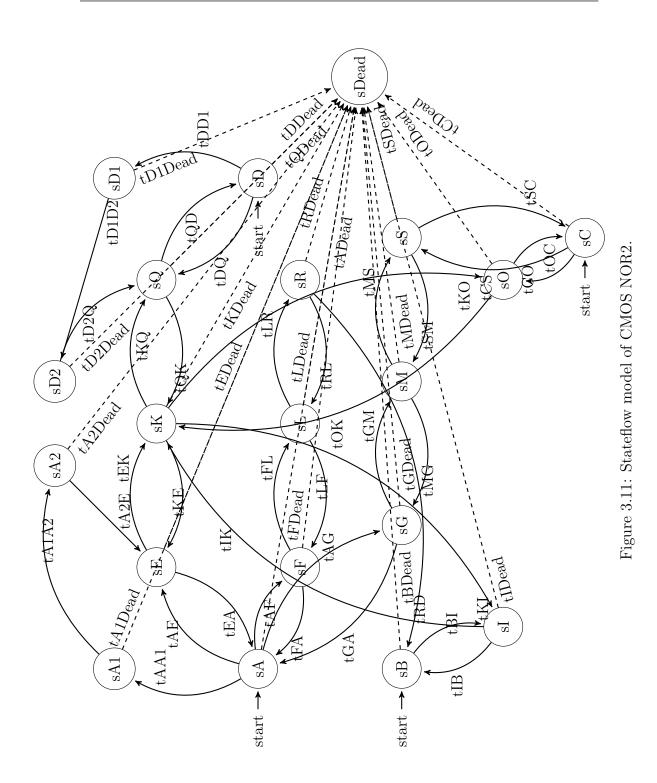

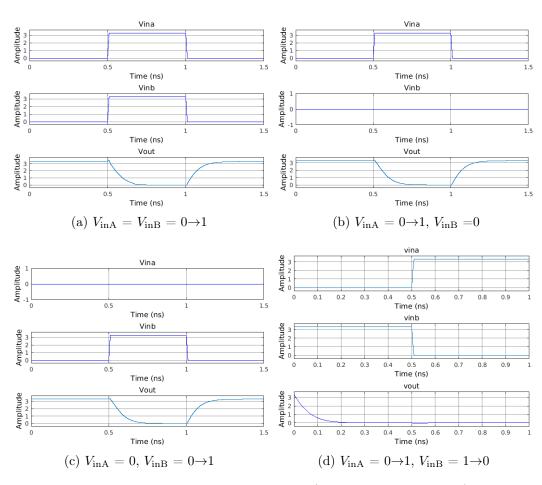

|          | 3.5                                                                                                                                                        | Stateflow Model of CMOS NOR2                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |                                                                                                                                                            | 3.5.1 Case 1 : $V_{inA} = V_{inB} = 0 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                                                                                                                                            | 3.5.2 Case 2: $V_{inA} = 0, V_{inB} = 0 \rightarrow 1 \dots \dots \dots \dots 4$                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                            | 3.5.3 Case 3: $V_{\text{inB}} = 0$ , $V_{\text{inA}} = 0 \rightarrow 1$                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |                                                                                                                                                            | 3.5.4 Case 4 : $V_{inA} = 0 \rightarrow 1$ , $V_{inB} = 1 \rightarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                |

|          | 3.6                                                                                                                                                        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4        | Mo                                                                                                                                                         | delling and Analysis of Transistor Operation using BSIM3v3                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                                                                                                                                                            | rel 49 MOSFET Model 54                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 4.1                                                                                                                                                        | Transistor Operation Modelling 5                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                                                                                            | 4.1.1 Description of MOSFET Parameters at Level 49 5                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                                                                                                                                                            | 4.1.2 MOSFET Level 49 Model Equation 5                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 4.2                                                                                                                                                        | Mechanism of Dual-rail Precharge based Circuit 6                                                                                                                                                                                                                                                                                                                                                                                                                        |

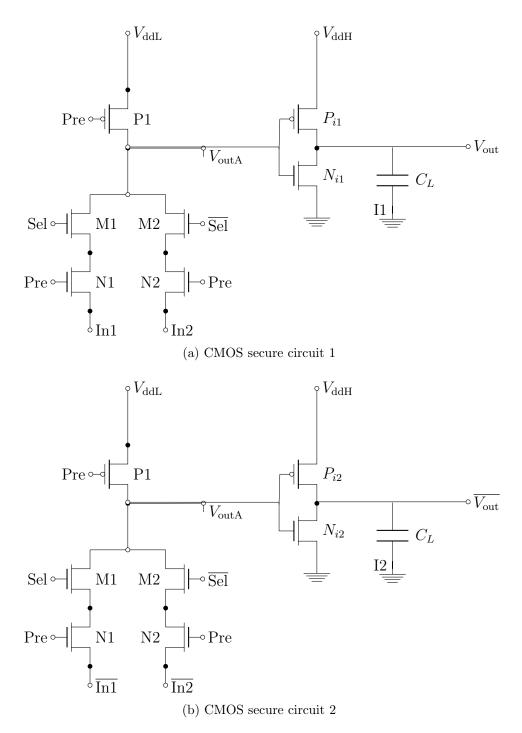

|          | 4.3                                                                                                                                                        | Stateflow Model of Secure Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |                                                                                                                                                            | $4.3.1  \text{Choice of start state}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  6$                                                                                                                                                                                                                                                                                                                                                                               |

|          | 4.4                                                                                                                                                        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|          |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| <b>5</b> | Par                                                                                                                                                        | ameter Optimisation for Delay and Power 7                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5        | <b>Par</b><br>5.1                                                                                                                                          | cameter Optimisation for Delay and Power       7         Signal Temporal Logic (STL)       7                                                                                                                                                                                                                                                                                                                                                                            |

| 5        |                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5        | 5.1                                                                                                                                                        | Signal Temporal Logic (STL)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5        | 5.1                                                                                                                                                        | Signal Temporal Logic (STL)                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5        | 5.1                                                                                                                                                        | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1Proposed 2D Search Algorithm7                                                                                                                                                                                                                                                                                                                                                                                   |

| 5        | 5.1<br>5.2<br>5.3                                                                                                                                          | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1Proposed 2D Search Algorithm75.2.2Nelder Mead Algorithm10                                                                                                                                                                                                                                                                                                                                                       |

|          | 5.1<br>5.2<br>5.3                                                                                                                                          | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1Proposed 2D Search Algorithm75.2.2Nelder Mead Algorithm10Summary10                                                                                                                                                                                                                                                                                                                                              |

|          | <ul><li>5.1</li><li>5.2</li><li>5.3</li><li>Case</li></ul>                                                                                                 | Signal Temporal Logic (STL)       7         Optimization Algorithm       7         5.2.1       Proposed 2D Search Algorithm       7         5.2.2       Nelder Mead Algorithm       10         Summary       10       10         11                                                                                                                                                                                                                                     |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> </ul>                                                                  | Signal Temporal Logic (STL)       7         Optimization Algorithm       7         5.2.1       Proposed 2D Search Algorithm       7         5.2.2       Nelder Mead Algorithm       10         Summary       10       10         Se Study for CMOS Circuits       11         Experimental Results for CMOS Inverter       11                                                                                                                                            |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> </ul>                                                                  | Signal Temporal Logic (STL)       7         Optimization Algorithm       7         5.2.1       Proposed 2D Search Algorithm       7         5.2.2       Nelder Mead Algorithm       10         Summary       10       10         Se Study for CMOS Circuits         Experimental Results for CMOS Inverter       11         Experimental Result for CMOS NAND2       11                                                                                                 |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul>                                                     | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1 Proposed 2D Search Algorithm75.2.2 Nelder Mead Algorithm10Summary10Summary10Se Study for CMOS Circuits11Experimental Results for CMOS Inverter11Experimental Result for CMOS NAND211Experimental Result for CMOS NOR211                                                                                                                                                                                        |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> </ul>                                        | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1 Proposed 2D Search Algorithm75.2.2 Nelder Mead Algorithm10Summary10Summary10Se Study for CMOS Circuits11Experimental Results for CMOS Inverter11Experimental Result for CMOS NAND211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211                                                                                                                  |

|          | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>              | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1 Proposed 2D Search Algorithm75.2.2 Nelder Mead Algorithm10Summary10Summary10Se Study for CMOS Circuits11Experimental Results for CMOS Inverter11Experimental Result for CMOS NAND211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Validation of CMOS Circuits11                                                                                                                        |

| 6        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul>              | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1 Proposed 2D Search Algorithm75.2.2 Nelder Mead Algorithm10Summary10Summary10Se Study for CMOS Circuits11Experimental Results for CMOS Inverter11Experimental Result for CMOS NAND211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for Secure Circuit11Validation of CMOS Circuits12Summary12 |

| 6        | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Case</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>Con</li> </ul> | Signal Temporal Logic (STL)7Optimization Algorithm75.2.1 Proposed 2D Search Algorithm75.2.2 Nelder Mead Algorithm10Summary10Summary10Se Study for CMOS Circuits11Experimental Results for CMOS Inverter11Experimental Result for CMOS NAND211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for CMOS NOR211Experimental Result for Secure Circuit12Numary12Summary12Summary12Numary12Numary12                                |

| В            | SPICE Model Parameters of MOSFETS            | 139 |

|--------------|----------------------------------------------|-----|

| $\mathbf{C}$ | SPICE Model Parameters of MOSFETS - Level 49 | 141 |

# List of Abbreviations and Symbols

| ADC                  | Area-Delay Curve                                               |

|----------------------|----------------------------------------------------------------|

| APE                  | Analog Performance Estimation                                  |

| NM                   | Nelder Mead                                                    |

| CMOS                 | Complementary Metal-Oxide Semiconductor                        |

| DE                   | Differential Evolution                                         |

| MOS                  | Metal-Oxide Semiconductor                                      |

| MDE                  | Minimum Delay Estimation                                       |

| PSO                  | Particle Swarm Optimization                                    |

| RGA                  | Real-coded Genetic Algorithm                                   |

| $\operatorname{STL}$ | Signal Temporal Logic                                          |

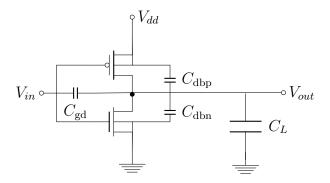

| $C_{ m L}$           | is the load capacitance                                        |

| $C_{ m dbn}$         | is the drain to bulk junction capacitances of nMOS transistors |

| $C_{ m dbp}$         | is the drain to bulk junction capacitances pMOS transistors    |

| $C_{ m gdn}$         | is the gate to drain capacitances of nMOS transistors          |

| $C_{\mathrm{gdp}}$   | is the gate to drain capacitances of pMOS transistors          |

| GND                  | Ground                                                         |

| L                    | Channel Length of transistor                                   |

| $I_{\mathrm{p}}$     | is the drain current through pMOS                              |

| In                   | is the drain current through nMOS                              |

| $t_r$                | Rise Time                                                      |

| $t_f$                | Fall Time                                                      |

| $V_{ m dd}$          | Supply voltage                                                 |

| $V_{ m ds}$          | voltage between drain and source                               |

| $V_{ m dsat}$        | saturation voltage                                             |

| $V_{ m gs}$          | voltage between gate and source                                |

| $V_{ m out}$         | is the output voltage                                          |

| $V_{ m th}$          | Threshold voltage                                              |

### LIST OF ABBREVIATIONS AND SYMBOLS

| $V_{ m bi}$              | Built-in voltage                                      |

|--------------------------|-------------------------------------------------------|

| $V_{ m to}$              | Zero-bias threshold voltage                           |

| $V_{ m FB}$              | flatband voltage                                      |

| W                        | Channel width of transistor                           |

| $\phi_{\mathbf{f}}$      | is bulk Fermi potential                               |

| $\phi_{ m ms}$           | is metal semiconductor work function differnce        |

| $\gamma$                 | is the body effect factor                             |

| $F_1$                    | is the short channel factor                           |

| $F_{\mathbf{w}}$         | is the narrow width factor based on thick field oxide |

| $X_{j}$                  | is the junction depth of source and drain junction    |

| $X_{ m sd}$              | is the depletion layer width of source                |

| $X_{ m dd}$              | is the depletion layer width of drain                 |

| $\epsilon_{\mathrm{o}}$  | is dieletric constant of vaccum                       |

| $\epsilon_{\mathrm{ox}}$ | is dielectric constant of $SiO_2$                     |

| $\epsilon_{ m si}$       | is permitivity of Si                                  |

| $\mu_{ m n}$             | is carrier mobility of nMOS                           |

| $C_{\rm OX}$             | is the gate oxide capacitance per unit area           |

| $t_{\rm ox}$             | is the thickness of oxide layer                       |

| $\lambda$                | is the channel-length modulation                      |

| $P_{ m p}$               | is peak power at pMOS transistor                      |

| $P_{\rm n}$              | is peak power at nMOS transistor                      |

| $P_{\rm sc}$             | is short circuit power dissipation                    |

|                          |                                                       |

# List of Algorithms

| 1 | Algorithm to identify search range for STL formula where ob- |    |

|---|--------------------------------------------------------------|----|

|   | jective function components vary monotonically with wn and   |    |

|   | wp                                                           | 78 |

| 2 | 2D search for parameter estimation                           | 82 |

# List of Equations

| 3.1 Zero bias threshold voltage of a long and wide channel device $(V_{\rm to})$               | 17 |

|------------------------------------------------------------------------------------------------|----|

| 3.4 Intrinsic transconductance parameter $(k_{\rm p})$                                         | 17 |

| 3.5 Surface potential (Phi)                                                                    | 18 |

| 3.7 Surface Mobility Degradation                                                               | 18 |

| 3.8 Threshold voltage equation at Level 2                                                      | 21 |

| 3.9 Built in voltage for narrow channel                                                        | 21 |

| 3.10Short channel factor $(F_1)$ at Level 2 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 21 |

| 3.11Narrow width factor $(F_w)$ at Level 2                                                     | 21 |

| 3.14Saturation voltage of nMOS transistor at Level 2                                           | 21 |

| 3.15Linear drain current equation of nMOS at Level 2                                           | 22 |

| 3.16Saturation drain current equation of nMOS at Level 2                                       | 22 |

| 3.17Linear drain current equation of pMOS at Level 2                                           | 23 |

| 3.18Saturation drain current equation of pMOS at Level 2                                       | 23 |

| 3.19Differential equation of the CMOS inverter                                                 | 23 |

| 3.20Drain to bulk capacitance $(C_{db})$                                                       | 24 |

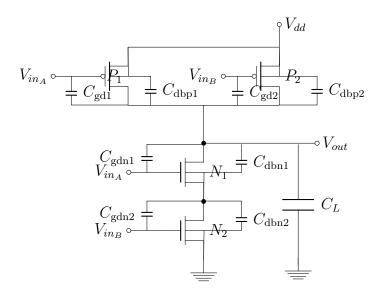

| 3.23<br>Drain current of nMOS $N_1$ of CMOS NAND2 at Level 2                                   | 31 |

| 3.24Drain current of nMOS $N_2$ of CMOS NAND2 at Level 2                                       | 31 |

| 3.25Drain current of pMOS $P_1$ of CMOS NAND2 at Level 2                                       | 33 |

| 3.26Drain current of pMOS $P_2$ of CMOS NAND2 at Level 2                                       | 33 |

| 3.27Differential equation of the CMOS NAND2                                                    | 33 |

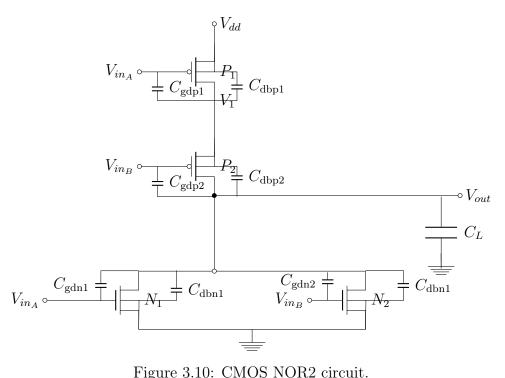

| 3.28Drain current of nMOS $N_1$ of CMOS NOR2 at Level 2                                        | 44 |

| 3.29Drain current of nMOS $N_2$ of CMOS NOR2 at Level 2                                        | 44 |

| 3.30Drain current of pMOS $P_1$ of CMOS NOR2 at Level 2                                        | 44 |

| 3.31Drain current of pMOS $P_2$ of CMOS NOR2 at Level 2                                        | 45 |

| 3.32Differential equation of the CMOS NOR2                                                     | 45 |

| 4.1 First-order body effect coefficient $(k_1)$                                                | 56 |

| 4.2 Second-order body effect coefficient $(k_2)$                                               | 56 |

| 4.3 Body effect coefficient near the surface $(\gamma_1)$                                      | 57 |

| 4.4 Body effect coefficient in the bulk $(\gamma_2)$                                           | 57 |

| 4.6 Short Channel Effect $(\Delta V_{\rm th})$                                                 | 57 |

| 4.7 Narrow Channel Effect                                                                      | 58 |

| 4.8 Mobility of carrier $(\mu_{\text{eff}})$                                                   | 58 |

### LIST OF EQUATIONS

| 4.9 Bulk charge effect $(A_{bulk})$                          | 58 |

|--------------------------------------------------------------|----|

| 4.10Channel Length Modulation $(V_{aclm})$                   | 59 |

| 4.11 Drain-Induced Barrier Lowering $(V_{adibl})$            | 59 |

| 4.12Threshold voltage equation at Level 49                   | 59 |

| 4.13Saturation voltage $(V_{dsat})$ at Level 49              | 60 |

| 4.15Linear Drain current equation of nMOS at Level 49        | 60 |

| 4.17Saturation Drain current equation of nMOS at Level 49    | 61 |

| 4.18Differential equation of the dual rail precharge circuit | 61 |

# List of Figures

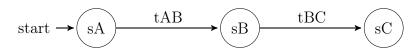

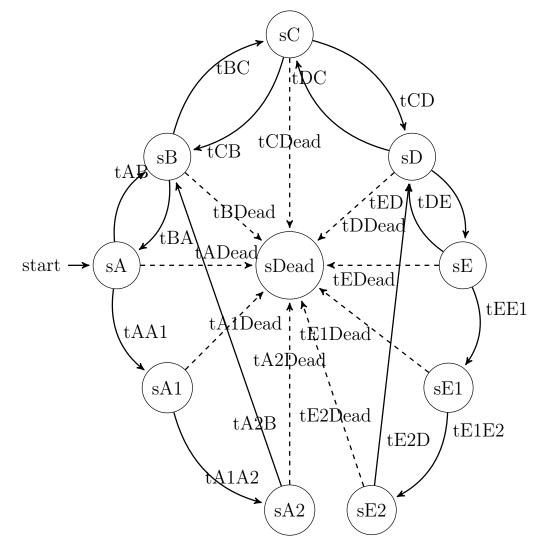

| 3.1  | State Diagram.                                                 | 12 |

|------|----------------------------------------------------------------|----|

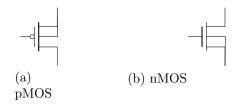

| 3.2  | MOS Transistors.                                               | 19 |

| 3.3  | CMOS inverter circuit.                                         | 20 |

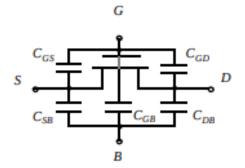

| 3.4  | MOSFET capacitance model.                                      | 24 |

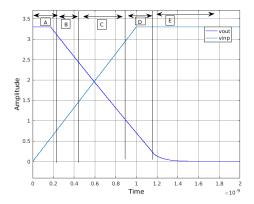

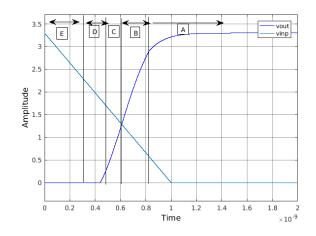

| 3.5  | Rising ramp input (CMOS inverter).                             | 25 |

| 3.6  | Falling ramp input (CMOS inverter).                            | 28 |

| 3.7  | Stateflow model of CMOS inverter.                              | 29 |

| 3.8  | CMOS NAND2 circuit.                                            | 30 |

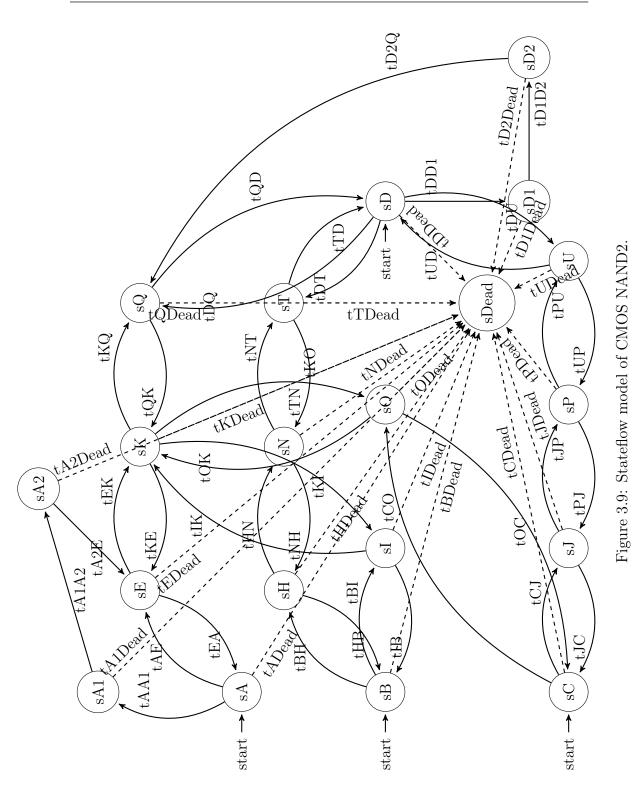

| 3.9  | Stateflow model of CMOS NAND2.                                 | 36 |

| 3.10 | CMOS NOR2 circuit.                                             | 42 |

| 3.11 | Stateflow model of CMOS NOR2                                   | 48 |

| 4 1  |                                                                | 00 |

| 4.1  | Design of the basic cell with top-bottom precharge logic [74]. | 62 |

| 4.2  | Stateflow model of secure circuit 1                            | 64 |

| 5.1  | Breach model                                                   | 72 |

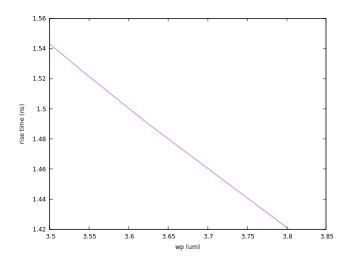

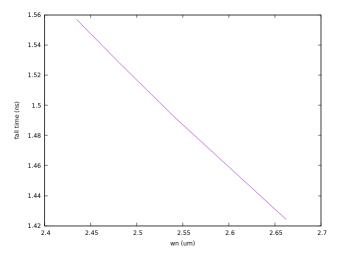

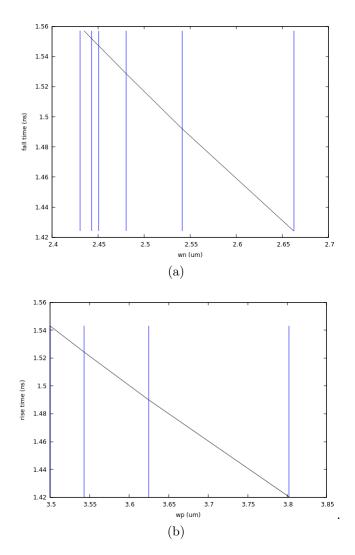

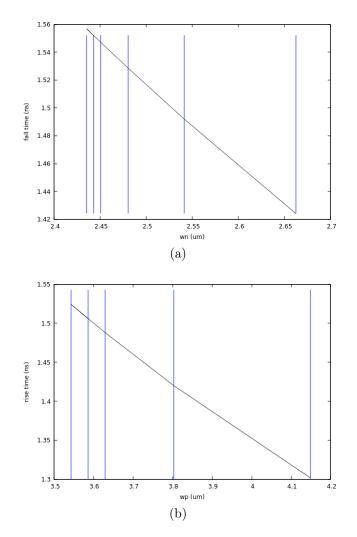

| 5.2  | pMOS transistor width $(\mu m)$ vs rise time (ns) of CMOS in-  |    |

| -    | verter for given nMOS transistor width $(\mu m)$               | 73 |

| 5.3  | nMOS transistor width $(\mu m)$ vs fall time (ns) of CMOS in-  |    |

|      | verter for given pMOS transistor width $(\mu m)$               | 74 |

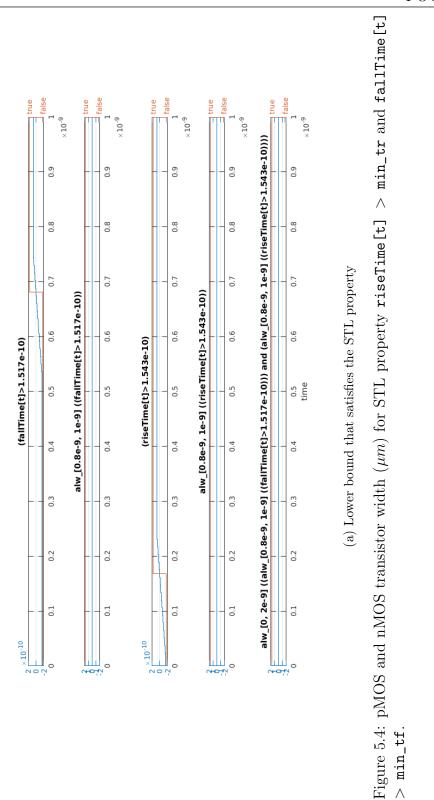

| 5.4  | pMOS and nMOS transistor width $(\mu m)$ for STL property      |    |

|      | riseTime[t] > min_tr and fallTime[t] > min_tf                  | 76 |

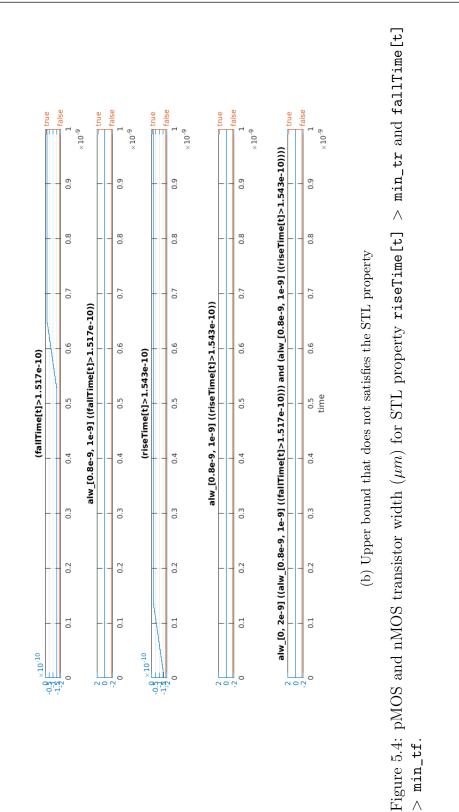

| 5.4  | pMOS and nMOS transistor width $(\mu m)$ for STL property      |    |

|      | riseTime[t] > min_tr and fallTime[t] > min_tf                  | 77 |

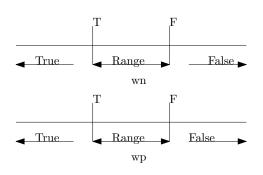

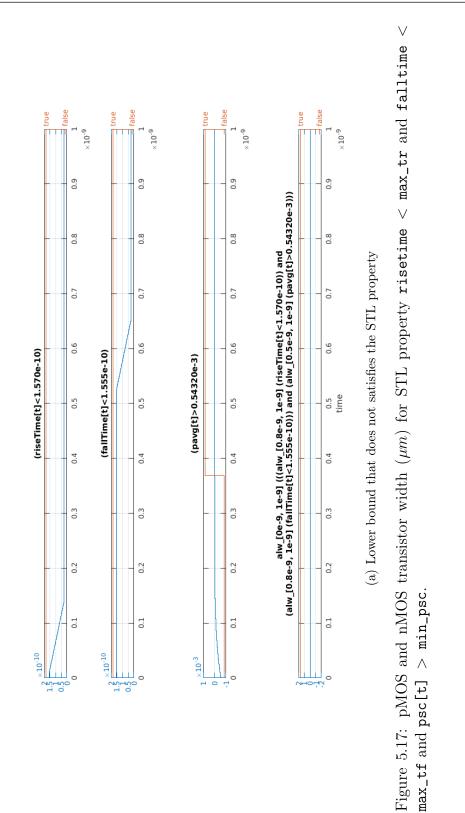

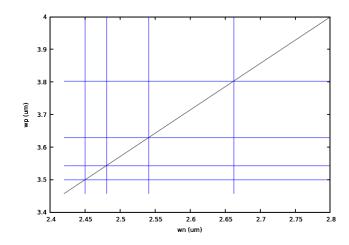

| 5.5  | Data range using Algorithm 1.                                  | 79 |

| 5.6  | 2D search for computation of rise time and fall time using     |    |

|      | Algorithm 2 for STL property riseTime[t] > min_tr and          |    |

|      | fallTime[t] > min_tf                                           | 80 |

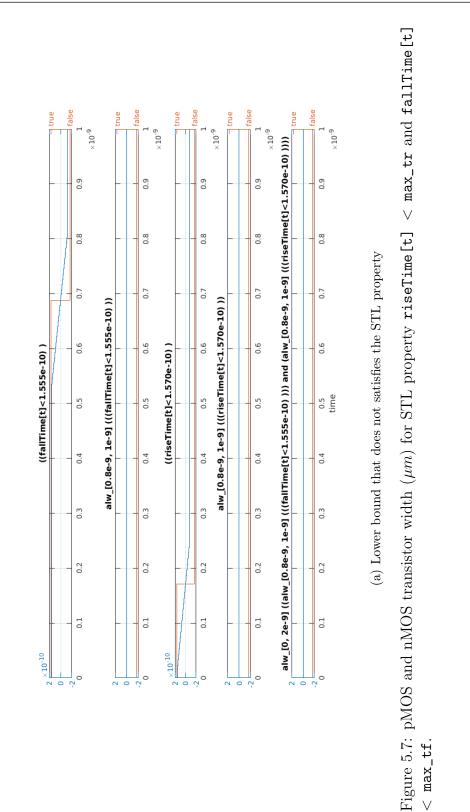

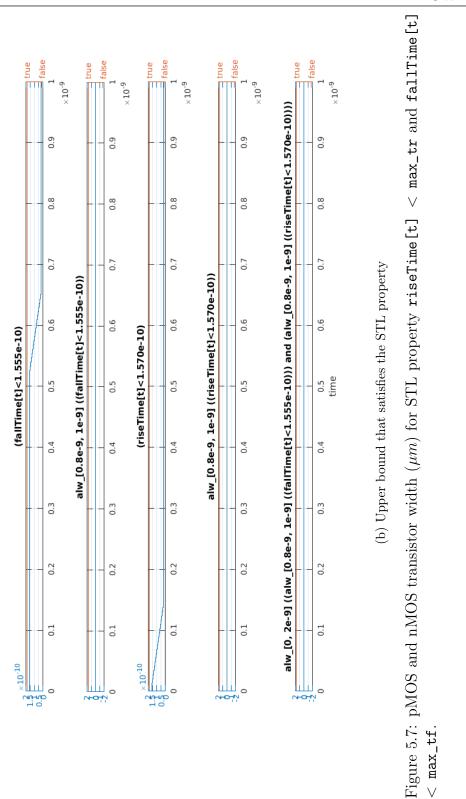

| 5.7  | pMOS and nMOS transistor width $(\mu m)$ for STL property      |    |

|      | riseTime[t] < max_tr and fallTime[t] < max_tf                  | 83 |

| 5.7  | pMOS and nMOS transistor width $(\mu m)$ for STL property      | _  |

|      | riseTime[t] < max_tr and fallTime[t] < max_tf                  | 84 |

|      | — — — — — —                                                    |    |

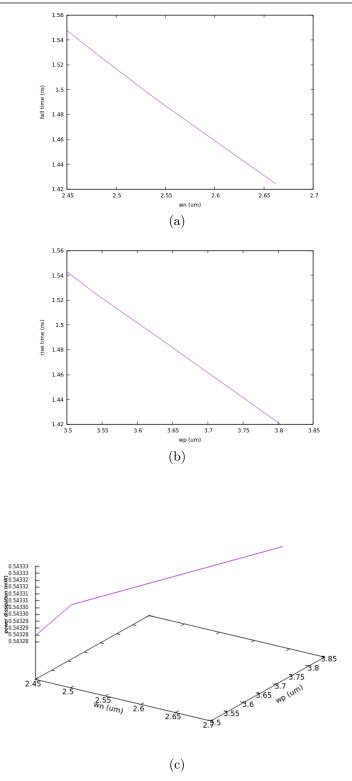

| 5.8  | 2D search for computation of rise time and fall time using                                 |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | Algorithm 2 for STL property riseTime[t] < max_tr and                                      |     |

|      | fallTime[t] < max_tf                                                                       | 85  |

| 5.9  | Transistor width $(\mu m)$ vs power dissipation (mW) of CMOS                               |     |

|      | inverter                                                                                   | 88  |

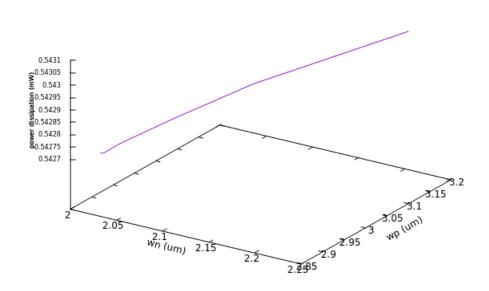

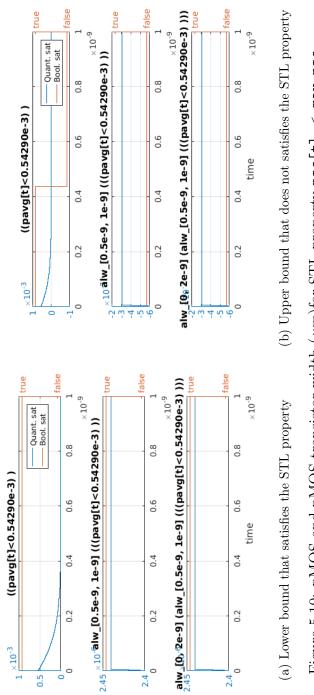

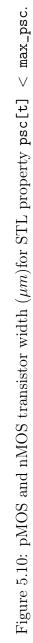

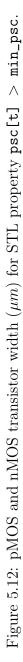

| 5.10 | pMOS and nMOS transistor width $(\mu m)$ for STL property psc[t]                           |     |

|      | < max_psc                                                                                  | 89  |

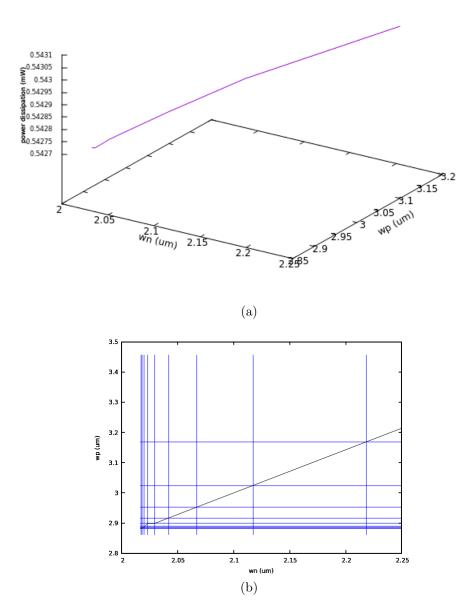

| 5.11 | 2D search for computation of power dissipation using Algo-                                 |     |

|      | rithm 2 for STL property psc[t] < max_psc                                                  | 91  |

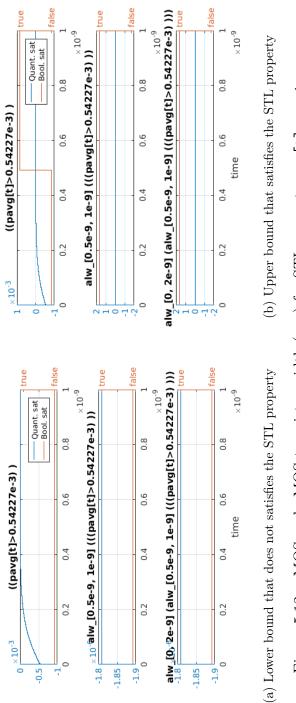

| 5.12 | pMOS and nMOS transistor width $(\mu m)$ for STL property                                  |     |

|      | psc[t] > min_psc                                                                           | 93  |

| 5.13 | 2D search for computation of power dissipation using Algo-                                 |     |

|      | rithm 2 for STL property psc[t] > min_psc                                                  | 95  |

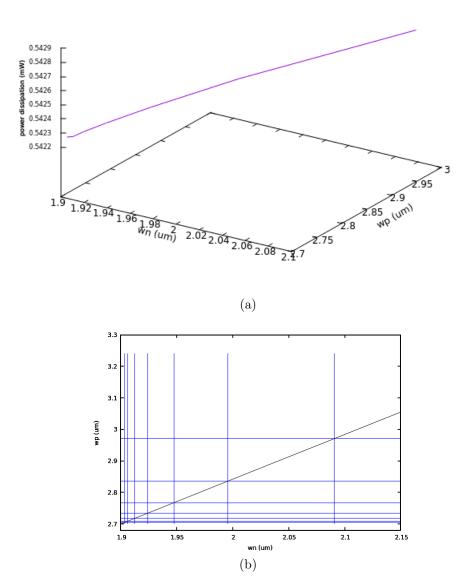

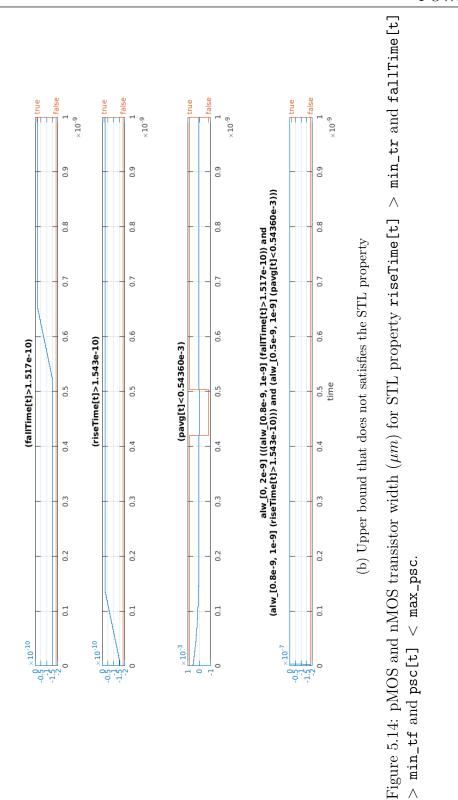

| 5.14 | pMOS and nMOS transistor width $(\mu m)$ for STL property                                  |     |

|      | <pre>riseTime[t] &gt; min_tr and fallTime[t] &gt; min_tf and psc[t</pre>                   | ;]  |

|      | < max_psc                                                                                  | 97  |

| 5.14 | pMOS and nMOS transistor width $(\mu m)$ for STL property                                  |     |

|      | <pre>riseTime[t] &gt; min_tr and fallTime[t] &gt; min_tf and psc[t</pre>                   | ;]  |

|      | < max_psc                                                                                  | 98  |

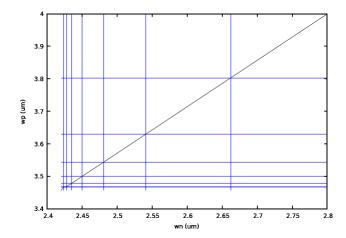

| 5.15 | 2D search for computation of rise time and fall time and power                             |     |

|      | dissipation using Algorithm 2 for STL property riseTime[t]                                 |     |

|      | $> \min_{tr} and fallTime[t] > \min_{tf} and psc[t] < \max_{psc}$                          |     |

| 5.16 | Objective function with respect to transistor width $(w_n \text{ and } w_p)$ .             | 101 |

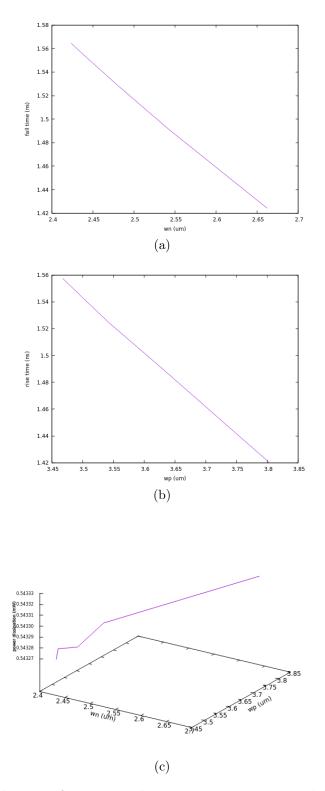

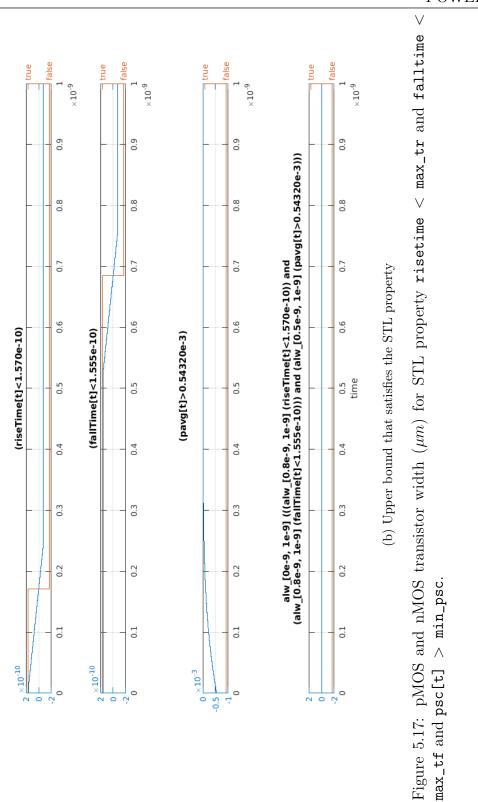

| 5.17 | pMOS and nMOS transistor width $(\mu m)$ for STL property                                  |     |

|      | <pre>risetime &lt; max_tr and falltime &lt; max_tf and psc[t]</pre>                        |     |

|      | > min_psc                                                                                  | 103 |

| 5.17 | pMOS and nMOS transistor width $(\mu m)$ for STL property                                  |     |

|      | <pre>risetime &lt; max_tr and falltime &lt; max_tf and psc[t]</pre>                        |     |

|      | > min_psc                                                                                  | 104 |

| 5.18 | 2D search for computation of rise time and fall time and power                             |     |

|      | dissipation using Algorithm 2 for STL property risetime $<$                                |     |

|      | $max_tr and falltime < max_tf and psc[t] > min_psc.$                                       | 105 |

| 5.19 | Objective function with respect to transistor width $(w_{\rm n} \text{ and } w_{\rm p})$ . | 106 |

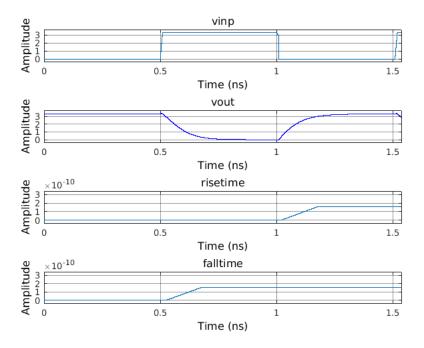

| 61   | Output of CMOS invertor $(0.25 \text{ upp} V = 2.2 \text{ V})$                             | 110 |

| 6.1  | Output of CMOS inverter $(0.35 \ \mu m, V_{dd} = 3.3 \ V)$                                 |     |

| 6.2  | Output of CMOS NAND2 (0.35 $\mu m$ , $V_{dd} = 3.3$ V)                                     |     |

| 6.3  | Output of CMOS NOR2 (0.35 $\mu m$ , $V_{dd} = 3.3$ V)                                      |     |

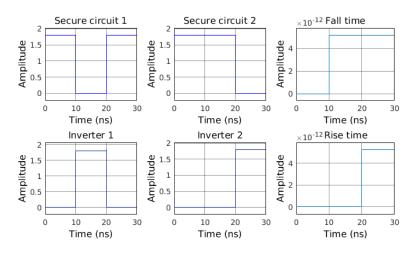

| 6.4  | Output of Secure circuit (180 nm, $V_{dd} = 1.8$ V)                                        | 122 |

## List of Tables

| 3.1  | Three Modes of Operation of Transistor                                                                                                                            |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2  | MOSFET Gate capacitance                                                                                                                                           |

| 3.3  | Operating regions of pMOS and nMOS transistors of CMOS                                                                                                            |

|      | inverter                                                                                                                                                          |

| 3.4  | Truth table of CMOS NAND2                                                                                                                                         |

| 3.5  | Operating regions of pMOS and nMOS transistor of CMOS                                                                                                             |

|      | NAND2                                                                                                                                                             |

| 3.6  | Truth table of CMOS NOR2                                                                                                                                          |

| 3.7  | Operating regions of pMOS and nMOS transistor of CMOS                                                                                                             |

| 0.1  | NOR2 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $33$                                                                                 |

|      |                                                                                                                                                                   |

| 4.1  | Operating regions of pMOS and nMOS transistors of secure                                                                                                          |

|      | circuit                                                                                                                                                           |

|      |                                                                                                                                                                   |

| 6.1  | Compution time                                                                                                                                                    |

| 6.2  | Results of CMOS inverter for rise time and fall time compu-                                                                                                       |

|      | tation $(0.35 \ \mu m, V_{dd} = 3.3 \ V)$                                                                                                                         |

| 6.3  | Results of CMOS inverter for power computation (0.35 $\mu m$ ,                                                                                                    |

|      | $V_{\rm dd} = 3.3 {\rm V})$                                                                                                                                       |

| 6.4  | Results of CMOS inverter for rise time and fall time and power                                                                                                    |

|      | computation (0.35 $\mu m$ , $V_{dd} = 3.3 \text{ V}$ )                                                                                                            |

| 6.5  | Results of CMOS NAND2 for rise time and fall time compu-                                                                                                          |

|      | tation (0.35 $\mu m$ , $V_{dd} = 3.3$ V)                                                                                                                          |

| 6.6  | Results of CMOS NAND2 for computation of power (0.35 $\mu m$ ,                                                                                                    |

|      | $V_{\rm dd} = 3.3 \text{ V}) \dots \dots$                   |

| 6.7  | Results of CMOS NAND2 for rise time and fall time and power                                                                                                       |

| 0.1  | computation (0.35 $\mu m$ , $V_{dd} = 3.3$ V) $\dots \dots \dots$ |

| 6.8  | Results of CMOS NOR2 for rise time and fall time computa-                                                                                                         |

| 0.0  | tion $(0.35 \ \mu m, V_{dd} = 3.3 \text{ V})$                                                                                                                     |

| 6.9  | Results of CMOS NOR2 for power computation (0.35 $\mu m$ ,                                                                                                        |

| 0.9  | $V_{\rm dd} = 3.3 \text{ V})$                                                                                                                                     |

| 6 10 |                                                                                                                                                                   |

| 6.10 | Results of CMOS NOR2 for rise time and fall time and power $(0.25 - V - 2.2 N)$                                                                                   |

|      | computation (0.35 $\mu m$ , $V_{dd} = 3.3 \text{ V}$ )                                                                                                            |

| 6.11 Results of CMOS secure circuit for rise time and fall time                     |

|-------------------------------------------------------------------------------------|

| computation (180 nm, $V_{dd} = 1.8 \text{ V}$ )                                     |

| 6.12 Results of CMOS secure circuit for rise time and fall time                     |

| computation (180 nm, $V_{dd} = 1.8 \text{ V}$ )                                     |

| 6.13 Spice results vs NM results of CMOS inverter for rise time and                 |

| fall time computation (0.35 $\mu m$ , $V_{dd} = 3.3$ V) $\dots \dots 126$           |

| 6.14 Spice results vs 2D search results of CMOS inverter for rise                   |

| time and fall time computation (0.35 $\mu m$ , $V_{\rm dd} = 3.3$ V) $\ldots$ 127   |

| 6.15 Spice results vs NM results of CMOS NAND2 for rise time                        |

| and fall time computation (0.35 $\mu m$ , $V_{\rm dd} = 3.3$ V) $\ldots \ldots 128$ |

| 6.16 Spice results vs 2D search results of CMOS NAND2 for rise                      |

| time and fall time computation (0.35 $\mu m$ , $V_{\rm dd} = 3.3$ V) $\ldots$ 129   |

| 6.17 Spice results vs Nelder mead results of CMOS NOR2 for rise                     |

| time and fall time computation (0.35 $\mu m$ , $V_{\rm dd} = 3.3$ V) $\ldots$ 130   |

| 6.18 Spice results vs 2D search results of CMOS NOR2 for rise time                  |

| and fall time computation $(0.35 \ \mu m, V_{dd} = 3.3 \ V)$                        |

| 6.19 Spice results vs NM results of CMOS secure circuit for rise                    |

| time and fall time computation (180 nm, $V_{dd} = 1.8 \text{ V}$ )                  |

| 6.20 Spice results vs 2D search results of CMOS secure circuit for                  |

| rise time and fall time computation (180 nm, $V_{\rm dd} = 1.8~{\rm V})~$ 133       |

|                                                                                     |

# Chapter 1 Introduction

The most important component in today's microelectronics is the transistor. MOSFET transistors are designed as pMOS and nMOS transistors. For semiconductor devices the equivalent circuit model elements are highly nonlinear and element values are strongly dependent on DC bias, frequency, signal level and temperature. Therefore, the first step is the accurate modelling of the behaviour of the circuit on which suitable analysis can be carried out. In general there are three types of circuit models- DC models, transient models and AC models. These circuit models correspond to three basic types of circuit analysis: i) A DC model is a static model which evaluates the device current for a fixed voltage, not varying with time. Thus in a DC model dynamic effects such as time delay arising from the presence of energy-storage elements i.e. capacitors are ignored. *ii*) A transient model is a large-signal dynamic model that evaluates the device current when the applied voltage is varying with time. Dynamic effects arising from the charging or discharging of device storage elements, usually capacitances are included. *iii*) An AC model is a small-signal model that evaluates the current when the applied voltage variation is so small that the resulting small current variations can be expressed using linear relations. The small signal linear model is obtained from the DC model of the device. AC model is used for the frequency-domain analysis. In this work, the MOSFET models that are concerned with is the transient model and contains only capacitances as the storage elements. The performance of a device can be described in terms of mathematical equations, considering theoretical or empirical methods, or both can be used to derive a model. Physical, environmental, and operational conditions influence strongly the device characteristics. A few model parameters along with the characterization can be used to build a desired model.

Highly advanced models exist to handle deep submicron circuits [1]. However, for demonstrating the techniques developed in this work, Spice level 2 and BSIM3v3 level 49 model of MOS transistor is considered towards developing the analytical methods. There are two types of analytical models where model equations are directly derived from device physics. One type of model is based on surface potential analysis known as charge sheet models [2,3]. These models are inherently continuous in all regions of operation of the device. The current can be accurately determined using these models, but the equations themselves are complex, thus not very suitable for circuit simulation. The second type of analytical model is the result of applying various approximations to the semiconductor equations, based upon decisions as to which physical phenomena dominate [4-6]. Thus different equations are used to represent different regions of operation of the device. The level 2 model is a second-order model of MOS device behavior and BSIM3v3 level 49 is the higher order model. Based on such second-order behavior model of MOS devices, the output waveform of a CMOS inverter driven by a step input has been reported by [7]. The accuracy of the device depends on the equations governing the behaviour of the MOSFETs at different regions and also the influence of the various model parameters. Therefore after modelling the device accurately, the second step is the parameter optimisation.

The rest of the chapter is organized as follows. Section 1.1 deals with motivation of the present work. Section 1.2 gives an overview of the present research work and highlights the specific contributions of the thesis. Finally, Section 1.3 outlines the organization of the rest of the thesis.

### 1.1 Motivation

Simulation is considered to be essential because conducting a complex experiment is often challenging. For instance, the computer simulation process simulates an electronic circuit, where we describe the entire circuit with a mathematical description through mathematical equations. MATLAB Simulink is one of the widely used industrial tools. It helps in modelling systems, even if they are more complex. The resulting model must be tested to detect the completeness of the model. But, such a model consists of many blocks, so the testing process becomes complex. So we have to decrease the complexity of the models to handle large models and ensure the complex models' quality. Therefore, the Stateflow designing tool of MATLAB is used to model, simulate, and analyze systems to capture the systems' event-driven behavior. Event-driven systems where the system makes a transition from one state to another state based on transition condition. Thus it confirms the completeness of the system if all accepting states in a system are reachable. The mathematical equations are a function of parameters that configures the mathematical model to describe the dependence of the output signal. The parameter values have to be determined from a known data set using a technique called parameter optimisation.

Circuit optimisation, by way of transistor resizing and selection of other design parameters, to achieve multiple objectives is an important design goal [8]. Optimisation of design metrics such as rise time, fall time and power are important objectives for modelling CMOS circuits. The parameter optimisation requires measurements of several device parameters along with different combinations of length and width of the device (nMOS and pMOS). There is a functional relationship between device parameters and design objectives. For instance, power dissipation is related to transistor size (width, length) and load capacitor. Rise time and fall time are dependent on output capacitor and on-resistance, which need to be minimized for faster switching [9]. On-resistance of transistor can be minimized by increasing the W/L ratio of the transistor.

### **1.2** Overview and Contributions of the Thesis

In this work, modelling of CMOS circuits has been done in the Matlab environment by using Simulink/Stateflow designing tool and parameter optimisation using the Breach toolbox. Matlab Simulink is a modelling tool that includes Stateflow [10]. Stateflow has been studied for formal modelling [11] [12] and verification [13]. Signal temporal logic (STL) [14] formulas are used to specify the desired properties of continuous signals determining the parameters of the underlying model. Breach [15] is an analytic toolbox of Matlab which can be used to monitor and analyze the transient behavior of model based systems. Breach estimates dense sets that are reachable by the model based on simulation [16]. Breach works on STL properties [17] for a given Stateflow model and returns *false* (0), if no satisfying trace can be found; otherwise, *true* (1) is returned.

#### 1.2.1 Contribution

An attempt has been made to utilise problem-specific features to achieve an efficient transistor sizing technique to achieve design objectives. This work has three contributions as listed below.

• Simulink Stateflow (hybrid system) modelling of transistor operation of CMOS inverter, CMOS NAND2 and CMOS NOR2 at Spice level 2 and checking the completeness of the model through reachability analysis. The designed model is comparable with respect to the real circuit simulation results and execution time is fast.

- Simulink Stateflow (hybrid system) modelling of transistor operation of precharge based logic circuits at BSIM3v3 level 49 and checking the completness of the model. The model designed using Stateflow simulink is comparable with respect to the real circuit simulation results and execution time is fast.

- Formulation of desired circuit performance required using STL properties to capture desired properties (rise time, fall time and power). Parameter determination (transistor sizing) to achieve performance goals using the Breach tool; Nelder mead (NM) algorithm and the presented two dimensional (2D) search algorithm has been used to compare the parameters more efficiently. Using 2D search algorithm, it is possible to obtain a range of parameters with less computation time as compared to NM algorithm. The CMOS circuits are created using spice with optimised values of transistor width achieved through NM algorithm and 2D search algorithm to verify the stateflow model.

### 1.3 Organization of the rest of the Thesis

This section presents an outline of the organization of the rest of the thesis. **Chapter 2:** Survey of literature has been presented that led to the motivation behind the present work.

**Chapter 3:** Hybrid Modelling of CMOS circuits (CMOS inverter, CMOS NAND2, and CMOS NOR2) as a hybrid system at spice Level 2 has been done in the Matlab environment using Simulink/Stateflow design tool. Reachability analysis has been done to confirm that the dead state is unreachable from the initial state and confirm the completeness of the model.

**Chapter 4:** Hybrid modelling of the dual-rail precharge circuit as a hybrid system at BSIM3v3 Level 49 have been done in the Matlab environment using Simulink/Stateflow design tool. For checking the completeness of a model, reachability analysis has been done and to confirm that the dead state is unreachable from the initial state.

**Chapter 5:** Formulation of desired circuit performance requires using STL formula and parameter determination to achieve performance goals using Breach tool, which attempts to find a set of parameters using the Nelder-Mead (NM) algorithms in the given ranges. The presented two dimensional (2D) search algorithm has been used to compare the parameters more efficiently.

**Chapter 6:** Experimental results are provided to demonstrate the effectiveness of the methodology. To verify the results achieved through the NM algorithm and proposed 2D search algorithm, the CMOS circuits have been redesigned with synthesized values of output load capacitance and transistor size using Spice simulator.

**Chapter 7 :** The contributions of this thesis are summarized in this chapter.

# Chapter 2 Literature Survey

In this chapter, we present a comprehensive survey of the literature related to the following topics (i) modeling of digital circuits, (ii) rise time and fall time and power dissipation and (iii) optimisation techniques.

### 2.1 Modelling of Digital Circuits

Before the actual fabrication of a designed circuit, the circuit performance should be predicted and evaluated. A better modeling is needed to predict and evaluate the behavior of the circuit [18]. The analytical response derived by Kayssi *et al.* [19] is based on first-order model of MOS device behavior where the second-order phenomena including carrier velocity saturation effect, the carrier mobility degradation and weak inversion are kept suppressed. The models are designed using mathematical equations to improve and predict the real time behaviour of the transistors [20]. Karlsson *et al.* [21] has presented linear region model parameters of submicron transistors and neglected the parameters at saturation region. An analytical models to describe the propagation delay and the power consumption of the CMOS inverter in closed mathematical forms using nanometer MOS transistors has been proposed by Chaourani et al. [22]. However, in this models the current of the short-circuiting transistor has been neglected and uses simplified transistor current expressions. Consoli et al. [23] has reported piecewise linear approximation and handles only nine parameters. Other analytical models which employ heavy approximations and still several physical effects i.e. channellength modulation, drain-induced barrier lowering were neglected [24]. Sheu et al. [25] has reported a model where the second order mobility reduction factor is neglected. The behaviours of a circuit depend on the transistor channel length and width through complex high orders of equations. For a complex circuit, the relationships between the design parameters and the performance parameters becomes complicated [26] [27]. The design of nano scale CMOS inverter using 45 nm Berkeley Predictive Technology model parameters [28] for simulation as well as for evaluating the cost function using PSO is reported by [29]. The transistor geometries (the channel length and channel width) are considered to be the design parameters and form the design space which is to be explored in order to obtain an optimal solution point [30]. In [31], an improved analytical propagation delay model has been presented, but it neglects the channel length modulation effect, which is important for deep submicron technologies. The MOSFET threshold voltage  $(V_{\rm th})$  is an essential device parameter. For an accurate design, its value must be hold within certain limits and thus it is important that  $V_{\rm th}$  be modeled accurately [32]. A two - dimensional analytical solution was devoloped by using the charge sharing approach [33] or simplifying Poisson's equation in the depletion region [34] [35]. They used simple geometrical division of the depletion layer in the substrate to derive the expressions of threshold voltage.

Dual-Rail Logic [36] [37] is a pre-charged based circuit technique which is used to improve the speed of CMOS circuits.

In this work, stateflow modelling of complex circuits considering the short channel effects of MOS transistor using Spice level2 and BSIM3v3 level 49 will be taken into account for higher accuracy modelling of short-channel devices.

### 2.2 Rise Time and Fall Time and Power Dissipation

CMOS circuits can be optimized in a number of ways, such as device model selection, and transistor sizing. For a given technology, a small change in the transistor size leads to a remarkable change in the characteristics of a circuit. Therefore, an appropriate transistor sizing method is necessary for acceptable circuit performance. So, to achieve the best circuit performance one should attempt to minimize power and minimize delay where both power and delay parameters are functions of the transistor size. For a certain technology, the channel lengths of all transistors are fixed at the minimal feature size [38]. So, the only variable to be optimized is the channel width of each transistor. Several approaches have been applied in transistor sizing, one being a mathematical optimisation method [39] [40]. In this method, the transistor sizing problem is formulated as a constrained nonlinear mathematical program. Two algorithms, MDE (Minimum Delay Estimation) and ADC (Area-Delay Curve), are based on logical effort. Once the delay is optimized using MDE algorithm, the ADC algorithm optimizes area-delay product. Hence, in these algorithms the delay performance is the target parameter and power is not optimized. The work [41] shows how these algorithms can size the transistors without running a heuristic sizing tool by calculating the minimum achievable delay and the cost of achieving a target delay. A transistor sizing tool for speed, area, and power optimisation of static CMOS circuits is reported by Dutta *et al.* [42].

The first analytical expressions for the output waveform including the effect of the input slope were presented by Hedenstiema *et al.* [43], where the influence of short circuit current was neglected. These expressions were extended by Kayssi *et al.* [19] for the exponential input waveform, step input and ramp input, but still short circuit current was not included. The differential equation that describes the discharge of the load capacitor was solved for a rising input ramp considering the currents through both transistors [44]. However, in the case where the nMOS device is saturated and the PMOS device is in the linear region, the quadratic term of the current through the pMOS device was neglected. Vemuru *et al.* [45] derived an expression for the output waveform, which includes this term of the pMOS current, using a power series to approximate the solution of the differential equation. However, only the first five terms of the series were calculated, and a recursion form for the calculation of higher order terms in order to obtain better accuracy, was not considered.

The power dissipation is a strong function of transistor sizing which affects capacitance. Thus, sources of power consumption such as short-circuit currents can be minimized by designing circuit and transistor sizing accurately. Transistor sizing also affects time constant of the gate due to the parasitic capacitors. Veendrick *et al.* report a scheme for short circuit power [46] based on the Shichman and Hodges model [47]. However, they do not consider the load capacitance. Bisdounis *et al.* [48] includes the load capacitance into account but rely on a long channel model of the transistor. In this work the scheme presented by Chatzigeorgiou *et al.* [49] has been used which takes the load capacitance into account. Low-power design is an important objective for which transistor sizing in a static CMOS layout may be utilised [50]. Low power CMOS digital design with optimal supply voltage and transistor sizing is reported by Anantha et al. [51], where they argue that smallest possible W/L ratios minimise power dissipation.

In this work, the channel length of all transistors are kept fixed. Transistor width is optimized such that minimum rise time, minimum fall time and minimum power are achieved.

### 2.3 Optimisation techniques