### DESIGN OF POWER ATTACK RESISTANT CIRCUITS FOR

### CRYPTOGRAPHY

### DESIGN OF POWER ATTACK RESISTANT CIRCUITS FOR

#### CRYPTOGRAPHY

Thesis submitted in partial fulfillment of the requirements for the award of the degree

of

#### **Masters in Science**

by

### Partha De

Under the supervision of

### Dr. Chittaranjan Mandal

### **Department of Computer Science and Engineering**

Indian Institute of Technology, Kharagpur

August 2014

© 2014 Partha De. All Rights Reserved.

### **APPROVAL OF THE VIVA-VOCE BOARD**

Certified that the thesis entitled "**Design of Power Attack Resistant Circuits for Cryptography**," submitted by **Partha De** to the Indian Institute of Technology, Kharagpur, for the award of the degree of Master In Science has been accepted by the external examiners and that the student has successfully defended the thesis in the viva-voce examination held today.

Prof Dpankar Sarkar (Member of the DAC)

Prof Anupam Basu (Member of the DAC) Prof Santanu Chattopadhay (Member of the DAC)

Prof Chittaranjan Mandal (Supervisor)

(External Examiner)

(Chairman)

Date:

### ACKNOWLEDGMENTS

I would like to express my heartiest gratitude to my thesis supervisor Prof Chittaranjan Mandal for guiding me through the Master in Science program. I acknowledge his constant technical and moral support and guidance throughout my MS period. At the time of joining, I was a novice in the field of VLSI, but in the course of my work, I have learned a lot about the art of conducting research, solving problems, designing circuits, using complex cad tools and art of taping-out IC from my supervisor. I consider myself extremely lucky for getting the opportunity to work under him. I would also express my thanks to Prof Debdeep Mukhopadhay for helping me in my work.

I want to thank my lab mates Aritra, Antara, Kunal, Sandipan, Chandan, Rajoshree, Subhadip, Tamal, Satya Goutam, Dhiman Gargi, Devleena, Sudipda, Maunendra, Sumana, Arindam, Shiladitya, Soumyadeep and Debjit for making the laboratory environment most enjoyable. Special thanks go to Kunal for his association with my work.

I also thank Sayan, Santa, Debasis Kundu, Sankar for making my stay in Kharagpur extremely memorable. I also thanks to D-304 mess for taking care of my food habits. Special thanks to Bappa, Prasun-da, Durga-da and Sibu-da for their assistance in the laboratories.

I also thank my brother Papai who stays home and taking care of our parents. Last but not the least, I express my gratitude to my parents who has sacrificed much and provided me continuous support and encouragement without which I could not come out with this work. I would also like to thank my family members for their encouragement and for the confidence they reposed on me.

Partha De

## Indian Institute of Technology Kharagpur

Certificate by the Supervisor

Date: 20-08-2014

This is to certify that the thesis entitled,

#### "Design of Power Attack Resistant Circuits for Cryptography"

submitted by PARTHA DE(10CS70P03) to the Indian Institute of Technology Kharagpur, is a record of bonafide research work carried under my supervision and is worthy of consideration for the award of the Master of Science of the Institute.

Signature of the Supervisor(s):

Prof. CHITTARANJAN MANDAL

COMPUTER SCIENCE & ENGINEERING

### Indian Institute of Technology Kharagpur

**Declaration by the Student**

Date: 20-08-2014

Title of the Thesis:

Design of Power Attack Resistant Circuits for Cryptography

I Certify that

a. the work contained in the thesis is original and has been done by me under the guidance of my Supervisor;

b. the work has not been submitted to any other Institute for any degree or diploma;

c. I have followed the guidelines provided by the Institute in preparing the thesis;

d. I have conformed to ethical norms and guidelines while writing the thesis and;

e. whenever I have used materials (data, models, figures, and text) from other sources, I have given due credit to them by citing them in the text of the thesis, giving their details in the references, and taking permission from the copyright owners of the sources, whenever necessary.

Signature of the Student: \_\_\_\_\_

Name of the Student: PARTHA DE (10CS70P03)

#### ABSTRACT

Power analysis attacks (PAAs) have been found to be extremely effective on cryptographic systems to derive the cryptographic secrets from these traces.

In this work, Binary Decision Diagram (BDD) based dual-rail logic circuit schemes have been developed to counter power analysis attacks (PAAs). The hallmark of our circuit schemes is that an identical number of switchings is ensured on each circuit path. The transistors are interconnected to create pull-up and pull-down paths to outputs by way of binary decisions based on the input variables, so as to realise the required Boolean function. This principle of operation has directly permitted the use of BDD based logic synthesis to design the required pull-up and pull-down networks of transistors. The operation of these circuit schemes feature novel pre-charge generation, voltage scaling with leakage power minimization and early propagation effect resistance mechanism. In particular, we have developed and explored top pre-charging, top-bottom pre-charging, bottom pre-charging and symmetric NMOS bottom pre-charging logics. A simple synthesis algorithm for mapping a given Boolean functions to such BDD based circuits is also presented.

Extensive experimentation has been carried out to establish resistance of our circuits to PAAs. Objective of the experimentation is two fold, to demonstrate resistance to power attacks and to highlight the low power characteristics. Towards the first objective, differential power attacks such as, difference of mean (DoM) and correlation power attack (CPA) have been carried out. Resilience to the the early propagation effect (EPE) is also demonstrated. Six 2-input basic cell and two  $4 \times 4$  S-boxes are used for experimental benchmark. Experimental results on circuits with bottom pre-charge logic demonstrate a significant reduction by 99.68% and 88.55% in peak power variance (PPV) over two chosen competing designs, for the basic cell. The reduction in PPV is recorded to be greater than 99.9% for the S-box implementations for both those design. A reduction of about 30% to 67% in both average power and average current consumption is observed while comparing with the chosen techniques. Experimental results on circuits with various other features such as top pre-charge and top-bottom pre-charge also demonstrate a large reductions in PPV. Significant reduction for average power and average current for both the pre-charge logics is also achieved. Circuits using top-pre charging required less transistors and demonstrated lower PPV in comparison with others. Symmetric NMOS bottom pre-charge logic was more resilient to EPE due to its symmetric nature. Bottom pre-charge and symmetric NMOS bottom pre-charge logic were also effective in avoiding timing attacks along with top-bottom pre-charge logic.

**Keywords:** Side channel attack; Power analysis attack; Binary Decision Diagram; Early propagation effect; Voltage scaling; Pre-charge logic;

# Contents

| Та | Table of Contentsxv |                                                         |        |  |  |

|----|---------------------|---------------------------------------------------------|--------|--|--|

| Li | st of I             | Figures                                                 | xix    |  |  |

| Li | st of ]             | Tables x                                                | xiii   |  |  |

| 1  | <b>Intr</b><br>1.1  | oduction Motivation                                     | 1<br>5 |  |  |

|    | 1.2                 | Problem statement                                       | 6      |  |  |

|    | 1.3                 | Summary of contributions                                | 6      |  |  |

|    | 1.4                 | Thesis outline                                          | 8      |  |  |

| 2  | Prel                | iminaries                                               | 11     |  |  |

|    | 2.1                 | BDDs and ROBDDs                                         | 11     |  |  |

|    | 2.2                 | ASIC design flow                                        | 15     |  |  |

|    |                     | 2.2.1 Full custom design flow                           | 16     |  |  |

|    |                     | 2.2.2 Semi-custom design flow                           | 16     |  |  |

|    | 2.3                 | Pass transistor logic                                   | 18     |  |  |

|    | 2.4                 | Power consumption of CMOS logic                         | 19     |  |  |

|    | 2.5                 | Vulnerability of cryptosystems to side channel attacks  | 21     |  |  |

|    |                     | 2.5.1 Symmetric-Key encryption                          | 21     |  |  |

|    |                     | 2.5.2 Asymmetric-Key encryption                         | 23     |  |  |

|    | 2.6                 | Side channel attacks on cryptographic devices           | 24     |  |  |

|    | 2.7                 | Side channel attacks                                    | 25     |  |  |

|    |                     | 2.7.1 Differential power analysis                       | 26     |  |  |

|    |                     | 2.7.2 Difference of means method                        | 27     |  |  |

|    |                     | 2.7.3 Correlation power analysis                        | 28     |  |  |

|    |                     | 2.7.4 Early propagation effect                          | 28     |  |  |

| 3  | Basi                | c BDD based circuits with bottom pre-charge             | 31     |  |  |

|    | 3.1                 | Basic BDD based circuits with bottom pre-charge         | 32     |  |  |

|    |                     | 3.1.1 Pre-charge generation logic                       | 32     |  |  |

|    |                     | 3.1.2 BDD based tree network to realize logic functions | 37     |  |  |

|    |                     | 3.1.3 Swing restoration logic                           | 38     |  |  |

|   |      | 3.1.4    | Voltage scaling and leakage power minimization               | 39  |

|---|------|----------|--------------------------------------------------------------|-----|

|   |      | 3.1.5    | Circuit synthesis of bottom pre-charge logic by combining    |     |

|   |      |          | four aspects                                                 | 39  |

|   |      | 3.1.6    | Synthesis of symmetric NMOS based bottom pre-charge logic    |     |

|   |      |          | by combining four aspects                                    | 40  |

|   | 3.2  |          | ations of bottom pre-charge logic                            | 40  |

|   |      | 3.2.1    | Basic cell design using bottom pre-charge logic              | 41  |

|   |      | 3.2.2    | Adder design with bottom and BDD based pre-charge logic .    | 42  |

|   | 3.3  |          | ations of symmetric NMOS based pre-charge logic              | 45  |

|   |      | 3.3.1    | Basic cell design with symmetric NMOS based pre-charge logic | 46  |

|   |      | 3.3.2    | BDD based S-box design symmetric NMOS based pre-charge       |     |

|   |      |          | logic                                                        | 47  |

|   | 3.4  | Conclu   | sion                                                         | 48  |

| 4 | BDD  | ) based  | circuits with various other features                         | 57  |

|   | 4.1  | BDD b    | ased circuits with various other features                    | 58  |

|   |      | 4.1.1    | Pre-charge generation logic design                           | 58  |

|   |      | 4.1.2    | BDD based tree network to realize logic functions            | 61  |

|   |      | 4.1.3    | Voltage scaling and leakage power minimization               | 63  |

|   | 4.2  | Applic   | ations of BDD based logic with top-bottom pre-charge         | 64  |

|   |      | 4.2.1    | BDD based basic cell design                                  | 64  |

|   |      | 4.2.2    | BDD based S-box designs with top-bottom pre-charge logic .   | 65  |

|   | 4.3  | Applic   | ations of BDD based logic with top pre-charge                | 67  |

|   |      | 4.3.1    | Basic Cell design using top pre-charge logic                 | 68  |

|   |      | 4.3.2    | BDD based S-box designs with top pre-charge logic            | 69  |

|   | 4.4  | Conclu   |                                                              | 70  |

| 5 | Auto | omated s | synthesis scheme                                             | 75  |

| - | 5.1  |          | atic synthesis of Verilog code                               | 75  |

|   | 5.2  |          | ning the large BDDs                                          | 80  |

|   | 5.3  |          | ated synthesis of AES                                        | 82  |

|   | 5.4  | Conclu   |                                                              | 84  |

| _ |      |          |                                                              |     |

| 6 | -    |          | al results with different process technology                 | 89  |

|   | 6.1  | -        | mentation for bottom-pre charge logic in 180 nm technology.  | 91  |

|   | 6.2  | -        | mentation for bottom-pre charge logic in 65 nm technology    | 93  |

|   |      | 6.2.1    | Comparison in terms of standard attributes                   | 94  |

|   |      | 6.2.2    | DPA attack resistance                                        | 94  |

|   |      | 6.2.3    | CPA attack resistance                                        | 95  |

|   |      | 6.2.4    | Comparison in terms of normalized attributes                 | 96  |

|   |      | 6.2.5    | EPE attack resistance                                        | 97  |

|   | 6.3  | Experie  | mentation for symmetric NMOS based pre-charge logic in 65    |     |

|   |      | nm tec   | hnology                                                      | 97  |

|   |      | 6.3.1    | Comparison in terms of standard attributes                   | 98  |

|   |      | 6.3.2    | DPA attack resistance                                        | 98  |

|   |      | 6.3.3    | CPA attack resistance                                        | 99  |

|   |      | 6.3.4    | Comparison in terms of normalized attributes                 | 100 |

|                                                         |                                                                      | 6.3.5   | EPE attack resistance                                   | 100 |

|---------------------------------------------------------|----------------------------------------------------------------------|---------|---------------------------------------------------------|-----|

|                                                         | 6.4 Experimentation for top-bottom pre-charge in 65 nm technology 10 |         |                                                         | 102 |

|                                                         |                                                                      | 6.4.1   | Comparison in terms of standard attributes              | 102 |

|                                                         |                                                                      | 6.4.2   | DPA attack resistance                                   | 103 |

|                                                         |                                                                      | 6.4.3   | CPA attack resistance                                   | 104 |

|                                                         |                                                                      | 6.4.4   | Comparison in terms of normalized attributes            | 105 |

|                                                         |                                                                      | 6.4.5   | EPE attack resistance                                   | 106 |

|                                                         | 6.5                                                                  | Experi  | imentation for Top pre-charge logic in 65 nm technology | 107 |

|                                                         |                                                                      | 6.5.1   | Comparison in terms of standard attributes              | 108 |

|                                                         |                                                                      | 6.5.2   | DPA attack resistance                                   | 108 |

|                                                         |                                                                      | 6.5.3   | CPA attack resistance                                   | 108 |

|                                                         |                                                                      | 6.5.4   | Comparison in terms of normalized attributes            | 109 |

|                                                         |                                                                      | 6.5.5   | EPE attack resistance                                   | 110 |

|                                                         | 6.6                                                                  | Conclu  | usion                                                   | 111 |

| 7                                                       | Con                                                                  | clusion | s and future work                                       | 113 |

|                                                         | 7.1                                                                  | Future  | e work                                                  | 114 |

| A BDDs of AES generated by automated synthesis tool 117 |                                                                      |         |                                                         |     |

| Bi                                                      | Bibliography 126                                                     |         |                                                         |     |

| Pu                                                      | Pulications 133                                                      |         |                                                         |     |

# **List of Figures**

| 2.1  | Decision tree for $f = (a \lor b) \land c$ .                                              | 12 |  |  |

|------|-------------------------------------------------------------------------------------------|----|--|--|

| 2.2  | Reduced BDD for $f = (a \lor b) \land c \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 14 |  |  |

| 2.3  | Digital design flow.                                                                      | 15 |  |  |

| 2.4  | Standard cell design flow                                                                 |    |  |  |

| 2.5  | PTL based basic cell design.                                                              | 19 |  |  |

| 2.6  | Conventional Process of cryptography.                                                     | 21 |  |  |

| 2.7  | Symmetric-Key cryptography.                                                               | 21 |  |  |

| 2.8  | Asymmetric-Key cryptography.                                                              | 24 |  |  |

| 2.9  | A example data-dependent power consumption due to early propagation.                      | 29 |  |  |

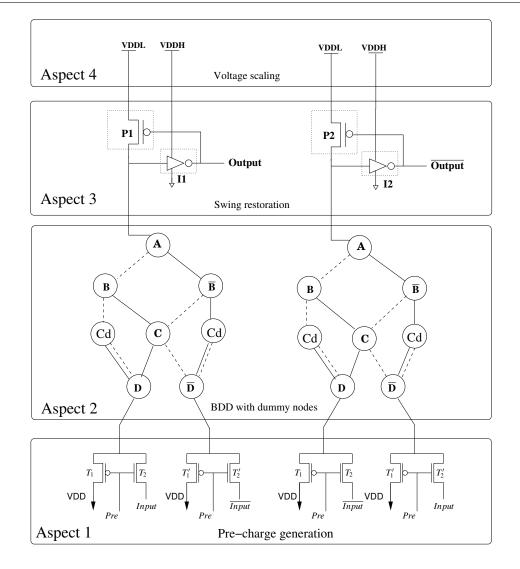

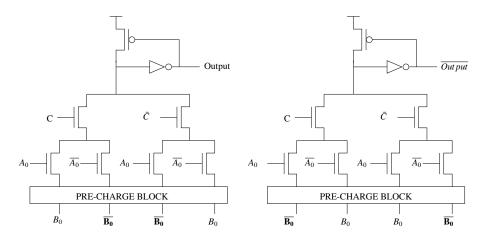

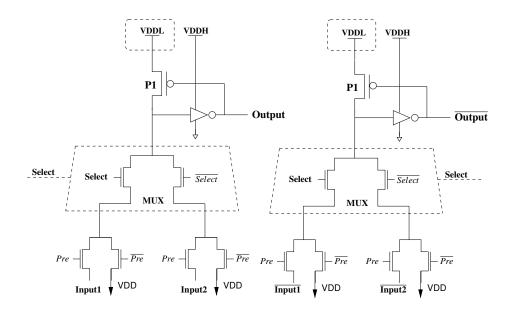

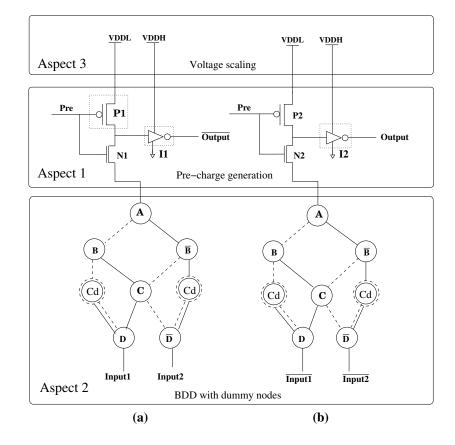

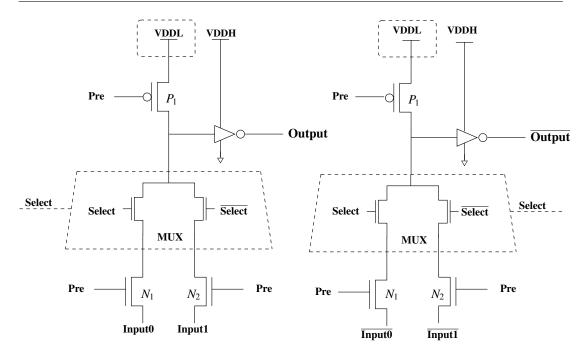

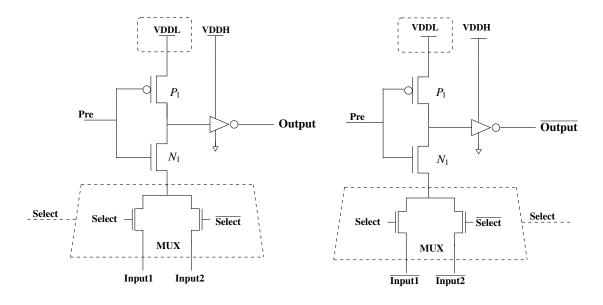

| 3.1  | The four aspects of BDD based logic synthesis with bottom pre-charge                      | 33 |  |  |

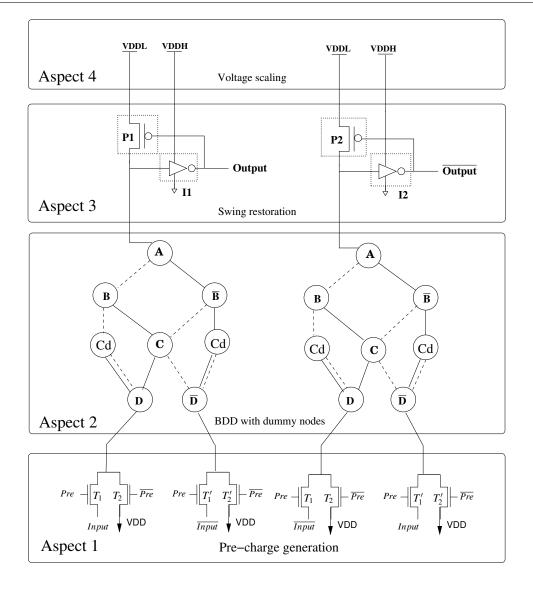

| 3.2  | The four aspects of BDD based logic synthesis with symmetric NMOS based                   |    |  |  |

|      | pre-charge                                                                                | 34 |  |  |

| 3.3  | Design of the Bottom pre-charge logic                                                     | 35 |  |  |

| 3.4  | Design of the symmetric NMOS based bottom pre-charge logic                                | 35 |  |  |

| 3.5  | (a) BDD for $\overline{x+y}$ . (b) BDD for $\overline{x+y}$ after dummy node insertion    | 37 |  |  |

| 3.6  | Pass transistor logic based circuit realization from a BDD                                | 38 |  |  |

| 3.7  | Design of the basic cell with bottom pre-charge logic                                     | 42 |  |  |

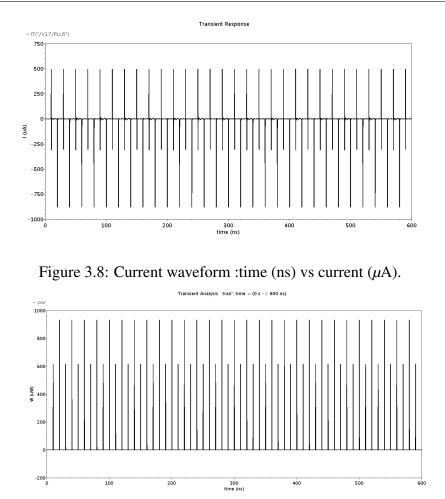

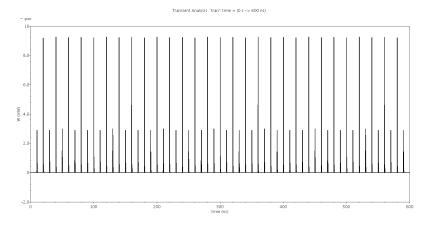

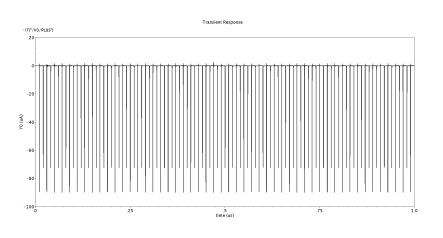

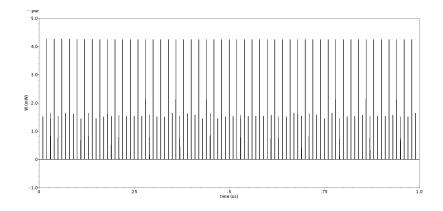

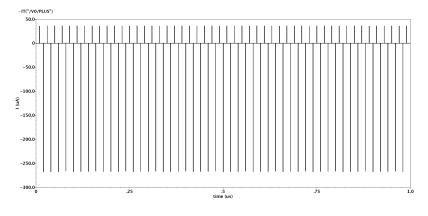

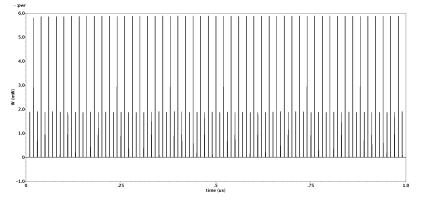

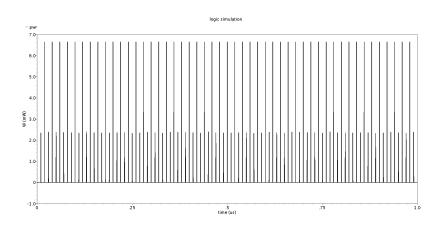

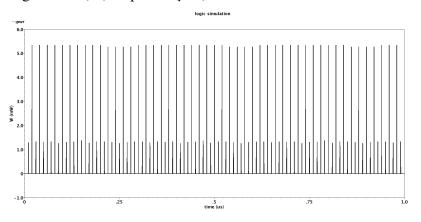

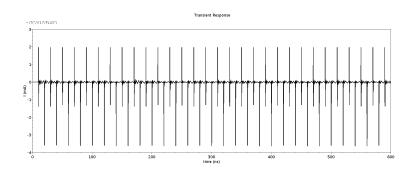

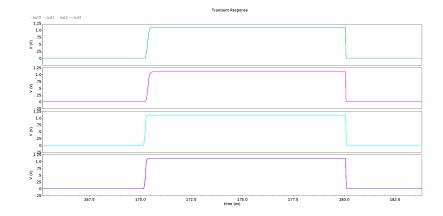

| 3.8  | Current waveform :time (ns) vs current ( $\mu$ A)                                         | 43 |  |  |

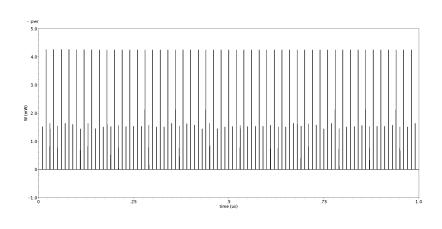

| 3.9  | Power waveform :time (ns) vs power ( $\mu$ W)                                             | 43 |  |  |

| 3.10 | Waveforms for the basic cell with bottom pre-charge                                       | 43 |  |  |

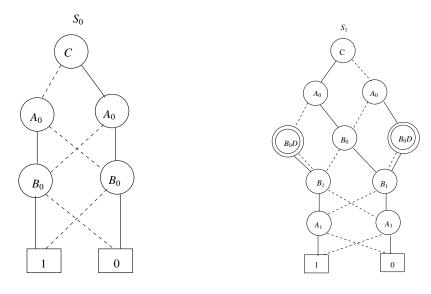

| 3.11 | Resultant BDD after dummy node insertion of the corresponding 3.1                         |    |  |  |

|      | equation                                                                                  | 44 |  |  |

| 3.12 | Resultant BDD after dummy node insertion of the corresponding 3.2                         |    |  |  |

|      | equation                                                                                  | 44 |  |  |

| 3.13 | Resultant BDD after dummy node insertion of the corresponding 3.3                         |    |  |  |

|      | equation                                                                                  | 45 |  |  |

| 3.14 | Resultant BDD after dummy node insertion of the corresponding 3.4                         |    |  |  |

|      | equation                                                                                  | 45 |  |  |

| 3.15 | Sum0 circuit.                                                                             | 49 |  |  |

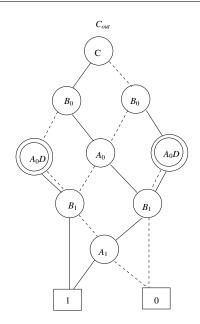

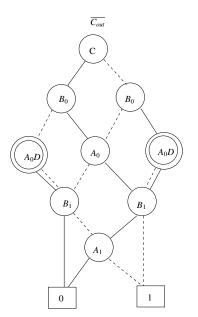

| 3.16 | Sum1 circuit.                                                                             | 49 |  |  |

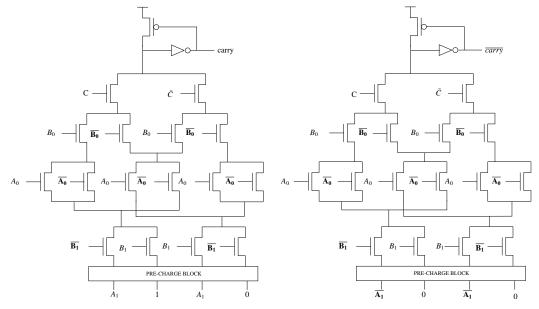

| 3.17 | Carry and complementary carry circuits.                                                   | 49 |  |  |

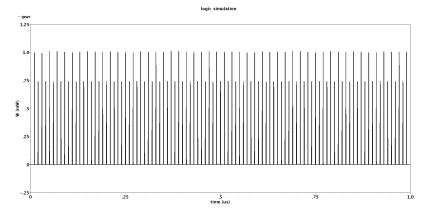

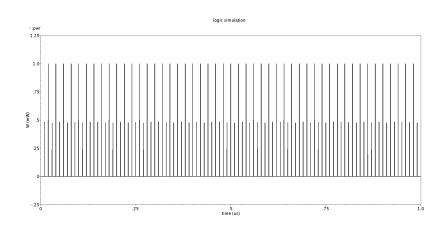

| 3.18 | Current waveform for the 2 bit adder :time (ns) vs current ( $\mu$ A)                     | 50 |  |  |

| 3.19 | Power waveform for the 2 bit adder :time (ns) vs power ( $\mu$ W)                         | 50 |  |  |

| 3.20 | Power and current waveform for the 2 bit adder with bottom pre-                       |    |

|------|---------------------------------------------------------------------------------------|----|

|      | charge logic                                                                          | 50 |

| 3.21 | Design of the basic cell with voltage scaling using symmetric NMOS                    |    |

|      | based pre-charge logic.                                                               | 51 |

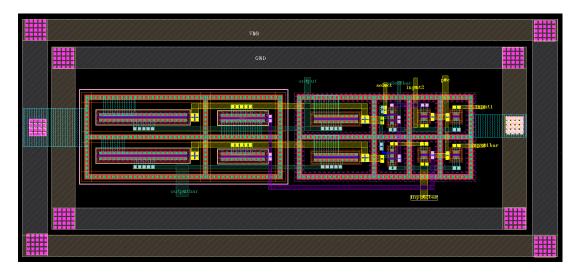

| 3.22 | Layout of the basic cell using symmetric NMOS based pre-charge logic.                 | 51 |

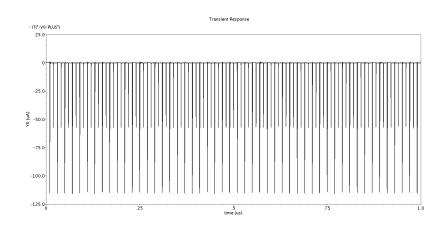

| 3.23 | Current waveform characteristics of the basic cell with the symmetric                 |    |

|      | NMOS based pre-charge generation logic and the dual voltage source:                   |    |

|      | time (ns) vs current ( $\mu$ A).                                                      | 52 |

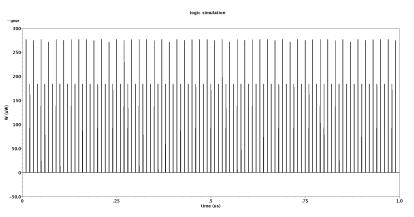

| 3.24 | Power waveform characteristics of the basic cell with the symmetric                   |    |

|      | NMOS based pre-charge generation logic and the dual voltage source:                   |    |

|      | time (ns) vs power ( $\mu$ W).                                                        | 52 |

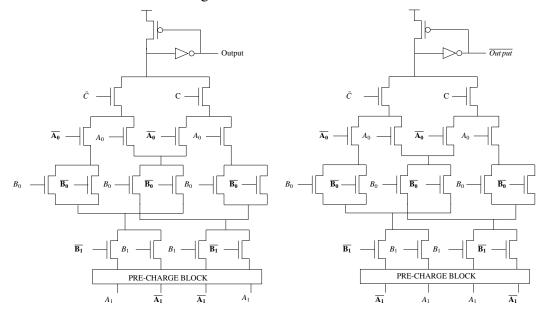

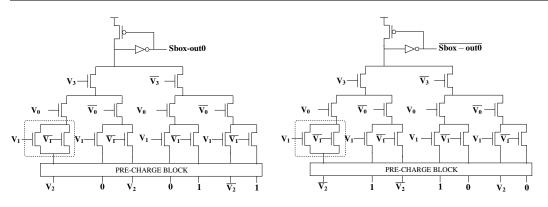

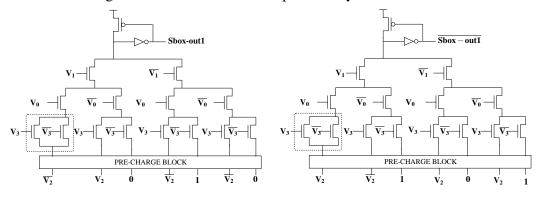

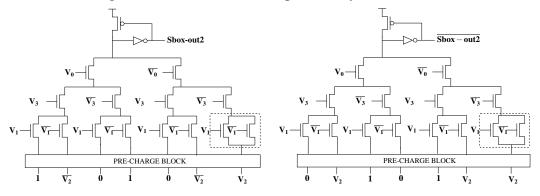

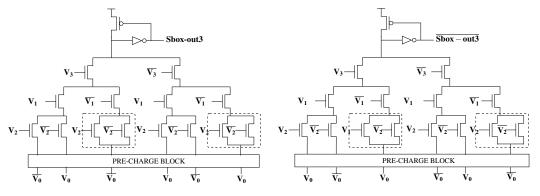

| 3.25 | Normal and complementary circuits for out0.                                           | 53 |

|      | Normal and complementary circuits for out1.                                           | 53 |

|      | Normal and complementary circuits for out2.                                           | 53 |

|      | Normal and complementary circuits for out3.                                           | 53 |

|      | Normal and complementary circuits for the output bits of Present S-                   |    |

|      | box with the dummy nodes highlighted using dashed boxes.                              | 53 |

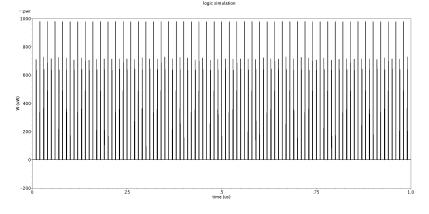

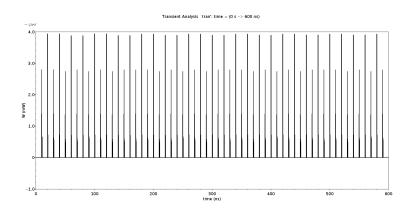

| 3.30 | Current waveform characteristics of the Present S-box with the sym-                   |    |

|      | metric NMOS based pre-charge generation logic : time (ns) vs current                  |    |

|      | (mA)                                                                                  | 54 |

| 3.31 | Power waveform characteristics of the Present S-box with the sym-                     | υ. |

| 0.01 | metric NMOS based pre-charge generation logic : time (ns) vs power                    |    |

|      | (mW)                                                                                  | 54 |

| 3 32 | Current waveform characteristics of the Lucifer S-box symmetric NMOS                  |    |

| 0.02 | based pre-charge generation logic : time (ns) vs current (mA).                        | 55 |

| 3 33 | Power waveform characteristics of the Lucifer S-box symmetric NMOS                    | 55 |

| 5.55 | based pre-charge generation logic : time (ns) vs power (mW)                           | 55 |

|      | bused pre charge generation togie : time (hs) vs power (ht w):                        | 55 |

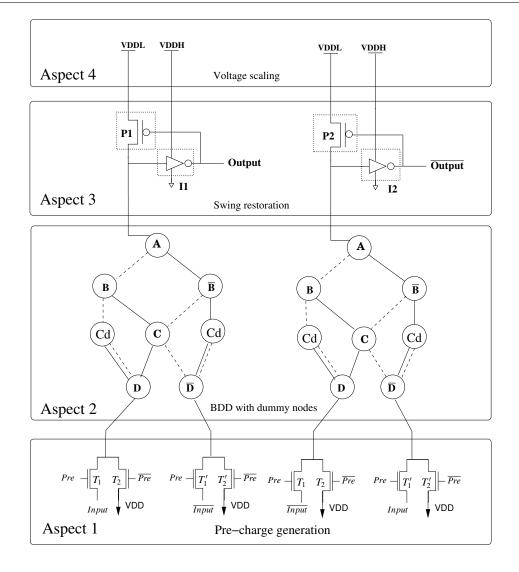

| 4.1  | The three aspects of BDD based logic operation with top pre-charge                    |    |

|      | logic                                                                                 | 59 |

| 4.2  | The three aspects of BDD based logic operation with top-bottom pre-                   |    |

|      | charge logic                                                                          | 60 |

| 4.3  | Basic structure of the basic cell with (a) top pre-charge logic, (b) top-             |    |

|      | bottom pre-charge logic.                                                              | 61 |

| 4.4  | (a) BDD for $\overline{x+y}$ (b) BDD for $\overline{x+y}$ after dummy node insertion. | 61 |

| 4.5  | Pass transistor logic based circuit realization from a BDD                            | 62 |

| 4.6  | Design of the BDD based basic cell with voltage scaling and top-                      |    |

|      | bottom pre-charge logic.                                                              | 66 |

| 4.7  | Layout of the basic cell with top-bottom pre-charge generation logic.                 | 67 |

| 4.8  | Power waveform characteristics of the basic cell with top-bottom pre-                 |    |

|      | charge generation logic: time (ns) vs power ( $\mu$ W)                                | 68 |

| 4.9  | Current waveform characteristics of the basic cell with top-bottom                    |    |

|      | pre-charge generation logic: time (ns) vs current (mA).                               | 68 |

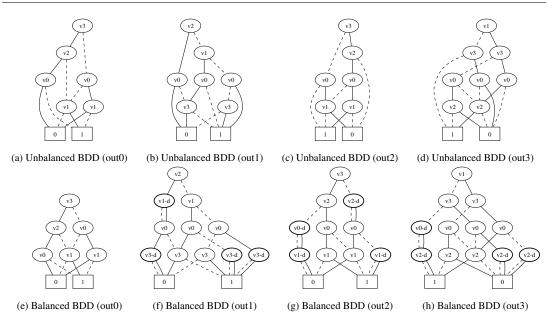

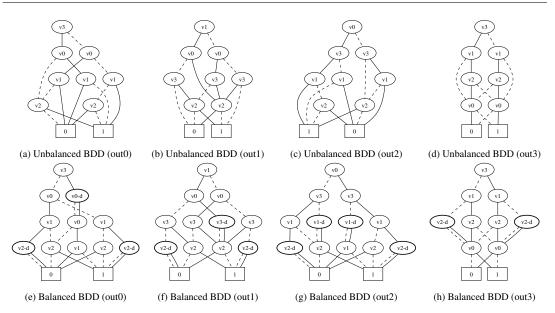

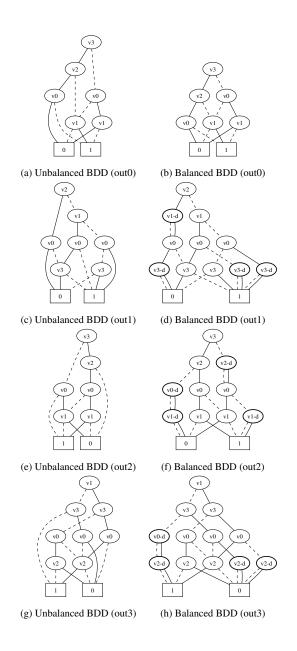

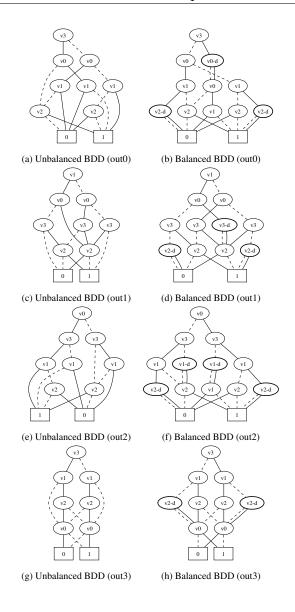

| 4.10 | Unbalanced and balanced BDDs for the output bits of the Lucifer S-                    |    |

|      | box highlighting the dummy nodes inserted                                             | 69 |

| 4.11 | Unbalanced and balanced BDDs for the output bits of the Present S-                    | -  |

|      | box highlighting the dummy nodes inserted.                                            | 70 |

|      |                                                                                       |    |

| 4.12       | Power waveform characteristics of the Lucifer S-box with top bottom       |     |

|------------|---------------------------------------------------------------------------|-----|

|            | pre-charge generation logic: time (ns) vs power ( $\mu$ W)                | 71  |

| 4.13       | Power waveform characteristics of the Present S-box with top bottom       |     |

|            | pre-charge generation logic: time (ns) vs power ( $\mu$ W)                | 71  |

| 4.14       | Design of the BDD based basic cell with voltage scaling and top pre-      |     |

|            | charge logic.                                                             | 72  |

| 4.15       | Power waveform characteristics of the basic cell with top pre-charge      |     |

|            | generation logic: time (ns) vs power ( $\mu$ W)                           | 73  |

| 4.16       | Current waveform characteristics of the basic cell with top pre-charge    |     |

|            | generation logic: time (ns) vs current (mA).                              | 73  |

| 4.17       | Power waveform characteristics of the Lucifer S-box with top pre-         |     |

|            | charge generation logic: time (ns) vs power ( $\mu$ W)                    | 74  |

| 4.18       | Power waveform characteristics of the Present S-box with top pre-         |     |

|            | charge generation logic: time (ns) vs power ( $\mu$ W)                    | 74  |

|            |                                                                           |     |

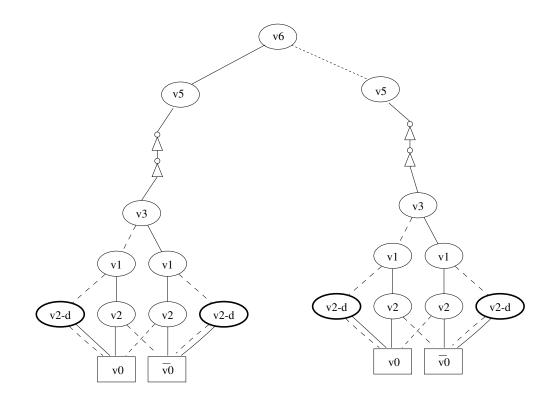

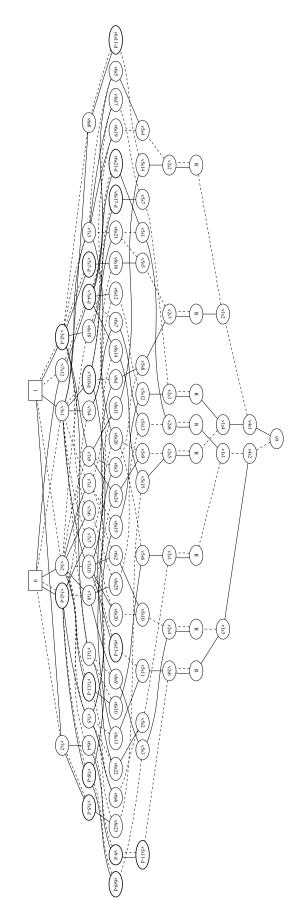

| 5.1        | Unbalanced and balanced BDDs for the output bits of the Lucifer S-        |     |

|            | box highlighting the dummy nodes inserted                                 | 85  |

| 5.2        | Unbalanced and balanced BDDs for the output bits of the Present S-        |     |

|            | box highlighting the dummy nodes inserted.                                | 86  |

| 5.3        | Reducing the balanced BDD of Fig. 5.2(h).                                 | 86  |

| 5.4        | Partitioning the large BDDs                                               | 87  |

| 5.5        | Reducing the balanced BDD of AES out0                                     | 88  |

| <i>.</i> . |                                                                           |     |

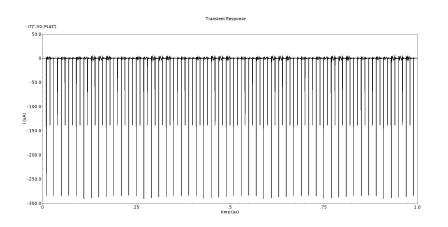

| 6.1        | Evaluation of DPA resistance by computing DoM                             | 92  |

| 6.2        | Current waveform generated by the attack                                  | 92  |

| 6.3        | Power waveform generated by the attack.                                   | 93  |

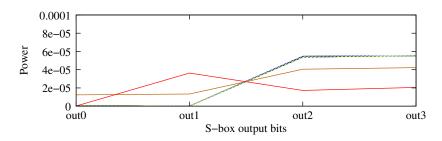

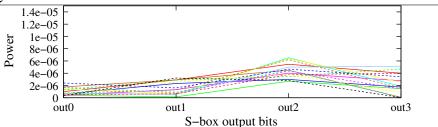

| 6.4        | DPA attack on bottom pre-charge logic design: Present S-box output        | ~ ~ |

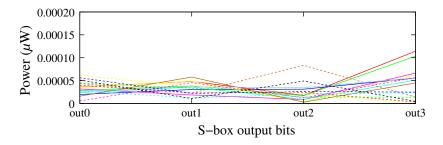

|            | bits vs power ( $\mu$ W)                                                  | 95  |

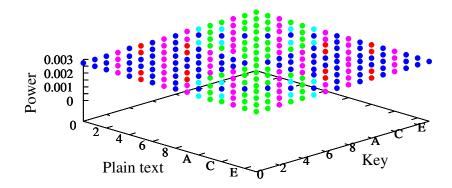

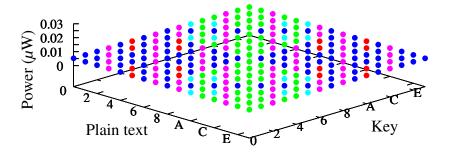

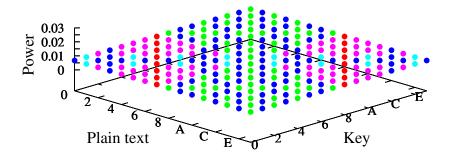

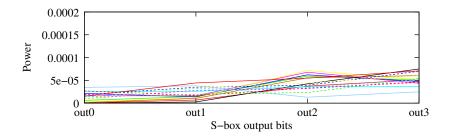

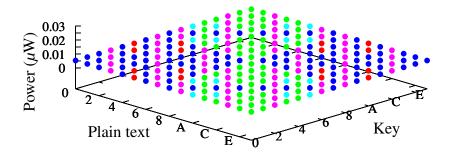

| 6.5        | CPA attack on bottom pre-charge logic Present S-box design: plain         |     |

|            | text vs key vs power ( $\mu$ W)                                           | 95  |

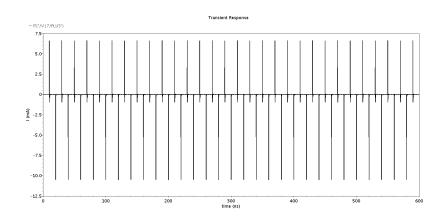

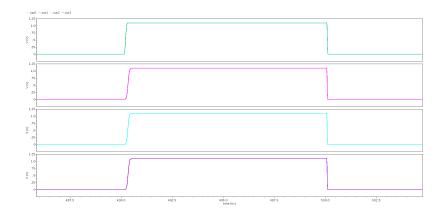

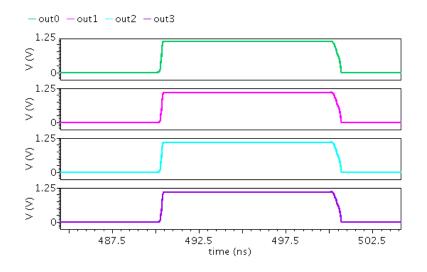

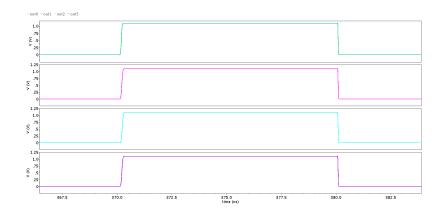

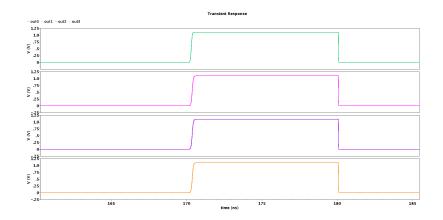

| 6.6        | Timing response of the four output bits (all 1s) generated by the Present |     |

|            | S-box desin using bottom pre-charge logic: time (ns) vs voltage (V)       | 96  |

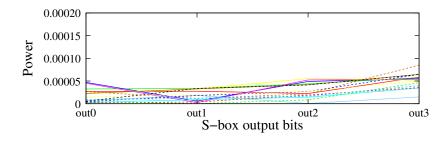

| 6.7        | DPA attack on symetric-NMOS based pre-charge logic design: Present        |     |

|            | S-box output bits vs power ( $\mu$ W)                                     | 99  |

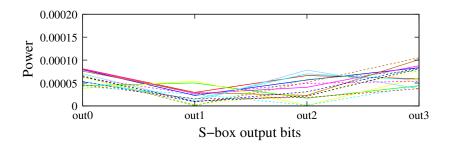

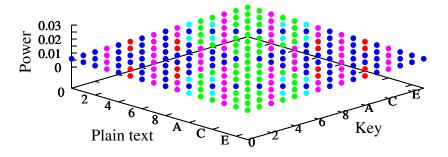

| 6.8        | CPA attack on symetric-NMOS based pre-charge logic Present S-box          |     |

|            | design: plain text vs key vs power ( $\mu$ W)                             | 99  |

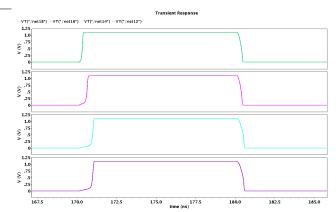

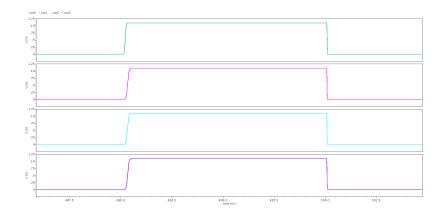

| 6.9        | Timing response of the four output bits (all 1s) generated by the Present |     |

|            | S-box desin using symetric-NMOS based pre-charge logic: time (ns)         |     |

|            | vs voltage (V)                                                            | 100 |

| 6.10       | Timing response of the four output bits (all 1s) generated by the lucifer |     |

|            | S-box desin using symetric-NMOS based pre-charge logic: time (ns)         |     |

|            | vs voltage (V)                                                            | 101 |

| 6.11       | DPA attack on our Lucifer S-box design with top-bottom pre-charge         |     |

|            | logic: S-box output bits vs power ( $\mu$ W)                              | 103 |

| 6.12       | DPA attack on our Present S-box design with top-bottom pre-charge         |     |

|            | logic: S-box output bits vs power ( $\mu$ W)                              | 103 |

| 6.13 | CPA attack on our Lucifer S-box design with top-bottom pre-charge    |     |

|------|----------------------------------------------------------------------|-----|

|      | logic: plain text vs key vs power ( $\mu$ W)                         | 104 |

| 6.14 | CPA attack on our Present S-box design with top-bottom pre-charge    |     |

|      | logic: plain text vs key vs power ( $\mu$ W)                         | 104 |

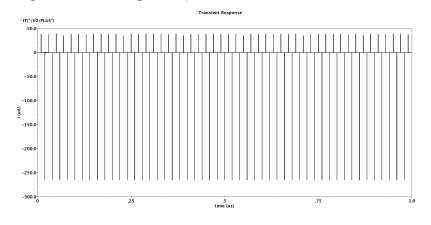

| 6.15 | Transient response of the four output bits (all 1s) generated by the |     |

|      | Lucifer S-box: time (ns) vs voltage (V).                             | 106 |

| 6.16 | Transient response of the four output bits (all 1s) generated by the |     |

|      | Present S-box: time (ns) vs voltage (V).                             | 106 |

| 6.17 | DPA attack on our Present S-box design with top pre-charge logic:    |     |

|      | S-box output bits vs power ( $\mu$ W)                                | 108 |

| 6.18 | DPA attack on our Lucifer S-box design with top pre-charge logic:    |     |

|      | S-box output bits vs power ( $\mu$ W)                                | 109 |

| 6.19 | CPA attack on our Present S-box design with top pre-charge logic:    |     |

|      | plain text vs key vs power ( $\mu$ W)                                | 109 |

| 6.20 | Transient response of the four output bits (all 1s) generated by the |     |

|      | Lucifer S-box with top pre-charge: time (ns) vs voltage (V).         | 110 |

| 6.21 | Transient response of the four output bits (all 1s) generated by the |     |

|      | Present S-box with top pre-charge: time (ns) vs voltage (V)          | 111 |

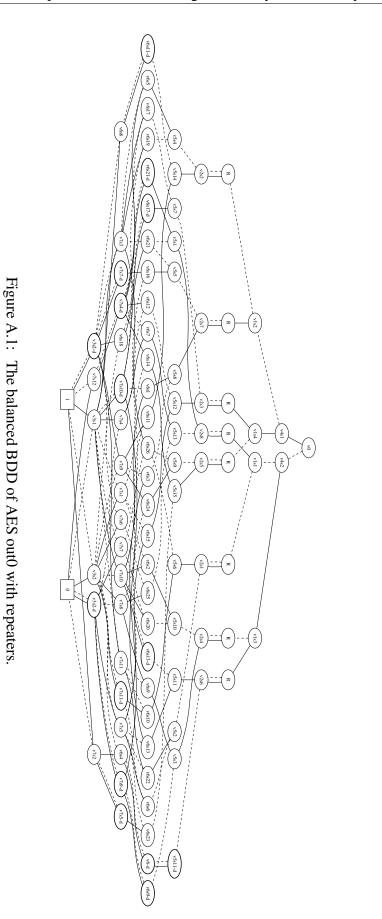

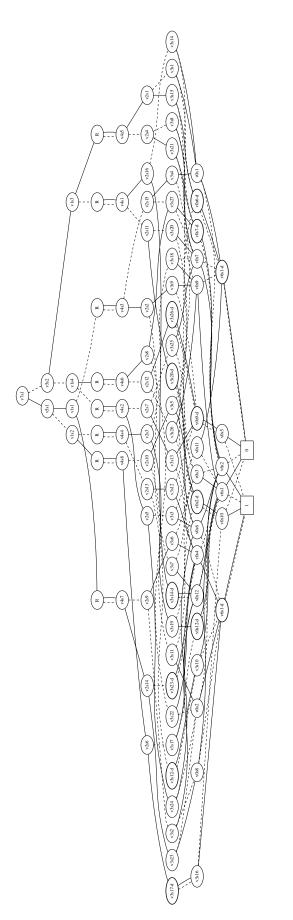

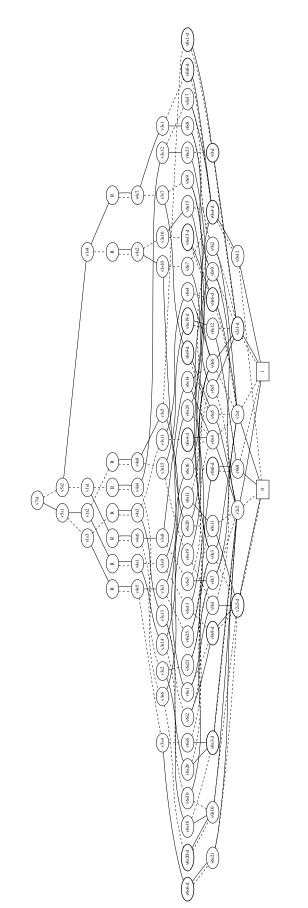

| A.1  | The balanced BDD of AES out0 with repeaters                          | 118 |

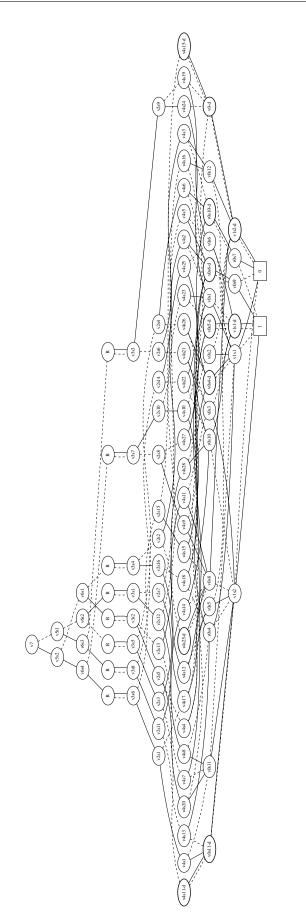

| A.2  | The balanced BDD of AES out1 with repeaters                          | 119 |

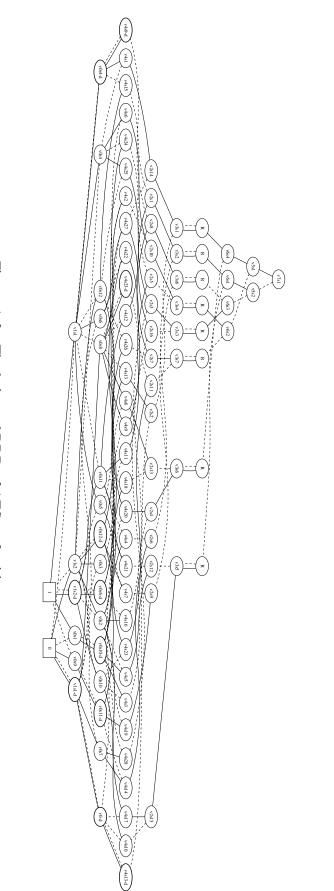

| A.3  | The balanced BDD of AES out2 with repeaters                          | 120 |

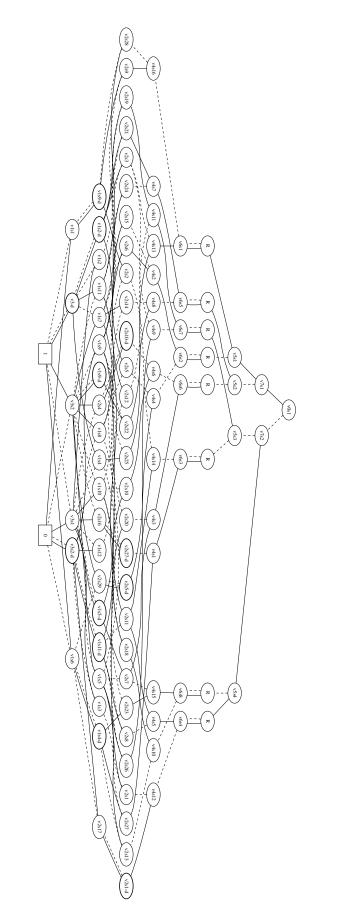

| A.4  | The balanced BDD of AES out3 with repeaters                          | 121 |

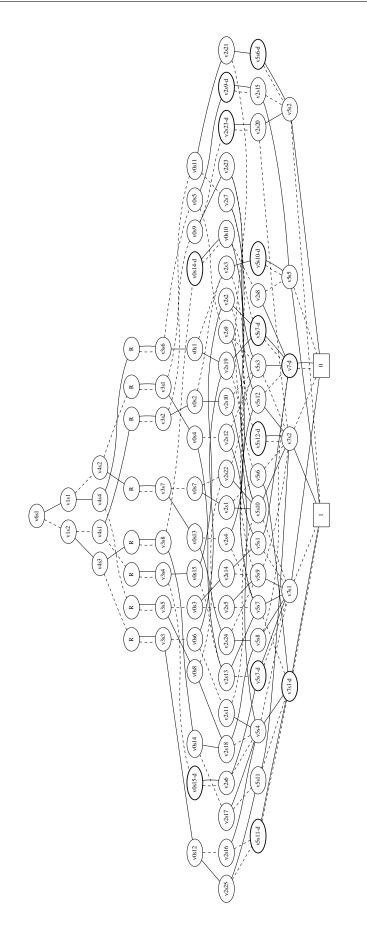

| A.5  | The balanced BDD of AES out4 with repeaters                          | 122 |

| A.6  | The balanced BDD of AES out5 with repeaters                          | 123 |

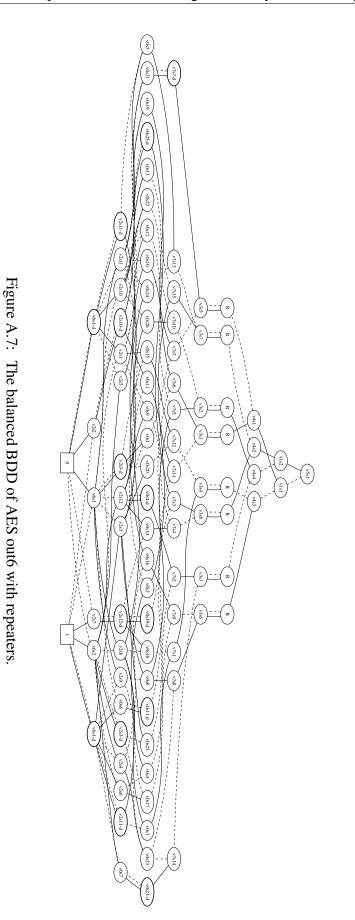

| A.7  | The balanced BDD of AES out6 with repeaters                          | 124 |

| A.8  | The balanced BDD of AES out7 with repeaters                          | 125 |

|      |                                                                      |     |

# **List of Tables**

| 1.1          | Power consumed due to switching                                                                                                    | 3          |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.1<br>2.2   | Power consumed due to switching                                                                                                    | 26<br>29   |

| 3.1<br>3.2   | Basic cell functions using multiplexing                                                                                            | 41<br>47   |

| 4.1<br>4.2   | Basic cell functions using multiplexing                                                                                            | 65<br>66   |

| 6.1<br>6.2   | Comparison between SDMLp and Our method                                                                                            | 93<br>94   |

| 6.3<br>6.4   | Comparison with respect to NED and NSD<br>Delay in output generation for the basic cell by symetric-NMOS based<br>pre-charge logic | 95<br>96   |

| 6.5          | Comparison with other methods with symetric-NMOS based pre-charge logic                                                            | 90<br>97   |

| 6.6<br>6.7   | -                                                                                                                                  | 100        |

| 6.8          | r · · · · · · · · · · · · · · · · · · ·                                                                                            | 101<br>102 |

| 6.9          | 1 1                                                                                                                                | 105        |

| 6.10<br>6.11 | Delay in output generation for the basic cell                                                                                      |            |

|              | Comparison with respect to NED and NSD                                                                                             |            |

|              | Delay in output generation for the basic cell                                                                                      |            |

# Chapter 1

# Introduction

Digital communications have become a major part of modern day life. With increase in reliance on the information transmitted through the web and other communication media, it has become a major challenge to keep those information safe and resist unauthorized accesses. A sensitive component of such transactions involve electronic banking ranging from internet banking to the use of smart debit/credit cards. We often talk of speed on the internet access, another significantly more important concern is that of security of information that is sent across the internet or between electronic devices. Smart cards include electronic circuits that authenticate the identity of the card holder. While data going through the internet is protected by encryption, there are several, relatively new and counter initiative, issues regarding the secure use of smart cards. The work done in this thesis is directly applicable to the vulnerability of such transactions done using smart cards.

Modern cryptography has the four objective: confidentiality, integrity, non-repudiation and authentication [5].

- Confidentiality: information can be only understood by intended persons

- Integrity: information should be unaltered

- Non-repudiation: sender of the information cannot deny at a later stage his or her intentions in the creation or transmission of the information

• Authentication: sender or receiver have to confirm their identity on time of sending and receiving the data

A cryptographic algorithm is a complex mathematical function that uses a secret key to encrypt information and without the knowledge of the required secret key, decrypting this information would be infeasible. During the past years, there has been a lot of research on cryptography and as a result there are several algorithms that provide data security and authenticity, such as RSA [37], ECC [23, 29], AES [31], DES [18], and DSA [32].

Cryptographic systems involve complex mathematical functions to make it difficult for intruders to discover the systems' secret keys. However, conventional hardware proves to be inadequate to process these functions. To overcome this issue, dedicated cryptographic hardware is used and still evolving. While these devices aim to achieve both security and efficiency, operational behaviour and corresponding data being handled by these hardware can be deciphered by intruders at the time of their execution by statistically analyzing their various properties like power, execution time, electromagnetic leaks, sound, etc. This phenomenon of acquiring sensitive data by exploiting the information gained from the physical implementation of a cryptographic system is called *side channel attack*.

The information available to the attacker is a set of public transactional messages processed by the cryptographic device and the corresponding running time, power dissipation, etc. and his goal is to recover the secret parameters being used inside the device using the available information. Different forms of side channel attacks are as follows:

- Timing attacks: attacks based on measuring how much time is taken to perform various computations [19, 24].

- Power monitoring attacks: attacks which make use of the varying power consumption by the hardware during computation [26, 30].

- Electromagnetic attacks: attacks based on leaked electromagnetic radiation which can directly provide information [1, 21].

- Acoustic cryptanalysis: attacks which exploit sound produced during computations [49].

- Differential fault analysis: in which secrets are discovered by introducing faults in a computation [8, 50].

- Data remanence: in which sensitive data are read after supposedly having been deleted [38].

A comprehensive study of side channel attacks can be found in [26, 30]. Among the various physical properties, the power consumption model is predominantly used to identify the secret keys because power traces are easily available. In general, the hardware synthesis flow attempts to optimize area, average power consumption and propagation delay. However in those flows security is mostly neglected.

Power dissipation of a circuit is proportional to its switching activity which, in turn, depends on the data that is being handled. The data dependent power consumption can be exploited to leak away the secret information, specifically, distribution of 0's and 1's. This is explained by means of table 1.1 which shows the signal transitions of single rail static circuit. Let P<sub>1</sub> and P<sub>2</sub> be the powers consumed during the transitions  $1\rightarrow 0$  and  $0\rightarrow 1$ , respectively. The amount of power consumed for these two transitions being different (i.e., P<sub>1</sub>  $\neq$  P<sub>2</sub>), the asymmetry can be exploited to mount power analysis attacks. Depending upon how the power traces are monitored, their analysis can be further classified.

- Simple Power Analysis (SPA): Only a single power trace is examined to extract the secret key.

- Differential Power Analysis (DPA): It involves collecting large number of power traces and performing statistical analysis of the power variation with respect to changes in data values to extract the secret key.

| Transitions       | Power consumed |

|-------------------|----------------|

| 1→0               | P <sub>1</sub> |

| 0→1               | P <sub>2</sub> |

| $0 \rightarrow 0$ | 0              |

| 1→1               | 0              |

Table 1.1: Power consumed due to switching

There are broadly two types of countermeasures of DPA based on their level of application: (*i*) algorithmic level, and (*ii*) cell level. Our focus is on cell level countermeasures for DPA. A cell level approach ensures algorithmic agnostic DPA resistance and also enables speedy completion of the encryption and the decryption processes. Moreover, it avoids extra circuitry to the extent that is needed for implementing reported algorithmic level DPA countermeasures [4, 33].

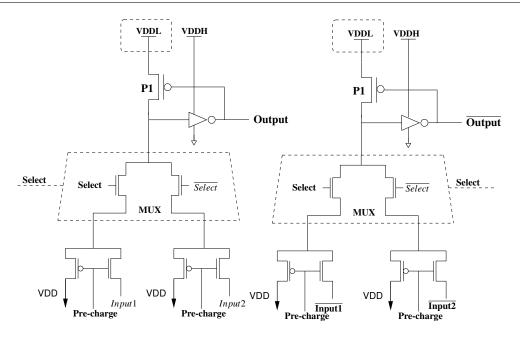

Prevalent circuit level countermeasures for DPA rely on customized transistor level circuit designs. The concept of Dynamic Differential Logic (DDL) has been used in Differential Cascade Voltage Switch Logic (DCVSL) [22]. However, circuit asymmetries in the gates realized using DCVSL can cause large variations in power consumption. Sense Amplifier Based Logic (SABL) [42, 45, 46], has been developed to overcome this drawback of DCVSL. SABL uses fixed amount of charge for every transition, even when a gate does not change its switching state. In every cycle, a SABL gate charges a total capacitance with a constant value. The emergence of WDDL [47] was an important development against DPA. WDDL has been found to exhibit resistance against power attacks for deployment on ASIC, FPGA [47], and AES coprocessor [44] fabricated on  $0.18\mu$ m CMOS technology.

A digital design flow for producing secure integrated circuits using WDDL is described in [48]. While WDDL circuits have the advantage of being realizable using standard cells, the resulting circuits lack the optimization possible for circuits specifically designed for DPA resistance. WDDL also suffers from the *early propagation effect* (EPE) which is caused when input signals of a WDDL gate have different delay times. The leakage due to EPE can be a potential source of data-dependent power consumption that may lead to more sophisticated power analysis attacks [27].

To overcome EPE, Dual-rail Pre-charge circuit with Binary Decision Diagram (DP-BDD) architecture was proposed in [3]. In a DP-BDD based circuit, it is ensured that the input signals always pass through the same number of AND-OR gates, thus countering the early propagation effect. Recently, Secure Differential Multiplexer Logic using Pass transistor (SDMLp) [35] has been used to provide DPA resistance comparable to that of WDDL while requiring lesser area, power and current, and having lower peak power variation. SDMLp is based on Reduced Ordered Binary Decision Diagram (ROBDD) which is capable of representing a logic function more succinctly (i.e., requiring lesser nodes) than normal BDD, thus saving on layout area.

However, it is important to evaluate the effectiveness of the countermeasures. Some techniques for systematically analysing DPA leakage have been developed in the literature [7, 15, 16]. Constructing a power consumption model is an important step for analysis of the effects of countermeasures. For instance, the model based on analog characteristics of CMOS circuits [15], the model based on the Hamming weight [16], and the simplification model of [15] based on transition of data registers [7] were proposed in 1999, 2000 and 2002, respectively.

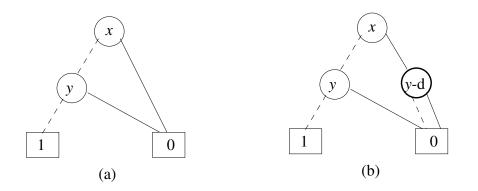

### **1.1** Motivation

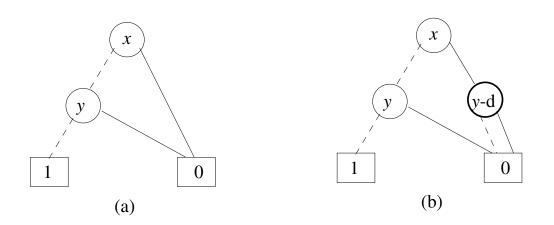

Reported DPA countermeasures are found not to ensure an identical number of transistors switches for all possible inputs. In this work we developed a design and synthesis scheme where the underlying transistor circuitry necessarily has the same number of transistors on all paths from the inputs to the output. The transistors are interconnected to create pull-up and pull-down paths to output by way of binary decisions based on the input variables, so as to realise the required Boolean function. This principle of operation has directly permitted the use binary decision diagram (BDD) [2, 11] based logic synthesis to design the required pull-up and pull-down networks of transistors. While the reduced order binary decision diagram (ROBDD) [2, 13] based synthesis mechanism yields optimised logic functions, it does not ensure identical path lengths. This problem is overcome through the insertion of *dummy* transistor for path length equalisation.

It is well known that dual rail pre-charge logic discharges parasitic capacitance periodically and thus enhances the power invariant characteristics of the circuit [41, 45–47]. In this work we explore the potential benefits of positioning the pre-charge generation logic at various places in the overall circuit – an aspect that is practically missing in the literature. In particular, we consider four pre-charge configurations and evaluate the resulting circuit behaviour with respect to characteristics such as power, current, delay and also evaluate the effectiveness against various power attacks.

### **1.2 Problem statement**

Variance in power dissipation is a key factor in determining the success or failure of a power analysis attack. Dynamic power which is major component of the total power consumption depends on the switching activity of the transistors which, in turn, depends on the input combinations applied to the transistors. The current flows from the *voltage-source* to the *ground* through intermediate capacitors (but not directly) of transistor networks depending on the switching activity of transistors. Outputs are produced by charging or discharging the output capacitors. Existing dual-rail complementary circuit realizations of logic functions designed for power attack resistance have asymmetry in the critical paths between points through which there is flow of charge. This asymmetry leads to different power consumption and also different propagation delays for different input combinations – making the circuit vulnerable to power attacks as well as timing attack, and the early propagation effect.

In this work, our objective is to identify power attack, timing attack and early propagation effect resistant circuit structures towards achieving satisfactory attack resistance with the property of identical critical path lengths of all possible switching paths. This property also has the potential to give immunity to timing attacks unless the excecution of the underlying algorithm itself is data dependent and opens the possibility of launching of timing attacks. Necessary pull-up and pull-down circuits are constructed based on the Boolean function of the input variables. Therefore, BDD based logic synthesis can be applied to design such pull-up and pull-down networks of transistors. ROBDD based mechanism reduces the logic functions by changing the order of the input variables. However, critical paths from parent to leaf nodes vary in such designs. To overcome this issue, dummy nodes have been inserted as required for path balancing.

## **1.3 Summary of contributions**

The contribution of this work is the development of a BDD based logic synthesis approach to counter power analysis attacks along with two different pre-charge generation logics styles. Each logic style consists of two different pre-charge generation schemes. The operation of this logic (for each of the pre-charge generation scheme) has four aspects, viz.:

- Pre-charging circuitry specially designed to work with BDD based directed acyclic graph (arising from folding the BDD tree)

- BDD based normal and complementary function realizations with identical critical path length of all possible switching paths and dual-rail complementary functions

- Output generation with proper voltage level

- Low power techniques (voltage scaling, leakage reductions) to reduce overall power dissipation without hampering DPA resistance

Based on our experience of designing power analysis attack (PAA) resistant circuits, we also provide an automated synthesis process of such circuits which involves the following steps:

- ROBDD based logic minimization with normal and complementary functions

- Insertion of dummy nodes for path balancing, pre-charge nodes for pre-charge logic and regenerative nodes for fanout

- Partitions of larger BDD structures into smaller realisable structures without compromising attack resistance

- Converting the resulting BDD to transistor-level Verilog

The operation of these customized designs is first described using a basic cell supporting fourteen logic functions including AND, OR, XOR, NOT, NAND, NOR. While any logic can be constructed using this basic cell, more optimized circuit realization is possible by utilizing the ROBDD based normal and complementary function realizations aspects of this logic synthesis approach. This is illustrated through the design of the 2-bit adder and different S-boxes [9, 40]. Experimental results have been gathered for the basic cell, the adder and the different S-box realizations. These results have demonstrated that our logic outperforms competing methods in terms of peak power variation, average power and average current and also repelled strong power attacks.

## 1.4 Thesis outline

The remaining thesis chapters are as follows:

# **Chapter 2: Preliminaries** This chapter presents some preliminary concepts relevant to the thesis which are as follows:

- Binary Decision Diagrams: This section describes BDD principles and the basic mechanism to represent a Boolean function as a BDD or ROBDD

- ASIC design flow: This section describes basic flow of digital system design

- Pass transistor logic: This section describes pass transistor logic principles

- Power consumption of CMOS logic: This section describes how power dissipation happen in the CMOS circuits

- Cryptographic preliminaries: This section describes basic principle of cryptography

- Side channel attacks: This section describes basic concepts of side channel attacks, different type of power attacks

Chapter 3: Basic BDD based circuits with bottom pre-charge This chapter describes BDD based logic synthesis and circuit design methods to counter power attack with the specific feature that the pre-charging is controlled via the leaf nodes of the transistor network realising the BDD.

- Bottom pre-charge

- Symmetric NMOS transistor based pre-charge

## Chapter 4: BDD based circuits with various other features This chapter describes BDD based logic synthesis and circuit design methods to counter power attack with other pre-charging schemes such as:

- Top pre-charge

- Top-bottom pre-charge

- **Chapter 5: Automated synthesis scheme** This chapter describes automated synthesis schemes for circuits designed using the above pre-charging techniques along with generation of the synthesisable Verilog code for these.

- **Chapter 6: Experimental results with different process technology** This chapter describes the experimentation and presents experimental results to establish resistance of our circuits to power attacks

- Chapter 7: Conclusions and future work Summary of work done in this thesis and conclusions so derived are presented. We also consider how this work can be further extended.

# Chapter 2

# **Preliminaries**

The work in this thesis involves use of CMOS circuits, PTL circuits, ASIC design, binary decision diagrams, low power techniques, use of cryptographic algorithms, side channel attacks. This chapter covers some elementary concepts and topics from these diverse areas that are relevant to this thesis.

This chapter is organized as follows. In the section 2.1 we introduce the binary decision diagram. Different ASIC design flows are introduced in section 2.2. Power dissipation in CMOS circuits is described in the section 2.4. Basic cryptographic concepts and the notion of side channel attacks, specifically for CMOS circuits are given in section 2.5.

## 2.1 Binary Decision Diagrams and Reduced Ordered Binary Decision Diagrams

We first introduce binary decision diagrams (BDD) and then explain how reduced ordered binary decision diagrams (ROBDD) are derived from those. We also discuss the additional properties of ROBDDs over BDDs.

Binary Decision Diagrams (BDDs) are decision trees based on Shannon's expansion. BDDs are extensively used for circuit design. A brief definition of the BDD is as follows: A binary decision diagram (BDD) is a rooted decision tree having the following properties.

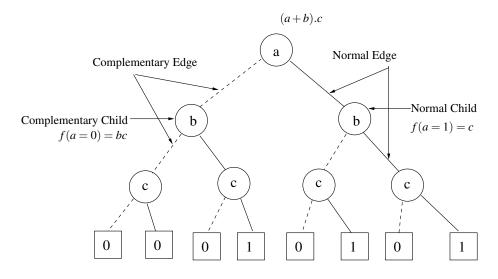

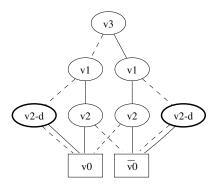

Figure 2.1: Decision tree for  $f = (a \lor b) \land c$ .

- Internal nodes of a BDD are labelled with variable names

- Leaf nodes of a BDD are labelled with either 0 or 1

- Each internal node in the DAG has exactly two children; one of the two arcs connecting a parent node to one child node is labelled by 0 (represented by a dashed line) while the other arc is labelled 1 (represent as a solid line)

- Nodes on every path in the graph have unique labels; different nodes on a single path are labeled by distinct variables

- Left and right sub-DAGs of every node are distinct

- Every pair of sub-DAGs rooted at two different nodes  $n_1$ ,  $n_2$  are non-isomorphic

The last property ensures that the BDD is reduced.

Given a Boolean function  $f(x_1, x_2, ..., x_k)$ , by Shannon's decomposition around variable  $x_1, f(x_1, x_2, ..., x_k)$ , this may be written as

$$f(x_1, x_2, \dots, x_k) = (x_1 \land f_{x_1 \leftarrow 1}) \lor (\neg x_1 \land f_{x_1 \leftarrow 0})$$

(2.1)

Here  $f_{x_1 \leftarrow 1}$  denotes f with  $x_1$  substituted by 1 and  $f_{x_1 \leftarrow 0}$  denotes f with  $x_1$  substituted by 0.  $f_{x_1 \leftarrow 1}$  and  $f_{x_1 \leftarrow 0}$  are also called the positive and negative cofactors to f with respect to  $x_1$ .

Suppose the Boolean function  $f(x_1, ..., x_k)$  is decomposed around variable  $x_i$  represented by a DAG node labelled  $x_i$ , then that node will have two children – the 0-child, representing  $f_{x_1 \leftarrow 0}$  and the 1-child representing  $f_{x_1 \leftarrow 1}$ . The edge connecting the node labelled  $x_1$  to the 1-child is called the normal edge, while the edge connecting that to the 0-child is called the complementary edge – refer to the picture of a BDD shown in Fig. 2.1. These cofactors may be further decomposed recursively, terminating at the Boolean constant 0 or 1, giving rise to the BDD representing the given function.

Given a valuation of the variables, the value of the function can be determined as follows:

- Starting from the root of the DAG follow either the normal or the complementary edges depending on the value of the decision variable at the node

- Continue this process until leaf node is reached

- For the given valuation of the variables, the value of the leaf node gives the value of the function

The variable ordering along a path from the root node to a leaf node is the sequence in which the variables appear along that path staring from the root node; it is the sequence in which variables are chosen for carrying out Shannon's decomposition. If the variable order is the same on all paths of the tree it is called an ordered decision tree. A BDD that is both ordered and reduced is called a Reduced Ordered Binary Decision Diagram (ROBDD). The ROBDD for a given Boolean function is unique and so the ROBDD representation of a Boolean function is canonical.

The steps of reducing BDD is following [17]:

- If two nodes represent the same function, then we merge them

- If a node has the same 0 -child and 1-child, then that node represents a "don't care" variable, and is removed. Formally, it follows from Shannon's decomposition that *f* is independent of *x<sub>i</sub>* whenever *f<sub>xi</sub>*→0 = *f<sub>xi</sub>*→1

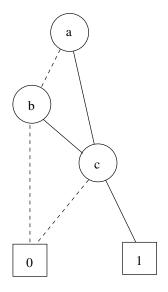

Figure 2.2: Reduced BDD for  $f = (a \lor b) \land c$

Applying these rules one obtains the Reduced Ordered Binary Decision Diagrams (ROBDD) which is canonical in nature. The task of finding the optimal variable ordering for a function is a computationally difficult problem. However, a wide variety of heuristics are available for finding a good variable ordering. Existing BDD packages such as CUDD often produce the optimum solution. The ROBDD for  $f = (a \lor b) \land c$  is shown in Fig. 2.2.

There are mainly two types of variable ordering available:

**Static variable ordering:** Static variable ordering techniques attempt to establish the optimal ordering of variables prior to constructing the actual BDD. A simple heuristic is that input variables that are topologically close together within the circuit should be relatively close together within the variable ordering for the resulting BDD. This is found to work well for tree-like circuits but does not generalise to most other circuits. Another principle is that the most influential of the primary inputs to the circuit (such as control inputs) are placed earlier on in the ordering. A detailed survey on static variable ordering is available in [36].

**Dynamic variable ordering:** In case of dynamic variable ordering, the ordering heuristics are used during the construction of BDDs. A circuit may have multiple subcircuits which may have different optimal variable ordering. In such situations, instead of a uniform global variable ordering, the ordering may vary from one sub-circuit to another. In a dynamic situation, shifting variables up and down and evaluating the impact is an important dynamic variable ordering mechanism. Sifting is not relevant to the current work.

#### 2.2 ASIC design flow

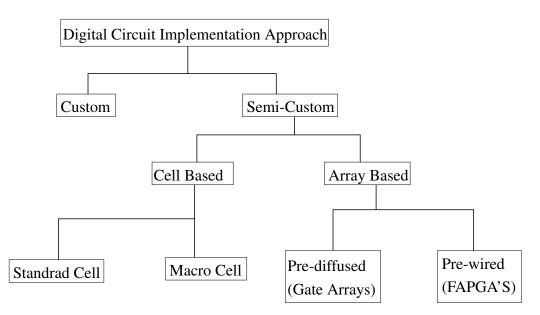

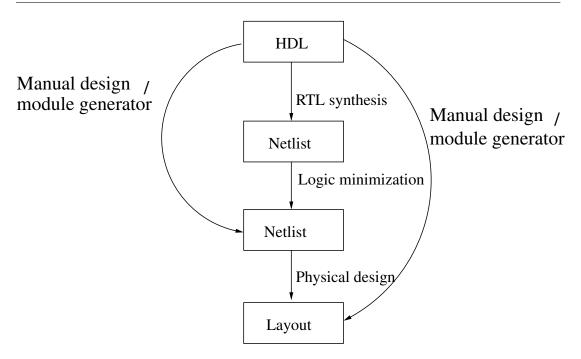

Application specific integrated circuit is popularly termed as ASIC. ASIC design flow is given in diagram 2.3.

Figure 2.3: Digital design flow.

There are broadly two methods that are followed for designing ASICs, using modern CAD tools, one is the full custom design flow, the other is the semi-custom design flow. Semi-custom design are two types: cell based and array based. Standard cell based and macro based design comes under cell based design flow. On the other hand, gate arrays and FPGA comes under array based design flow.

#### 2.2.1 Full custom design flow

In the full custom design flow, designers start designing from the scratch. Designers meet specification by designing transistor level circuits with optimized transistor widths. Layout, routing and synthesis is done at the transistor level by the designer. Most of the components are individually designed to give best overall performance, consuming lesser area and power in comparison with standard cell based designs. It is highly expensive and consumes huge man hours. It is generally used for designing new components for use with the other design styles. Specialised algorithms may also generate full custom design for particular applications. This is the design style we used for designing our circuits.

#### 2.2.2 Semi-custom design flow

Semi-custom design flow is the main area of focus of advanced CAD tools. We would basically emphasis on ASIC design and omit discussion on the FPGA design flow as that is not relevant to our current work. Details of semi-custom design flow is given below.

#### Standard cell based design flow

Here designers design and fabricate their design by using pre-designed basic gates, commonly known as standard cell. For a given a technology, standard cells are provided by the chip fabrication facility which are called standard cell design kits. These design kits reduce the cost of ASIC development. Standard cells of a particular family have the same height but vary in width making it suitable for placing in rows side by side. Gaps between rows are channels that are used for routing. Standard cell design flow is shown in Fig. 2.4.

#### Macro cell based design flow

More complex design modules may be provided as macros. For use with CAD tools these are given at a high level of abstraction. Macro cell based design can be sub-

Figure 2.4: Standard cell design flow.

classified into three parts.

- Hard macros: These are pre-complied design components which can be instantiated in a large design. For use at various levels of simulations, detailed abstract models of the component are made available for the designers, for protection of intellectual property right. Hard macros do not provide detailed internal layout information. Disadvantages of hard macros is their association with particular fab which results in lower flexibility. However these do have the benefit of optimised performance often with human optimisation.

- Firm macros: These are pre-complied design components which can be instantiated in the large design. Here the netlist is provided for use with the design tool. The physical design is done at the designer end. Protection of intellectual properties is less compared to hard macros. Physical design is more flexible with firm macros.

- Soft macros: These are also pre-complied design components which can be instantiated in the large design. Here the RTL is provided for use with the design tool. Logic design is done at designer end. Protection of intellectual properties is even less but design options are more. Optimisation is done by the CAD tool

and that is usually lower than that offered by hard macros.

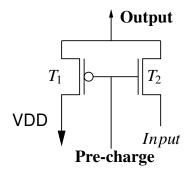

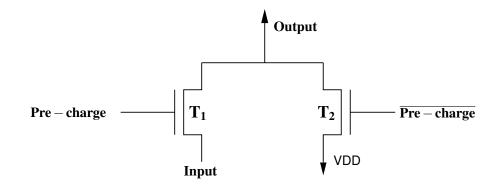

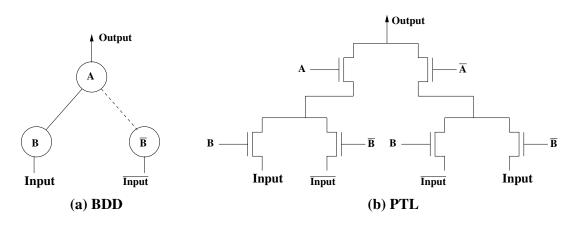

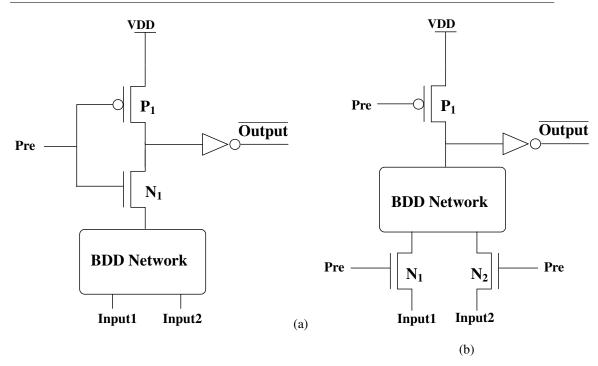

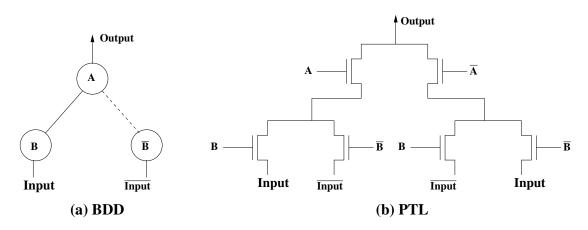

#### 2.3 Pass transistor logic

The basic idea behind pass transistor logic, commonly known as PTL, is multiplexing. Functionally, pass transistors behave like a switches. The source of the pass transistor is connected with some input signal. Generally, it is connected with power supply rail for other logics. Either NMOS or PMOS transistor is sufficient to perform the logic operation. This results in smaller number of transistors and smaller input loads, especially when NMOS transistor networks are used. However, there is a voltage drop at the output,  $V_{out} = VDD - V_{thN}$  due to the threshold voltage of the NMOS transistor while passing a logic '1'. To maintain the output voltage an acceptable range, swing restoration at the gate output is necessary. Pass transistor logic network whose basic structure is that of a multiplexer requires complementary control signals. Thus, dualrail logic which produces both normal and complemented form. To provide acceptable output driving capabilities inverters are attached with the gate outputs. Only single paths of each network must be active at a time to avoids short circuits [51].

Advantages of pass transistor logic:

- Ratio-less: In conventional CMOS logic, the width to length (W/L) ratio of the pull up device is generally few times greater than the pull down devices. As a result the geometrical dimension of the transistor is not minimal always. However, pass transistor can be realize with minimum dimension of a particular technology thus making it more area efficient.

- Lesser power: In a pass transistor logic realization of a Boolean function there is no DC path from supply to ground. So, standby power dissipation is small. Each additional input requires only minimum geometry transistor which results in minimal increase in power dissipation.

- Lower area: Only a few NMOS and PMOS transistors are sufficient to realize any logic function using pass transistor logic which ensures smaller input load and smaller area. Thus lower power consumption is achieved.

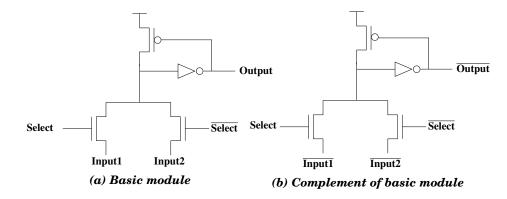

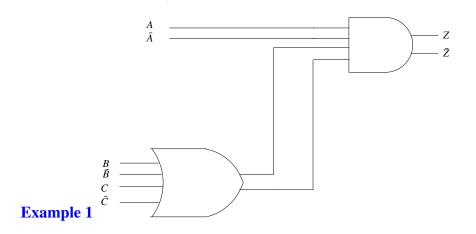

Figure 2.5: PTL based basic cell design.

There are many different types of pass transistor logic styles in use, such as:

- Complementary pass transistor logic (CPL)

- Swing restored pass-transistor logic (SRPL)

- Double pass transistor logic (DPL)

- Single-rail pass transistor logic (LEAP)

- The differential pass transistor logic (DPTL)

We use the complementary pass transistor logic with swing restorations. The basic multiplexer structure is given in Fig. 2.5. It is to be noted that pass transistor logic synthesis from BDDs is a well-studied domain [6, 14, 20].

#### 2.4 Power consumption of CMOS logic

Complementary Metal Oxide Semiconductor (CMOS) logic is most widely used for realization of ICs in modern times. CMOS consist of a pull up and a pull down network. The pull up network is realized with PMOS transistors while the pull down network is realized with NMOS transistors. Pull up and pull down networks are functionally complementary in nature. Only one of this network is conducting at a time.

Three major components of power consumption are:

• Dynamic power: Dynamic power which is the major component of the of total power consumption depends on charging and discharging of load capacitance. Dynamic power consumption can be calculated by the following equation:

$$P_{dynamic} = \alpha C_{load} V_{DD}^2 f \tag{2.2}$$

where  $\alpha$  is the switching activity factor of the circuit,  $C_{load}$  is the load capacitance including the parasitic capacitance,  $V_{DD}$  is the supply voltage and f is the circuit's operating frequency.  $\alpha$  the switching activity of the transistors, in turn, depends on the input combinations applied to the transistors which is measured by  $0\rightarrow 1$  transitions on the output of CMOS gates. Dynamic power directly depends on the input combinations applied to the transistors if the supply voltage and frequency are constant.

- Short circuit power: Short circuit power dissipation happens when gate voltage is applied to CMOS gate and both the transistors are changing state, then both the pull up network and pull down network are conducting simultaneously for a short period of time and there exists a direct connection between the voltage source to ground. Short circuit power is also dependent on switching activity factor  $\alpha$ .

- Static power (leakage power) : The static power or leakage power consumption of a circuit is given by the following equation:

$$P_{static} = I_{static} V_{DD} \tag{2.3}$$

where  $I_{static}$  is the current that flows between the supply rail when circuit is in idle mode that means there is zero switching activity in the circuit. Leakage power consumption emerges as a major portion of total power consumption for sub-micron technology, as CMOS technology scales down leakage power increases. A higher value of the threshold voltage helps to reduce the leakage current and therefore the lekage power.

#### 2.5 Vulnerability of cryptosystems to side channel attacks

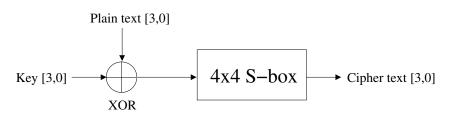

A cryptographic algorithm is a complex mathematical function that uses a secret key to encrypt information. The process by which message is encrypted by the secret key is referred to as encryption. The process by which an encrypted message is recovered in its earlier from is called decryption. The input of the encryption process is termed as plain text and the resultant output of the encryption process is termed as cipher text.

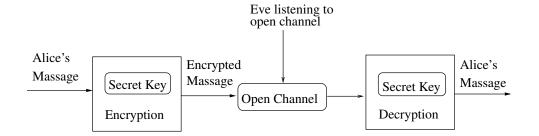

Figure 2.6: Conventional Process of cryptography.

Consider the famous cryptographic scenario where Alice has to send a secret message to Bob and does not want anyone else other then Bob to see this message. However, Alice sends the message through an insecure channel. Eve, a third person, is interested in knowing the content of the message. To protect the message from Eve, Alice send a cryptographic message to Bob. The entire mechanism is shown in Fig. 2.6. Depending upon encryption and decryption technique, this mechanism can be further classified in two ways.

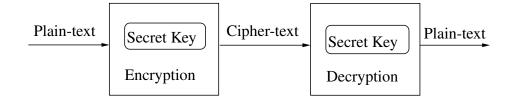

#### 2.5.1 Symmetric-Key encryption

Figure 2.7: Symmetric-Key cryptography.

Alice encrypts the message with a secret key using an encryption algorithm and sends it to Bob. Bob after receiving the message, decrypts it using the same secret key (which Alice has used) with the help of a decryption algorithm. Here a single secret key has been used for both encryption and decryption. Let *P* be the plain text which Alice has sent to Bob, *K* be the secret key by which Alice encrypted *P* with encryption algorithm  $E_k(x)$  and produced cipher text *C*. Bob decrypts *C* with the decryption algorithm  $D_K(x)$  and regenerates *P*.

So, during encryption:  $C = E_K(P)$  and during decryption  $P = D_K(C)$ such that  $D_K(E_k(x)) = E_k(D_K(x))$ In a nutshell, Alice:  $C = E_K(P)$  Bob:  $P_1 = D_K(C) = D_K(E_K(P)) = P$

The mechanism of the Symmetric-Key encryption is showing in Fig. 2.7. Depending upon the algorithm symmetric-key cryptography can be further classified into block ciphers and stream ciphers.

#### **Block cipher**

A block cipher takes an *n*-bit plain-text as a input and generates an *n*-bit cipher-text as output, where *n* is the block size. Diffusion and confusion techniques are used to encrypt data. The process by which redundancy in the plain-text and secret key are dissipated in the cipher-text is called diffusion. Resultant change in single input bit will be diffused over several cipher-text bits making it difficult for the attacker to gain knowledge of the plain text by analyzing the cipher-text. On the other hand, confusion is a process which makes the relationship between input and the cipher-text complex to make it difficult for the attacker to predict the patterns.

A product cipher combines two or more simple operations in a way that the resulting cipher is more secure than the individual components. These simple operations are meant to increase confusion or diffusion. An iterated block cipher is a cipher which involves sequential repetition of an internal functions which referred as a round functions. Two well known schemes for designing block ciphers are Substitution-Permutation (SP) networks and Feistel networks. We have experimented with the Lucifer and Present S-boxes which are all block ciphers. **Substitution-Permutation (SP)** Substitution-Permutation (SP) networks is a product ciphers which generate after substitutions and permutations in different number of stages. The data is separated into smaller blocks during substitutions. For increasing the confusion, the values in these blocks are substituted for others. This method uses a look-up table which is referred as S-box. The influence of data from one part of the plain-text is diffused through the whole cipher-text by using swapping bits or combining values.

**Feistel networks** Feistel networks are a subset of SP networks. It also generates cipher after substitutions and permutations in different number of stages. We do not use this type of cipher in this thesis.

#### Stream cipher

A stream cipher operates on smaller units of plain-text, usually some bits. Stream cipher does not need fixed length of data, it operates on any length. It works on a continuous stream of data with a random number generator for encryption of the plain text. Cipher-text generated by a stream cipher will vary depending on when they are encountered during the encryption process. Stream cipher are generally faster and less complex in nature compared to block cipher. We do not use this type of cipher in this thesis.

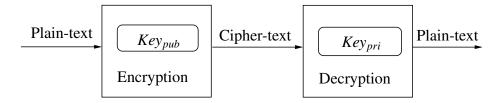

#### 2.5.2 Asymmetric-Key encryption

Key distribution is an important problem with symmetric cryptography. Take the classical example of cryptography where Alice has to securely communicate with Bob. So, in symmetric cryptography Alice and Bob has to exchange the secret key with other and they have to ensure the confidentiality of the key. But the channel is insecure. If there is a scenario where Alice has to communicate separately with a hundred different users he has to exchange that many secret keys before communicating. Here Asymmetric-Key Encryption turns out to be useful.

Here two keys are used; one is a public key and other is a private key. Alice

encrypts the message using Bob's public key. Bob decrypts the message using his own private key. The mechanism of Asymmetric-Key encryption is showing in Fig. 2.8. We do not use this method in this thesis.

Figure 2.8: Asymmetric-Key cryptography.

#### 2.6 Side channel attacks on cryptographic devices

The term *cryptanalysis* often refers to the study of ciphers, It is based on observing and analysing inputs and outputs of the cryptographic device. The cryptanalyst would attempt to extract the secret key based on these observations along with analysis and some knowledge of the implemented algorithms. Modern day cryptographic algorithms are mathematically more secure. It is almost impossible to mathematically break those systems and extract the systems' secret keys. However, their hardware implementations may be targeted and exploited for deducing the secret keys in use inside the system. Depending upon methods of the attacks it can be classified into two broad different category – (*i*) Invasive attacks and (*ii*) Non-invasive attacks

Invasive attacks are those which leave a physical evidence of tampering on the device. Common techniques are de-packing smart card chips, memory reverse engineering, and micro probing.

Non-invasive attacks are those that do not physically tamper with the device, instead they use information that is leaked from the device to attack. Non-invasive attacks are also commonly referred to as side channel attacks. The ability to attack devices such as smart cards on the fly, when those are being used, without leaving a trace of the attack has made side channel attacks very attractive. For this reason, securing devices from such attacks has gained significant practical importance.

#### 2.7 Side channel attacks

A special category of non-invasive attacks are called side channel attacks where the physical implementation of a cryptographic system can be monitored during its execution and the traces obtained can be examined by an attacker to discover the the secret key used in the system. Timing information, power consumption electromagnetic leaks, fault injection and sound can provide additional information by which cryptographic systems can be exploited. A comprehensive study of side channel attacks can be found in [26, 30]. Side channel attacks can be classified into invasive, non-invasive, active and passive attacks. The information available to the attacker is a set of messages processed by the cryptographic device and the corresponding running time, power dissipation etc. and his goal is to recover the device's secret parameters using the available information. Different forms of side channel attacks are as follows.

- Timing attacks: attacks based on measuring how much time is taken to perform various computations [19, 24].

- Power monitoring attacks: attacks which make use of the varying power consumption by the hardware during computation [26, 30].

- Electromagnetic attacks: attacks based on leaked electromagnetic radiation which can directly provide information [1, 21].

- Acoustic cryptanalysis: attacks which exploit sound produced during computations [49].

- Differential fault analysis: in which secrets are discovered by introducing faults in a computation [8, 50].

- Data remanence: in which sensitive data are read after supposedly having been deleted [38].

Among all these forms of attacks, the power monitoring attacks are the most prominent threat to the cryptographic systems since power traces of operations can be easily obtained. Those power traces can be mathematically analysed to reveal the secret keys quite easily. In general, power dissipation of a circuit is proportional to its switching activity which, in turn, depends on the data that is being handled. The data

| Transitions        | Power consumed |

|--------------------|----------------|

| 1→0                | P <sub>1</sub> |

| $0 \rightarrow 1$  | P <sub>2</sub> |