## An Optimization-based Methodology for High-Level Design of Analog Systems

Soumya Pandit

# An Optimization-based Methodology for High-Level Design of Analog Systems

Thesis submitted to the Indian Institute of Technology, Kharagpur For award of the degree

of

## Doctor of Philosophy (Ph.D.)

by

Soumya Pandit

School of Information Technology Indian Institute of Technology, Kharagpur

May 2009

To my parents for their constant support throughout my life. To Srabanti, the love of my life.

## Certificate of Approval

Certified that the thesis entitled "An Optimization-based Methodology for High-Level Design of Analog Systems" submitted by Soumya Pandit to the Indian Institute of Technology, Kharagpur for the award of the degree of Doctor of Philosophy, has been accepted by the external examiners and that the student has successfully defended the thesis in the viva-voce examination held today.

**Prof. Chittaranjan Mandal** (Supervisor)

**Prof. Amit Patra** (Co-Supervisor)

**Prof. Indranil Sengupta** (Chairman of DSC)

**Prof. G.Panda** (External Examiner)

**Prof. Shamik Shural** (Member of DSC)

**Prof. Siddhartha Sen** (Member of DSC)

### Declaration

*I*, the undersigned, hereby certify the following:

- 1. the work contained in this thesis is original and has been done by me under the guidance of my supervisor.

- 2. the work has not been submitted to any other Institute for any degree or diploma.

- 3. I have followed the guidelines provided by the Institute in preparing the thesis.

- 4. I have conformed to the norms and guidelines given in the Ethical Code of Conduct of the Institute.

- 5. whenever I have used materials (data, theoretical analysis, figures, and text) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references. Further, I have taken permission from the copyright owners of the sources, whenever necessary.

Dated: 18<sup>th</sup> May 2009 Kharagpur, Soumya Pandit Research Scholar, School of Information Technology Indian Institute of Technology Kharagpur -721 302, INDIA

### Certificate

This is to certify that the thesis entitled "An Optimization-based Methodology for High-Level Design of Analog Systems" submitted by Soumya Pandit to the Indian Institute of Technology, Kharagpur for the award of the degree of Doctor of Philosophy, is a record of bona fide research work carried out by him under our supervision and guidance and is worthy of consideration for the award of the degree of Doctor of Philosophy of the Institute

#### Chittaranjan Mandal

Associate Professor, School of Information Technology & Computer Science & Engineering Indian Institute of Technology Kharagpur -721 302, INDIA

#### Amit Patra

Professor, Department of Electrical Engineering Indian Institute of Technology Kharagpur -721 302, INDIA

### Acknowledgments

Writing this part of the thesis is probably the hardest. Though the list of people to thank is long, making this list is not the hard part. The hard part is finding the words that convey the sincerity and magnitude of my gratitude. People who were unknown to me a few years back, have now become a large part of my life, while people I already knew have remained pillars of constant support and encouragement through these long years. It is with all this help that I stand where I am.

My supervisor, Prof. Chittaranjan Mandal, has been primarily responsible for the freedom and timely guidance which I enjoyed during my doctoral studies. I shall be sincerely indebted to him for this. Prof. Amit Patra, my co-supervisor, has given me a lot of invaluable feedback on my research and I would like to thank him for that. I shall remain grateful to him for giving me chance to work in his consultancy project and for his partial financial support of the present research work. Prof. Shamik Sural has been a wonderful teacher and I am grateful to him for being a member of my doctoral committee. Prof. Indranil Sengupta, Head of SIT and one of my doctoral committee members has been very generous with his time on my seminars and I am indeed very thankful to him. Prof. Siddartha Sen, doctoral committee member has been exceptionally helpful in my stay at IIT Kharagpur, during which his door has always been open for me. I really enjoyed the working in his consultancy project, which is the primary source of funding of the present research work. I express my heartiest thanks to Sumit Kr. Bhattacharya, an M.Tech student of Electrical Engineering department for his significant technical contribution to this work. Thanks are due to Advanced VLSI Design Laboratory (AVDL), IIT Kharagpur and Department of Information Technology, Govt. of India for partial financial support to this project.

The AVDL members and facility staffs deserve a lot of thanks for helping me: Ashudeb, KCR, Sougata, Swamiji, Santosh, Subhashis, Anirban, Samiran, Uttamda, Joydeep and others have all contributed in no small amount to this project. The cooperation of all the SIT scholars: Somnath, Debashis, Misraji, Rajkumar, Ashalatha, Mandal-da, and Doctor-da is much appreciated. I express my thanks to all the SIT staff members: Mithun, Soumitri, Somadi, Samarda, Dasbabu, Malayda, Vinod and Raybabu.

The largest part of my campus life was dominated by my friends whom I worked with and learned from. I will begin with Mandal-da (Sushanta Mandal), who was such a source of knowledge and companionship that one cannot really hope for any better. Santosh, Sougata, Somnath and KCR have been wonderful friends on this journey.

I would not have been sitting here writing this acknowledgment of my PhD dissertation, were it not for my parents (Baba and Ma). Thank you for all the sacrifices you have made for me, thank you for your faith and confidence in me, and thank you for always supporting me in every endeavor. Your unending passion for work are truly inspiring to me. I owe great thanks to my brothers (Borda and Chhorda) for all things that they gave me or taught me. Without their support I would never have made any success. Words are inadequate to express my gratitude to my wife, Srabanti for being by my side through this roller-coaster ride, for having faith in me and for being my strength when everything seemed to be working against me, for celebrating my successes as if they were hers and for helping me emerge from my failures. I especially thank her for being so patient and taking a lot of pain in going through the entire thesis and providing me useful suggestions for technical improvement of the thesis. She has been my greatest source of strength and inspiration right from my undergraduate courses. I owe this degree most to her. Special thanks to my in-laws for being so supportive and understanding. I am grateful to them for their constant words of encouragement. Thanks are also due to all of my other family members, whose name I could not specify in this short space. Above all, to the One for always guiding me from within!

Soumya Pandit

### Abstract

Analog high-level design is rapidly becoming a main topic of interest in an analog design automation process because of its promise to deliver short design closure at much lesser costs. This has motivated us to develop methodologies which make several tasks of the analog high-level design process fast and accurate. This thesis presents optimization-based methodologies for the task of high-level performance model generation, optimal component-level topology generation and high-level specification translation.

This thesis first presents a non-parametric regression-based methodology for the generation of high-level performance models for analog component blocks. The transistor sizes of the circuit-level implementations of the component blocks along with a set of geometry constraints applied over them define the sample space. A Halton sequence generator is used as a sampling algorithm. Performance data are generated by simulating each sampled circuit configuration through SPICE. Least squares support vector machine (LS-SVM) is used as a regression function. Optimal values of the model hyper parameters are determined through a grid search-based technique and a genetic algorithm (GA)-based technique. The generalization ability of the models is estimated through a hold-out method and a k-fold cross validation method. The constructed performance models have been used to implement a GAbased topology sizing process. The advantages of the present methodology are that the constructed models are accurate with respect to real circuit-level simulation results, fast to evaluate and have a good generalization ability. In addition, the model construction time is low and the construction process does not require any detailed knowledge of circuit design. The entire methodology has been demonstrated with a set of experimental results.

This thesis then presents a top-down methodology for the generation of an optimal functional and component-level topology for linear analog systems, starting from a transfer function model of the system. The given transfer functions are converted to state space model which acts as the basis for generation of topologies of the system. The topology exploration process is modeled as a state space

matrix exploration process. Similarity transformation matrix is used as a topology transformation operator. The newly generated topologies have the same behavioral properties, but different performance properties. A simulated annealing-based optimization procedure determines an optimal state space model based on the performances of the models. The optimized state space model is realized by functional component blocks to generate an optimal functional topology, which is subsequently realized by appropriate analog component blocks to generate an optimal componentlevel topology of the system. As a case study, the thesis presents a methodology for generation of an operational transconductance amplifier (OTA)-capacitor (C) based optimal topology for a  $3^{rd}$  order and a  $4^{th}$  order continuous-time  $\Sigma\Delta$  modulator. It is found from the experimental results that the generated topologies are better in performances when compared to that of the commonly used topologies and satisfy the desired dynamic range specifications even under circuit-level non-ideal conditions. The advantage of the methodology is that the designer is able to specify the design goal and the desired specifications of a system at a higher level of abstraction in terms of transfer functions, while the design tool is able to generate an optimal component-level topology of the system directly from the transfer functions in a highly automated manner.

The thesis finally presents a design space exploration procedure for determining the specification parameters of the component blocks of the generated topology such that the desired specifications of the system are satisfied with optimized performances. A meet-in-the-middle approach is followed for constructing the feasible design space. It is constructed as the intersection of an application bounded specification space and a circuit realizable specification space. The former is constructed through a top-down procedure using interval analysis techniques and the latter, via a bottom-up procedure through actual circuit simulations. Least squares support vector machine-based classification principle is used to accurately identify the actual geometry of the feasible design space. Genetic algorithm is used for exploring the feasible design space. The reduced design space speeds up the exploration process. The cost function is computed through behavioral simulation of the entire system and by evaluating the high-level performance models of the component blocks. The final solution point is kept away from the feasible design space boundary, in order to increase the tolerance of the component specifications. The benefit of the methodology is that it is able to obtain practically correct circuit-level specifications of the component blocks of the system through a fast exploration process in a single pass.

The effectiveness of the procedure has been demonstrated by a set of experimental results.

These methodologies form the core of a semi-automated tool for analog highlevel design. The methodologies have been implemented under Matlab-Simulink environment. For demonstration of the methodologies, two case studies were chosen: an interface electronics system for MEMS capacitive accelerometer sensor and a continuous-time  $\Sigma\Delta$  modulator system. Optimal topologies for these two systems have been generated and specification parameters of the component blocks have been determined using the present methodologies. Finally, they have been implemented at the transistor level based on the derived specifications and are simulated with SPICE. The SPICE simulation results satisfy the desired specifications of the system and match closely with the predicted results. These validate the entire procedure. The entire high-level design process for the interface electronics system is completed in less than ten minutes time and for the  $\Sigma\Delta$  modulator system, the design process is completed within an hour. Thus the present methodologies make the high-level design process fast and accurate. In addition, the methodologies can be followed by users with less design experience.

# Contents

| 1                                                                   | Intr                              | oducti | ion        |                                                                                                  | 1  |

|---------------------------------------------------------------------|-----------------------------------|--------|------------|--------------------------------------------------------------------------------------------------|----|

|                                                                     | 1.1                               | Litera | ture Surv  | ey and Motivation                                                                                | 3  |

|                                                                     |                                   | 1.1.1  | Analog     | Performance Modeling                                                                             | 4  |

|                                                                     |                                   | 1.1.2  | Generat    | ion/Selection of an Optimal System Topology                                                      | 5  |

|                                                                     |                                   | 1.1.3  | High-Le    | vel Specification Translation $\ldots \ldots \ldots \ldots \ldots$                               | 7  |

| 1.2 Overview and Contributions of the Thesis $\ldots \ldots \ldots$ |                                   |        |            | Contributions of the Thesis                                                                      | 8  |

|                                                                     |                                   | 1.2.1  | Problem    | Definition $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 8  |

|                                                                     |                                   | 1.2.2  | Generat    | ion of High-Level Performance Models                                                             | 8  |

|                                                                     |                                   | 1.2.3  | Top-Dov    | wn Methodology for Generation of an Optimal Topol-                                               |    |

|                                                                     |                                   |        | ogy for 2  | Linear Analog Systems                                                                            | 9  |

|                                                                     |                                   | 1.2.4  | High-Le    | vel Specification Translation $\ldots \ldots \ldots \ldots \ldots$                               | 11 |

|                                                                     |                                   | 1.2.5  | Contribu   | utions $\ldots$ | 12 |

|                                                                     | 1.3                               | Organ  | ization of | The rest of the Thesis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                 | 12 |

| <b>2</b>                                                            | Opt                               | imizat | ion-base   | ed Analog High-Level Design Methodology                                                          | 15 |

|                                                                     | 2.1                               |        |            |                                                                                                  |    |

|                                                                     |                                   | 2.1.1  |            | ion-based Approach                                                                               |    |

|                                                                     |                                   | 2.1.2  |            | n-based Approach                                                                                 |    |

|                                                                     | 2.2                               | High-l |            | lel Generation                                                                                   |    |

|                                                                     | 2.2.1 Behavioral Model Generation |        |            |                                                                                                  | 19 |

|                                                                     |                                   |        | 2.2.1.1    | Analytical Techniques                                                                            | 20 |

|                                                                     |                                   |        | 2.2.1.2    | Fitting or Regression Methods                                                                    | 22 |

|                                                                     |                                   |        | 2.2.1.3    | Symbolic Model Generation Methods                                                                |    |

|                                                                     |                                   |        | 2.2.1.4    | Model Order Reduction Methods                                                                    | 24 |

| 2.2.2 Performance Estimation Model Generation                       |                                   |        |            |                                                                                                  | 24 |

|                                                                     |                                   |        | 2.2.2.1    | Bottom-Up Approach                                                                               | 24 |

|   |     |         | 2.2.2.2 Top-Down Approach                                                                          | 25 |

|---|-----|---------|----------------------------------------------------------------------------------------------------|----|

|   |     | 2.2.3   | Feasibility Model Generation                                                                       | 26 |

|   | 2.3 | Optim   | nization Methods                                                                                   | 26 |

|   |     | 2.3.1   | Deterministic Methods                                                                              | 27 |

|   |     | 2.3.2   | Stochastic Methods                                                                                 | 27 |

|   |     | 2.3.3   | Multi-Objective Optimization Method                                                                | 28 |

|   | 2.4 | Topole  | ogy Generation/Selection Methods                                                                   | 30 |

|   |     | 2.4.1   | Selection before or after sizing                                                                   | 30 |

|   |     | 2.4.2   | Selection during sizing                                                                            | 31 |

|   |     | 2.4.3   | Top-Down Generation                                                                                | 31 |

|   | 2.5 | Summ    | ary                                                                                                | 32 |

| 3 | Gen | ieratio | n of High-Level Performance Estimation Models                                                      | 33 |

|   | 3.1 | High-l  | Level Performance Estimation Models                                                                | 33 |

|   | 3.2 | Regres  | ssion-based Model Generation                                                                       | 35 |

|   |     | 3.2.1   | Sample Space and Design of Experiments                                                             | 35 |

|   |     | 3.2.2   | Training Data Generation and Scaling                                                               | 37 |

|   |     | 3.2.3   | Regression Using LS-SVM                                                                            | 40 |

|   |     |         | 3.2.3.1 Selection of Hyper parameters                                                              | 41 |

|   |     | 3.2.4   | Quality Measures                                                                                   | 45 |

|   | 3.3 | Comp    | arison with Existing Methodologies                                                                 | 45 |

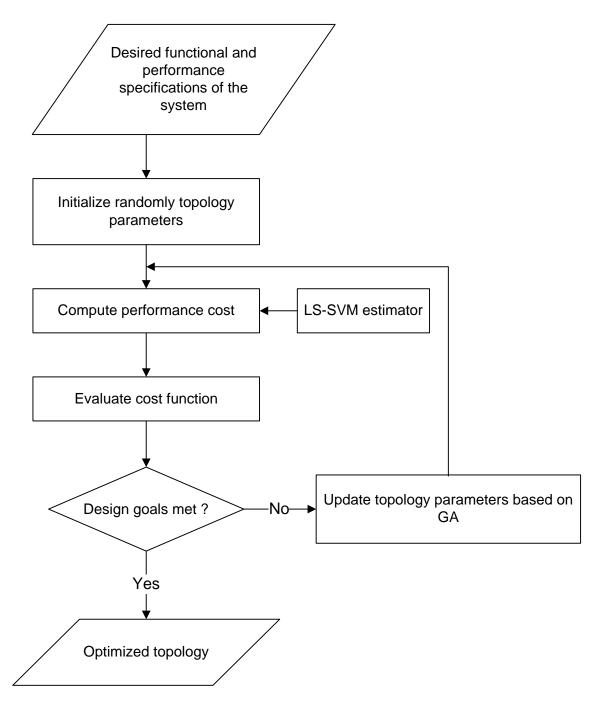

|   | 3.4 | Topole  | ogy Sizing Methodology using GA                                                                    | 47 |

|   | 3.5 | Exper   | imental Results                                                                                    | 47 |

|   |     | 3.5.1   | Experiment 1 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               | 49 |

|   |     | 3.5.2   | Experiment 2 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                        | 53 |

|   |     | 3.5.3   | Experiment $3 \ldots \ldots$ | 53 |

|   | 3.6 | Conclu  | usion                                                                                              | 60 |

| 4 | Top | -Down   | a Generation of an Optimal Topology                                                                | 63 |

|   | 4.1 | Top-D   | Oown Topology Generation Methodology                                                               | 64 |

|   |     | 4.1.1   | Outline of the Methodology                                                                         | 64 |

|   |     | 4.1.2   | Transfer Function and State Space Representation                                                   | 66 |

|   |     | 4.1.3   | Topology Generation                                                                                | 67 |

|   |     |         | 4.1.3.1 Functional Topology Generation                                                             | 68 |

|   |     |         | 4.1.3.2 Component-Level Topology Generation                                                        | 69 |

|   |     |         |                                                                                                    |    |

\_\_\_\_

|          |     | 4.1.4                    | Topology Transformation                                                                                                     | 71 |  |  |

|----------|-----|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|----|--|--|

|          |     | 4.1.5                    | Performance Estimation                                                                                                      | 76 |  |  |

|          |     |                          | 4.1.5.1 Sensitivity minimization                                                                                            | 76 |  |  |

|          |     |                          | 4.1.5.2 Hardware Complexity                                                                                                 | 79 |  |  |

|          |     |                          | 4.1.5.3 Relative Power Consumption                                                                                          | 80 |  |  |

|          |     | 4.1.6                    | Topology Exploration and Selection                                                                                          | 81 |  |  |

|          |     |                          | 4.1.6.1 Feasible $Gm$ Value Constraints $\ldots \ldots \ldots \ldots$                                                       | 81 |  |  |

|          |     |                          | 4.1.6.2 Non-overload Constraints                                                                                            | 82 |  |  |

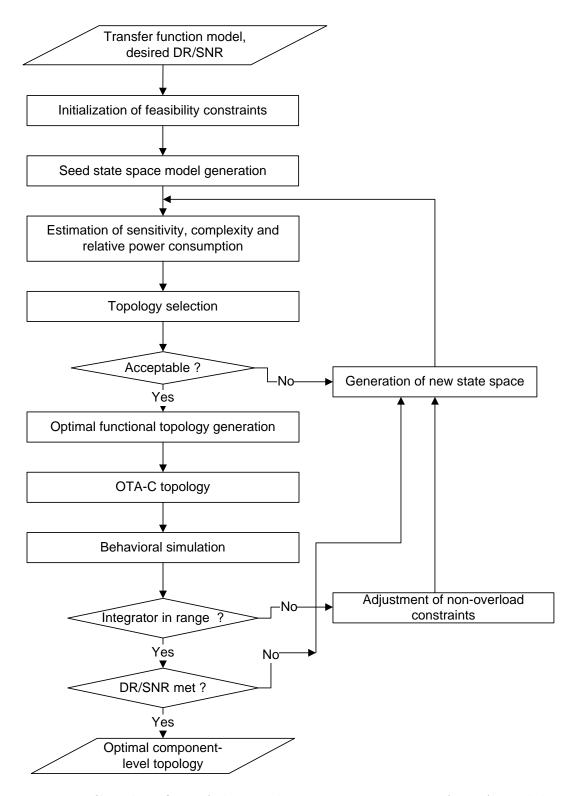

|          |     | 4.1.7                    | Complete Flow of the Topology Generation Process for CT                                                                     |    |  |  |

|          |     |                          | $\Sigma\Delta$ Modulator System                                                                                             | 82 |  |  |

|          |     |                          | 4.1.7.1 Related Work on $\Sigma\Delta$ Modulator Synthesis                                                                  | 83 |  |  |

|          |     |                          | $4.1.7.2  \text{Methodology}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                              | 85 |  |  |

|          | 4.2 | Comp                     | arison with Existing Methodologies                                                                                          | 85 |  |  |

|          | 4.3 | Exper                    | imental Results                                                                                                             | 87 |  |  |

|          |     | 4.3.1                    | Experiment 1 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 87 |  |  |

|          |     | 4.3.2                    | Experiment 2 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                        | 92 |  |  |

|          |     | 4.3.3                    | Experiment $3 \ldots \ldots$     | 95 |  |  |

|          | 4.4 | Conclu                   | usion                                                                                                                       | 00 |  |  |

| <b>5</b> | Hig | h-Leve                   | el Specification Translation 10                                                                                             | 03 |  |  |

|          | 5.1 | Proble                   | $\stackrel{-}{\operatorname{rem}}$                                                                                          | 03 |  |  |

|          | 5.2 | Feasib                   | ble Design Space Construction                                                                                               | 05 |  |  |

|          |     | 5.2.1                    | Application Bounded Space                                                                                                   | 05 |  |  |

|          |     | 5.2.2                    | Circuit Realizable Space                                                                                                    | 06 |  |  |

|          |     | 5.2.3                    | Feasible Design Space                                                                                                       | 07 |  |  |

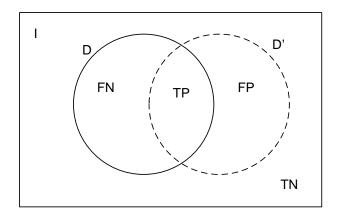

|          | 5.3 | Feasib                   | le Design Space Identification                                                                                              | 08 |  |  |

|          |     | 5.3.1                    | Accuracy Measurement                                                                                                        | 08 |  |  |

|          | 5.4 | Design Space Exploration |                                                                                                                             |    |  |  |

|          |     | 5.4.1                    | Cost Function Formulation                                                                                                   | 11 |  |  |

|          |     |                          | 5.4.1.1 Primary Objectives                                                                                                  | 11 |  |  |

|          |     |                          | 5.4.1.2 Secondary Objectives                                                                                                | 11 |  |  |

|          |     | 5.4.2                    | Exploration Algorithm $\ldots \ldots 1$ | 12 |  |  |

|          | 5.5 | Comp                     | arison with Existing Methodologies                                                                                          | 12 |  |  |

|          | 5.6 | Exper                    | imental Results                                                                                                             | 13 |  |  |

|          |     | 5.6.1                    | Experiment 1 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                           | 13 |  |  |

|              |     | 5.6.2 Experiment 2 $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $11'$                                                             |

|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |     | 5.6.3 Experiment $3 \ldots 119$                            |

|              | 5.7 | Conclusion                                                                                                                                                   |

| 6            | Con | clusion and Directions for Further Research 123                                                                                                              |

|              | 6.1 | Summary and Conclusions                                                                                                                                      |

|              |     | 6.1.1 Contributions $\ldots \ldots \ldots$   |

|              |     | 6.1.2 Tools developed $\ldots \ldots \ldots$ |

|              | 6.2 | Directions for Further Research                                                                                                                              |

| $\mathbf{A}$ | Lea | ast Squares Support Vector Machine 13                                                                                                                        |

|              | A.1 | Least-Squares Support Vector Regression                                                                                                                      |

|              | A.2 | Least-Squares Support Vector Classification                                                                                                                  |

| в            | Glo | bal Optimization Techniques 13'                                                                                                                              |

|              | B.1 | Genetic Algorithm                                                                                                                                            |

|              | B.2 | Simulated Annealing                                                                                                                                          |

# List of Figures

| 1.1  | Flow of a typical analog high-level design procedure                                              | 2  |

|------|---------------------------------------------------------------------------------------------------|----|

| 2.1  | Optimization-based design flow                                                                    | 17 |

| 2.2  | Simulink based behavioral model                                                                   | 21 |

| 3.1  | 2D projection of a four dimensional sample space                                                  | 36 |

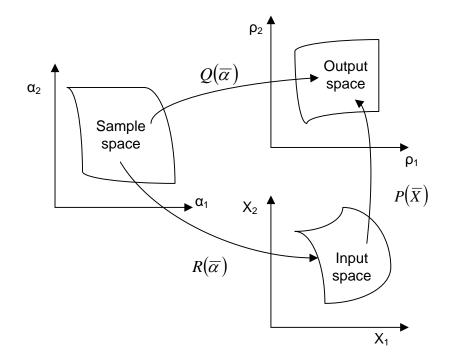

| 3.2  | Non-linear relation between the sample space and the input, output                                |    |

|      | space                                                                                             | 37 |

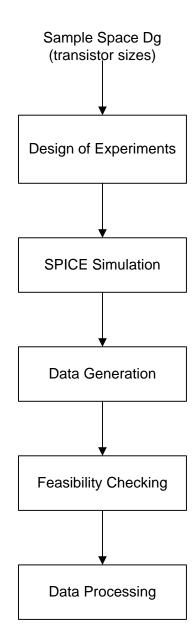

| 3.3  | An outline of the procedure for generation of training data                                       | 38 |

| 3.4  | Outline of GA-based hyperparameter selection procedure $\ . \ . \ . \ .$                          | 44 |

| 3.5  | Topology sizing methodology using GA optimizer with LS-SVM model                                  | 48 |

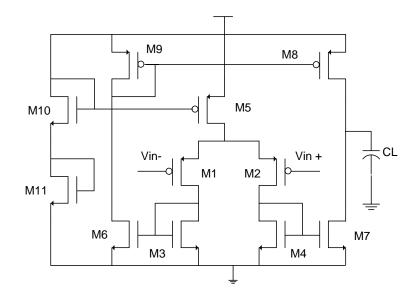

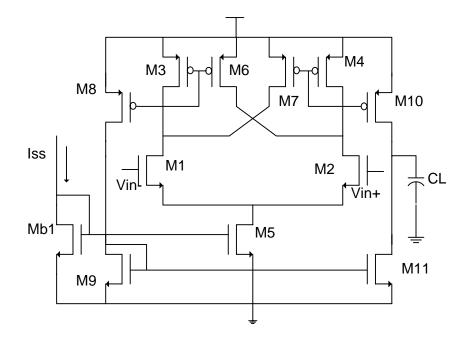

| 3.6  | PMOS OTA circuit                                                                                  | 49 |

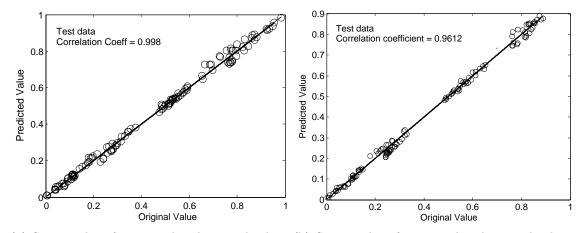

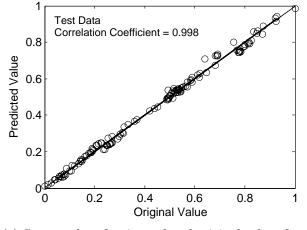

| 3.7  | Scatter Plot of the constructed models                                                            | 52 |

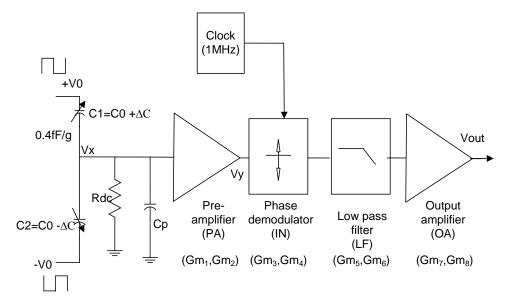

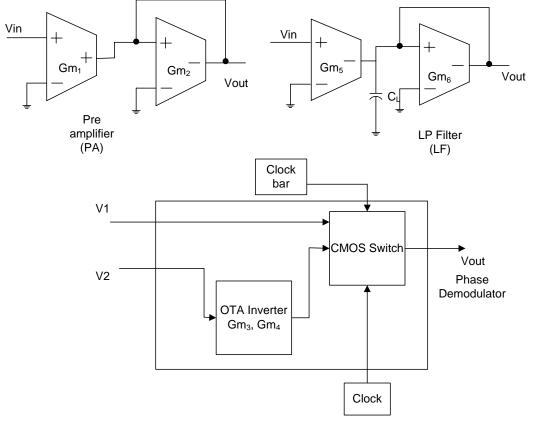

| 3.8  | Considered system for Experiment 3                                                                | 54 |

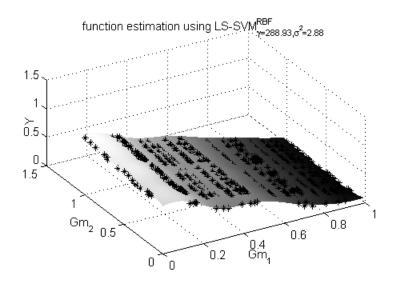

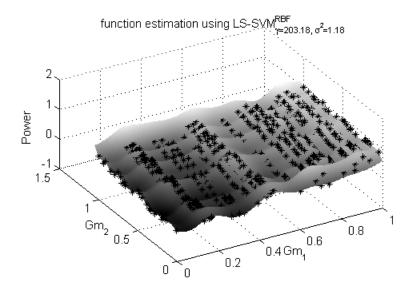

| 3.9  | Noise as function of $Gm_1$ and $Gm_2$                                                            | 58 |

| 3.10 | Power as function of $Gm_1$ and $Gm_2$                                                            | 58 |

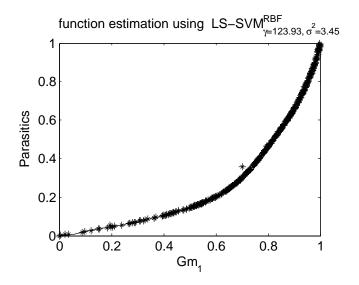

| 3.11 | Input parasitics as function of $Gm_1$                                                            | 59 |

| 4.1  | Top-down generation of an optimal topology for linear analog systems                              | 65 |

| 4.2  | Block diagram of a CT $\Sigma\Delta$ modulator $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 67 |

| 4.3  | Functional topology of a $4^{th}$ order CT $\Sigma\Delta$ modulator                               | 69 |

| 4.4  | Functional topology for a general $n^{th}$ order CT $\Sigma\Delta$ modulator                      | 70 |

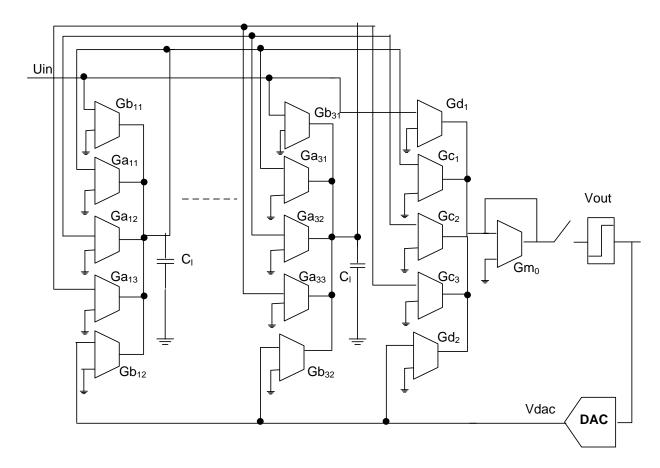

| 4.5  | A generic $3^{rd}$ order CT modulator with $GmC$ loop-filter. $(Ga_{ij} \equiv$                   |    |

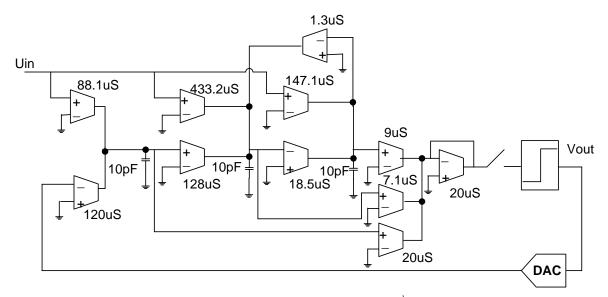

|      | $Gma_{ij}$ )                                                                                      | 71 |

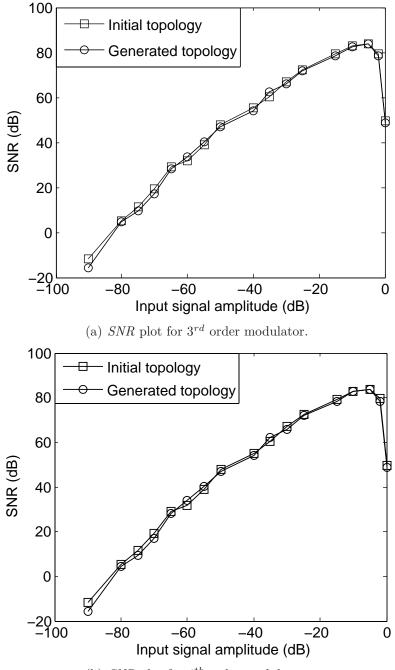

| 4.6  | SNR plot for two topologies generated through topology transforma-                                |    |

|      | tion, establishing the invariant property.                                                        | 75 |

| 4.7  | Complete flow of the topology generation process for $\Sigma\Delta$ modulator                                  |    |

|------|----------------------------------------------------------------------------------------------------------------|----|

|      | system                                                                                                         | 84 |

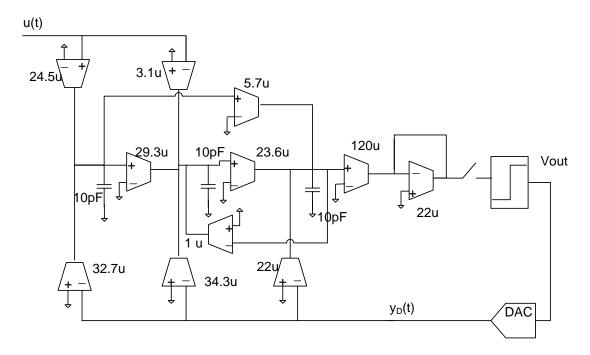

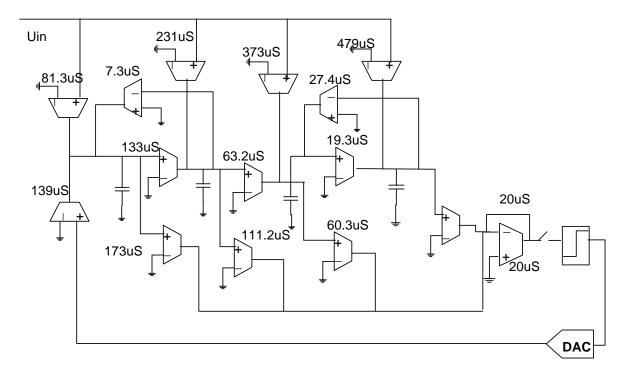

| 4.8  | The generated $3^{rd}$ order modulator topology                                                                | 88 |

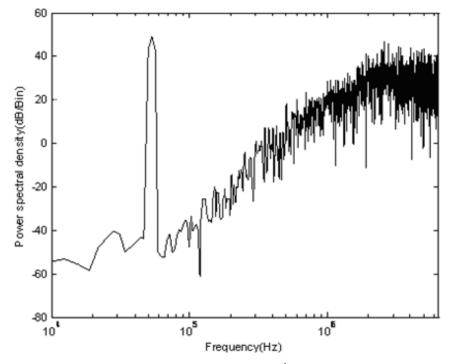

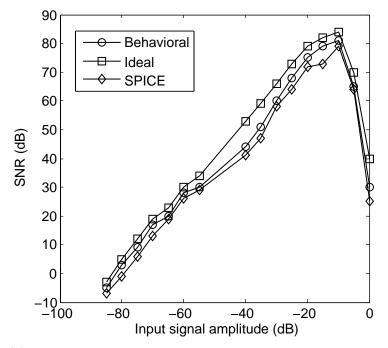

| 4.9  | Characterization of the generated $3^{rd}$ order modulator topology                                            | 90 |

| 4.10 | Chosen standard topologies of a $3^{rd}$ order modulator for comparison.                                       | 91 |

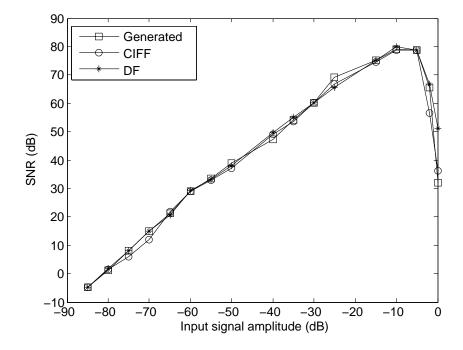

| 4.11 | SNR/DR comparison between the generated, CIFF and DF topology.                                                 | 92 |

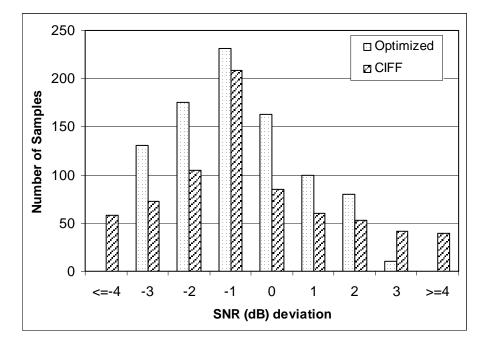

| 4.12 | Monte Carlo analysis plot for sensitivity comparison between the gen-                                          |    |

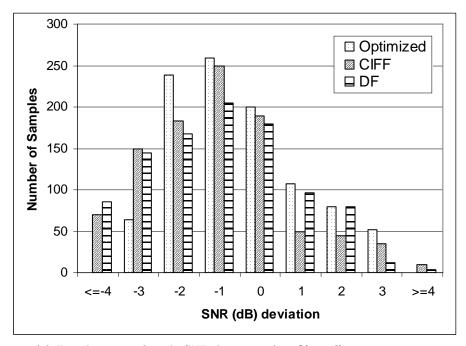

|      | erated (optimized), CIFF and DF topology                                                                       | 93 |

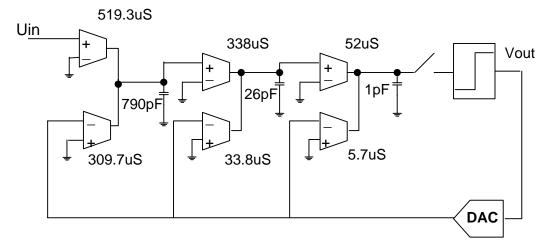

| 4.13 | The generated $4^{th}$ order modulator topology and the corresponding                                          |    |

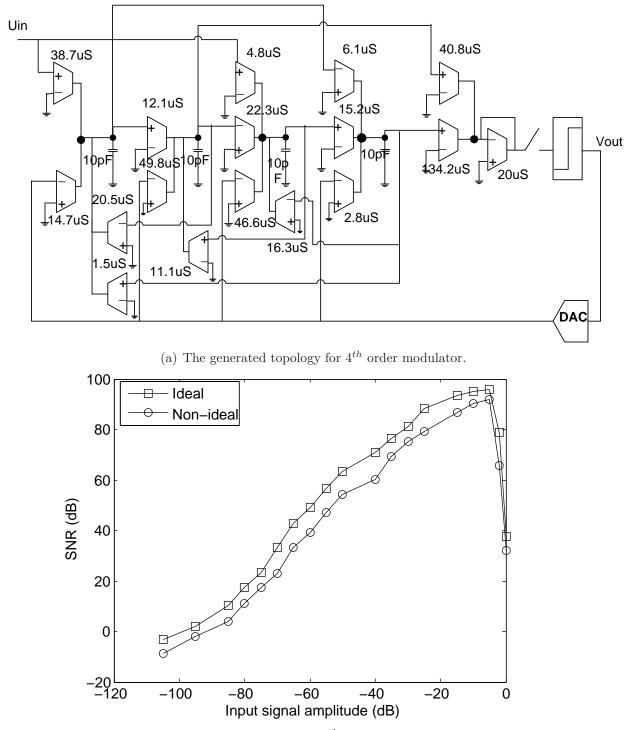

|      | SNR plot                                                                                                       | 97 |

| 4.14 | The CIFF $4^{th}$ order topology.                                                                              | 98 |

| 4.15 | Bar diagram of peak $SNR$ deviation for 5% coefficient variation for                                           |    |

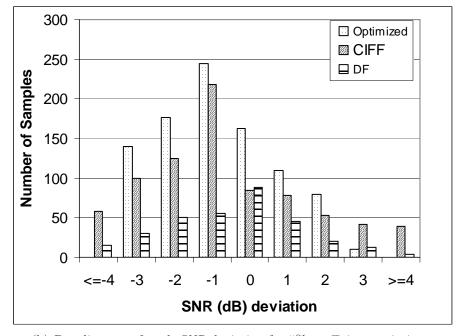

|      | the generated (optimized) and the CIFF $4^{th}$ order modulator topology.                                      | 99 |

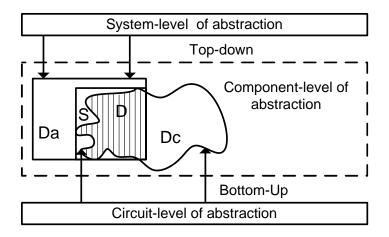

| 5.1  | Meet-in-the-middle way of constructing $\mathcal{D}, \mathcal{D} = \mathcal{D}_a \cap \mathcal{D}_c, S$ is the |    |

|      | search space                                                                                                   | 07 |

| 5.2  | Feasible design space and its subspaces                                                                        | 09 |

| 5.3  | DSE mechanism                                                                                                  | 10 |

| 5.4  | Considered system for experimentation                                                                          | 14 |

| 5.5  | SPICE output amplitude with 3 mV input                                                                         | 17 |

| 5.6  | $3^{rd}$ order OTA-C based $\Sigma\Delta$ modulator topology                                                   | 19 |

| 5.7  | Comparator circuit                                                                                             | 20 |

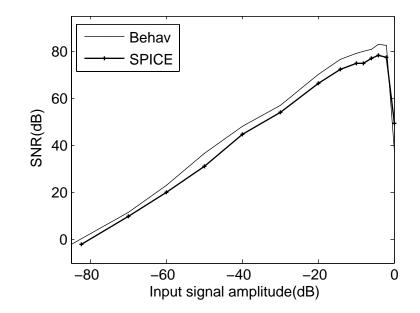

| 5.8  | Behavioral and SPICE simulated SNR plot of the modulator 1                                                     | 21 |

# List of Tables

| 3.1  | Transistor Sizes and Feasibility Constraints for OTA                                                                | 49  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

| 3.2  | Grid search technique using hold out method                                                                         | 50  |

| 3.3  | Grid search technique using 5-fold cross validation method $\ldots$                                                 | 50  |

| 3.4  | GA technique using hold out method                                                                                  | 51  |

| 3.5  | GA technique using 5-fold cross validation                                                                          | 51  |

| 3.6  | Comparison between GA and Grid search technique for LS-SVM con-                                                     |     |

|      | struction                                                                                                           | 51  |

| 3.7  | Construction of Nonlinear Performance Model $\ . \ . \ . \ . \ . \ .$                                               | 53  |

| 3.8  | Comparison between our methodology and EsteMate $\hfill \ldots \ldots \ldots$ .                                     | 53  |

| 3.9  | Functional Specs and Design constraints                                                                             | 55  |

| 3.10 | Transistor Sizes and Feasibility Constraints for Preamplifier $\ . \ . \ .$                                         | 56  |

| 3.11 | Accuracy of Preamplifier block                                                                                      | 56  |

| 3.12 | Synthesized Topology Parameters                                                                                     | 60  |

| 3.13 | Comparison of Predicted performances and SPICE value                                                                | 60  |

| 4.1  | Non-idealities of the OTA-C component blocks                                                                        | 74  |

| 4.2  | Non-idealities considered $\ldots$ | 89  |

| 4.3  | Comparision of behavior under ideal and non-ideal conditions $\ldots$ .                                             | 89  |

| 4.4  | Comparison in terms of yield for coefficient variation $\ldots \ldots \ldots$                                       | 92  |

| 4.5  | Comparison between the topologies for relative power and complexity                                                 | 95  |

| 4.6  | Comparision of behavior under ideal and non-ideal conditions: $4^{th}$                                              |     |

|      | order modulator                                                                                                     | 96  |

| 4.7  | Comparison in terms of yield for coefficient variation: $4^{th}$ order mod-                                         |     |

|      | ulator                                                                                                              | 96  |

| 4.8  | Comparison between the topologies for relative power and complexity                                                 | 98  |

| 5.1  | Application bounded constraints: Experiment 1                                                                       | 115 |

| 5.2  | Circuit Realizable Constraints: PA block                                                                                                                                       |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3  | SVM Performances: Experiment 1                                                                                                                                                 |

| 5.4  | Translated Specifications: Experiment 1                                                                                                                                        |

| 5.5  | GA results: averaged over 10 runs, 3.0 GHz 512 MB RAM PIV PC $$ . 116 $$                                                                                                       |

| 5.6  | End results: Experiment 1 and 2                                                                                                                                                |

| 5.7  | Application bounded constraints: Experiment 2 $\ldots \ldots $ |

| 5.8  | SVM Performances: Experiment 2                                                                                                                                                 |

| 5.9  | Translated Specifications: Experiment 2                                                                                                                                        |

| 5.10 | Feasibility constraints for OTA and Comparator: Experiment 3 $~$ 120 $~$                                                                                                       |

| 5.11 | Translated Specifications: Experiment 3 $\ldots \ldots $       |

| 5.12 | End results: Experiment 3                                                                                                                                                      |

# Abbreviations and Symbols

| ADC    | Analog-to-Digital Converter                   |

|--------|-----------------------------------------------|

| AMS    | Analog Mixed Signal                           |

| ANN    | Artificial Neural Network                     |

| С      | Capacitor                                     |

| CIFF   | Cascaded Integrator Feed Forward              |

| CMOS   | Complimentary Metal Oxide Semiconductor       |

| DF     | Distributed Feedback                          |

| DR     | Dynamic Range                                 |

| DSE    | Design Space Exploration                      |

| GA     | Genetic Algorithm                             |

| IC     | Integrated Circuit                            |

| LS-SVM | Least Squares Support Vector Machine          |

| MEMS   | Micro Electromechanical Systems               |

| NTF    | Noise Transfer Ratio                          |

| OTA    | Operational Transconductance Amplifier        |

| PLL    | Phase Locked Loop                             |

| RBF    | Radial Basis Function                         |

| RF     | Radio Frequency                               |

| SA     | Simulated Annealing                           |

| SFG    | Signal Flow Graph                             |

| SNR    | Signal-to-Noise Ratio                         |

| SPICE  | Simulator Program with Integrated Circuit Em- |

| SRM    | phasis<br>Structural Risk Minimization        |

| STF    | Signal Transfer Ratio                         |

| SVM    | Support Vector Machine                        |

| B      | Parameterized behavioral models               |

|        |                                               |

| $\bar{X}$                                       | Set/vector of design variables/parameters |

|-------------------------------------------------|-------------------------------------------|

| $ar{ ho}$                                       | Set/vector of performance parameters      |

| Р                                               | Performance model                         |

| $\Sigma\Delta$                                  | Sigma Delta                               |

| ${\mathbb D}_{lpha}$                            | Circuit-level design space                |

| ${\mathbb D}_g$                                 | Design space                              |

| $\mathfrak{D}_a$                                | Application-bounded specification space   |

| $\mathfrak{D}_c$                                | Circuit-realizable specification space    |

| $\gamma$                                        | Regularization parameter                  |

| $\sigma^2$                                      | RBF kernel parameter                      |

| ARE                                             | Average relative error                    |

| R                                               | Correlation Coefficient                   |

| Gm                                              | OTA transconductance value                |

| $C_L$                                           | Load Capacitance                          |

| L(s)                                            | Transfer function in s domain             |

| $(\mathbf{A},\mathbf{B},\mathbf{C},\mathbf{D})$ | State space matrix tuple                  |

| T                                               | Component-level topology                  |

| $\mathfrak{T}_F$                                | Functional topology                       |

| $S_{L12}$                                       | L12 norm of the sensitivity function      |

| W                                               | Observability Gramian matrix              |

| Κ                                               | Controllability Gramian matrix            |

| Т                                               | Topology transformation operator          |

|                                                 |                                           |

# Chapter 1

# Introduction

The growing complexity of CMOS integrated systems being designed today, together with the increasing fragility of analog component blocks brought about by shrinking geometries and reduced power consumption, pose tremendous challenges to traditional analog integrated circuit (IC) designers to produce satisfactory results in a short time. This situation has created a strong interest among the designers in developing new design methodologies and supporting computer aided design tools. The new IC design methodologies such as top-down constraint-driven methodology, platform-based design, etc., are based on a hierarchy of abstraction levels: system design, architectural design, cell design, cell layout and system layout design [1, 2, 3]. The design task that is performed at the architectural level of abstraction is referred to as high-level design. This includes decomposition of the system into an architecture consisting of functional component blocks, e.g., amplifiers, filters, ADCs, etc., that are required to realize the specified behavior of the system [3].

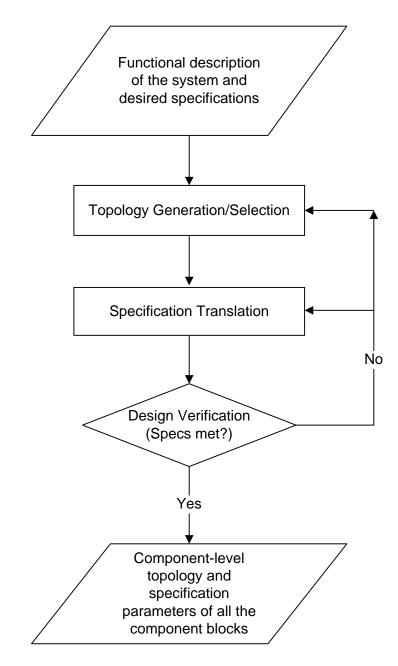

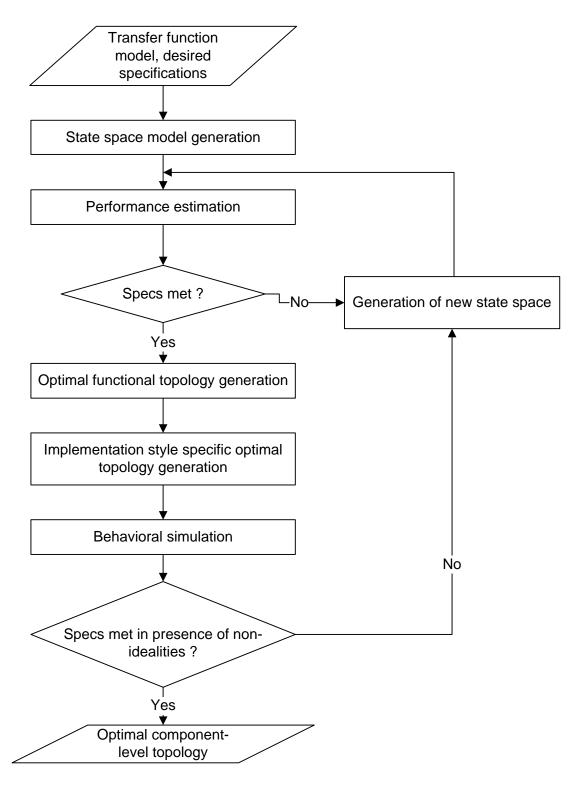

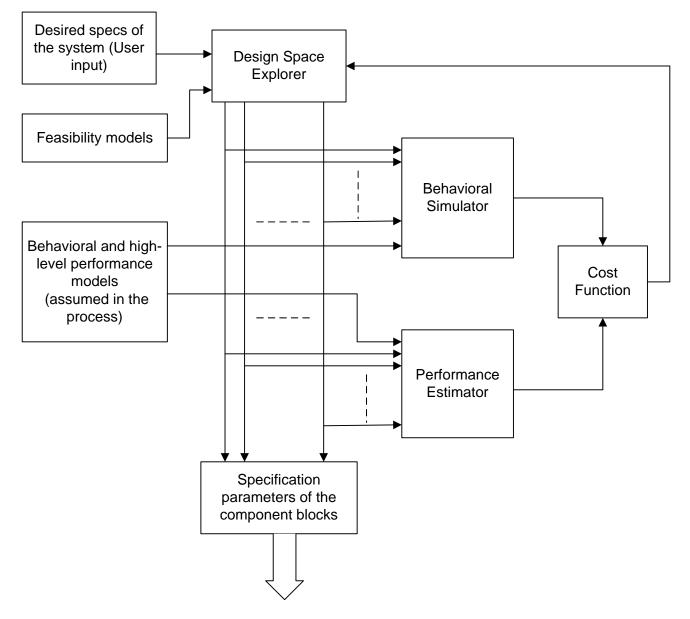

An analog high-level design process is defined as the translation of analog systemlevel specifications into a proper topology of component blocks, in which the specifications of all the component blocks are completely determined so that the overall system meets its desired specifications [4, 5]. The system-level specifications include a functional description of the system and the desired functional and performance specifications. Examples of component blocks are integrators, adders, mixers, etc. The flow of a typical analog high-level design procedure is illustrated in Fig. 1.1 [4]. The analog high-level design process consists of three steps. The first step includes the task of selecting a suitable topology, i.e., an interconnection of lower-level component blocks that is capable of realizing the desired behavior. This phase of

Figure 1.1: Flow of a typical analog high-level design procedure

the analog high-level design process is called topology generation/selection. At the architecture/high-level design abstraction level, the component blocks of a topology are generally represented by their behavioral models and so at this level the topologies are sometimes referred to as high-level topologies. In the second step, the specifications of the system under design are mapped into individual specifications for each of the component blocks of the selected high-level topology, so that the complete system meets its specifications, while possibly optimizing the design toward some application-specific design objectives (e.g., minimal power consumption). This process is referred to as specification translation [2, 3]. In the third step, the correctness of the first two steps is verified, generally through behavioral simulation. If the desired specifications of the system are not met, then one or both of the first two steps are repeated.

There are three different approaches for analog high-level design [4]. Of them, two are optimization-based approaches (simulation-based and equation-based) and one is a library-based approach. The optimization-based high-level design methodology is the subject matter of this thesis. The present research work develops methodologies for implementing three different tasks of an optimization-based analog high-level design process. These are (i) high-level performance estimation, (ii) generation of an optimal component-level topology of a system and (iii) high-level specification translation.

The rest of the chapter is organized as follows. Section 1 presents a comprehensive survey of literature on the above mentioned topics that led to the motivation behind the present work. Section 2 defines the specific problems that have been addressed in the present work, gives an overview of the present research work and highlights the specific contributions of the thesis. Finally, Section 3 outlines the organization of the rest of the thesis.

### 1.1 Literature Survey and Motivation

In this section, we present a comprehensive survey of the literature related to the following topics (i) high-level performance estimation, (ii) topology generation and (iii) specification translation. This provides us the motivation behind the present work.

### 1.1.1 Analog Performance Modeling

An analog performance estimation (APE) tool for high-level synthesis of analog integrated circuits is described in [6, 7]. It takes the design parameters (e.g., transistor sizes, biasing) of an analog circuit as inputs and determines its performance parameters (e.g., power consumption, thermal noise) along with anticipated sizes of all the circuit elements. The tool is structured as a hierarchical estimation engine containing performance models of analog circuits at various levels of abstraction like simple analog circuits (current mirrors, V-I converters, etc.), operational amplifiers, and analog library cells (integrators, filters, amplifiers, etc.). The estimates are propagated through all the levels using symbolic equations that relate them. The estimator is fast to evaluate but the accuracy of the estimated results with respect to real circuit-level simulation results is not good. This is because the performance equations are based on simplified MOS models (SPICE level 1 equations). A power estimation model for ADC using empirical formulae is described in [8]. Although this is fast, the accuracy with respect to real simulation results under all conditions is off by orders of magnitude. The same reference [8] describes another approach for estimating power consumption of analog filters. Apart from using generic theoretical formulae, additional information such as the topology and the type of the filter are taken into consideration for improving the accuracy level. The technique for generation of posynomial equation-based performance estimation models for analog circuits like opamps, multistage amplifiers, switch capacitor filters, etc., is described in [9, 10]. An important advantage of such a modeling approach is that the topology sizing process can be formulated as a geometric program, which is easy to solve through very fast techniques. However, there are several limitations of this technique. The derivation of performance equations is often a manual process, based on simple MOS equations. In addition, although many analog circuit characteristics can be cast in posynomial format, this is not true for all characteristics. For such characteristics, often an approximate representation is used. An automatic procedure for generation of posynomial models using fitting technique is described in [11, 12]. This technique overcomes several limitations of the handcrafted posynomial modeling techniques. The models are built from a set of data obtained through SPICE simulations. Therefore, full accuracy of SPICE simulation is achieved through such performance models. A limitation of the fitting technique is that a good model template needs to be selected before the construction process and the quality of the estimated results depends upon the chosen template. The model selection process is often a difficult task. In [13] a method has been presented to automatically generate compact symbolic performance models of analog circuits with no prior specification of an equation template. A neural network based tool for automated power and area estimation is described in [14]. Circuit simulation results are used to train a neural network model, which is subsequently used as an estimator. Fairly recently, support vector machine (SVM) has been used for modeling of performance parameters for RF and analog circuits [15, 16, 17]. Analog performance models constructed with regression technique are generally fast to evaluate and the accuracy with respect to circuit-level simulation results is also good. An important advantage of a non-parametric regression technique (e.g., SVM technique) over a parametric regression technique (e.g., curve-fitting technique) is that it does not require any model template. However, a major limitation of the non-parametric regression technique is that, the generalization ability of the constructed models is often not good. In addition, the model construction time is generally high which increases the design overhead.

In this work, we have explored the possibility of developing a methodology for generating a high-level performance model with good generalization ability and low construction time using non-parametric regression technique.

#### 1.1.2 Generation/Selection of an Optimal System Topology

A fairly complete survey of the methodologies for generation/selection of an optimal system topology has been presented in [18]. There are three main classes of techniques for a high-level topology generation and selection process. They are: (i) selection before or after sizing, (ii) selection during sizing and (iii) top-down generation.

There are several approaches for the selection mechanism in the 'selection before or after sizing' technique. In [19], the topology selection tool selects only those topologies from the library that are able to satisfy the specifications of the component blocks as determined in the specification sheet and ranks them in order of preference. In [20], a figure-of-merit function is computed using behavioral models which estimates the trade-off between several performances. This function is used for guiding the topology selection process. In [5, 21], techniques are used to optimize the performances of each topology present in a library. From them, the best one is selected. Similar technique has been used for the selection of an optimal topology for  $\Sigma\Delta$  modulator in [22, 23, 24].

The 'selection during sizing' technique is based on the use of topology templates. For selection of an optimal opamp topology, this approach has been used in [25]. At the architectural level, this has been used in [26] for selection of an optimal topology for  $\Sigma\Delta$  modulator system.

A drawback of the design strategies based on selection before, during or after sizing is that all the available topologies are selected from a library, either entirely or as a template with a few binary options for component blocks or interconnections. On the other hand, strategies which create the topology offer a wider design range. The 'top-down generation' technique for topology generation has been followed in [7, 27, 28]. The topology generation methodology starts from a signal flow graph (SFG) description of the functional topology  $^{1}$  of a system. In [7], a branch-andbound algorithm first generates alternative component-level topologies by mapping SFG components to circuit-level component blocks, stored in a library. For each resultant topology, a genetic algorithm-based technique is used for constraint transformation such that an optimal component-level topology is finally selected. In [27], a tabu search method and heuristic conversion rules are used to find different opamp-based topologies for linear analog systems. Through a parametric optimization procedure, an optimal component-level topology is finally generated. In [28], genetic algorithm has been used for simultaneous architectural and parametric optimization. For all these methodologies, the starting SFG description of the system is a relatively low level description and is oriented to a specific functional topology. These methodologies therefore, do not consider the task of generation of an optimal functional topology of a system. However, for several complex analog component blocks/systems, e.g.,  $\Sigma\Delta$  modulator, higher order state variable filters, there exists several functional topologies and an optimal functional topology needs to be selected prior to the component-level topology generation process. In [29], component-level topologies for analog filters have been generated from a transfer function model. This is a relatively higher level of description. The functional topologies of the filters are generated from the transfer function. The component-level topologies are generated by mapping the functional component blocks to circuit-level implementation style specific realizations. However, this method does not include any

<sup>&</sup>lt;sup>1</sup>A functional topology of a system is an interconnection of a set of functional component blocks, e.g., adder, integrator, realizing the desired functionality of the system.

performance optimization procedure within it. Therefore, the aspect of generation of an optimal component-level topology is not addressed.

In this work, we have explored the possibility of developing a methodology for generating an optimal functional and component-level topology of a system from a high-level description of the system (e.g., transfer function model).

#### 1.1.3 High-Level Specification Translation

A high-level specification translation procedure is implemented through a design space exploration procedure. The crucial components of a specification translation procedure are the feasibility models of the component blocks of the system topology and an exploration algorithm. The feasibility models are required for limiting the design space exploration procedure to generate realizable values of the component block specifications. [30] presents a technique for construction of the feasibility models using binary search techniques - radial binary search and vertical binary search. [31] presents two methods for the calculation of the feasible performance values of analog circuits. The first method [32] computes the Pareto-optimal trade-offs of competing performances with full simulator accuracy. The Pareto front is a part of the boundary of the feasible performance region. The second method [33] computes linear polytopal approximations to the feasible performance region. This technique provides only an approximate representation of the feasible design space. Another method that identifies the entire range of feasible performance values using support vector machine principle has been presented in [34]. This technique considers only the circuit realizable space while constructing the feasible design space. Application system specific constraints and mutual influence between the component blocks have not been considered. An approximation to the feasible performance region by box constraints has been presented in [19]. A directed interval-based search space profiling technique and a genetic optimization-based constraint transformation technique are described in [35]. The constructed feasibility models are used in conjunction with an optimization algorithm to implement a specification translation process [19, 31, 35, 36, 37]. The standard optimization algorithms like simulated annealing, genetic algorithm etc., are used to implement the design space exploration procedure.

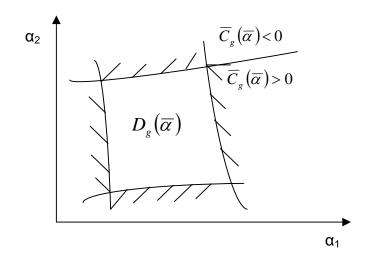

In this work, we have explored the possibility of developing a methodology for constructing the feasible design space by incorporating application system constraints and mutual influence among the component blocks. Further, we seek to identify the feasible design space accurately and develop an exploration procedure for high-level specification translation.

### 1.2 Overview and Contributions of the Thesis

This section first identifies the problems that have been addressed in this thesis and then gives a brief overview of the methodologies adopted to address them. Finally, the major contributions of this thesis are summarized.

#### 1.2.1 Problem Definition

The emphasis of this thesis is on optimization-based methodologies for the different tasks related to analog high-level design. The specific problems that have been addressed in this thesis are as follows:

- 1. Development of a systematic methodology for construction of high-level analog performance models with good generalization ability and low construction time using non-parametric regression technique.

- 2. Development of a methodology for top-down generation of an optimal functional and component-level topology for linear analog systems, starting from a high-level description of the system.

- 3. Development of a methodology for construction and accurate identification of a feasible design space and an exploration technique for high-level specification translation.

The following sub-sections give an overview of the approaches for solving these problems.

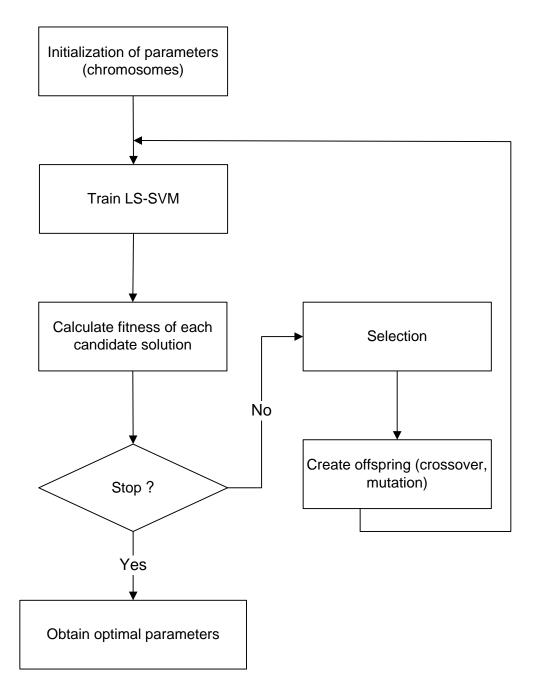

### 1.2.2 Generation of High-Level Performance Models

The thesis presents a methodology for generation of high-level performance models for analog component blocks using non-parametric regression technique. The transistor sizes of the circuit-level implementations of the component blocks along with a set of geometry constraints applied over them define the sample space. A Halton sequence generator is used for extracting samples from the sample space. Performance data are generated by simulating each sampled circuit configuration through SPICE. For training of the model, only those samples are considered which satisfy a set of functional and performance constraints. Least squares support vector machine (LS-SVM) is used as a non-parametric regression function. Optimal values of the model hyper parameters are determined using two techniques - grid search-based technique and genetic algorithm (GA)-based technique. The generalization ability of the constructed models is estimated using a hold out method and a 5-fold cross validation method. Average relative error and correlation coefficients are calculated for measuring the quality of the constructed models. The constructed performance estimation models are used in a genetic algorithm-based high-level topology sizing process.

The methodology is demonstrated with a set of experiments which are as follows:

- 1. Performance models corresponding to thermal noise, power consumption and output impedance of an operational transconductance amplifier are developed as functions of its specification parameters. The quality measures of the models are computed. The models are found to be quite accurate.

- 2. A comparison between the models constructed using the grid search-based training technique and the GA-based training technique w.r.t. the generalization ability and the training time is made. It is found that the training time is considerably less for the GA-based training technique compared to the grid search-based training technique, with almost the same generalization ability.

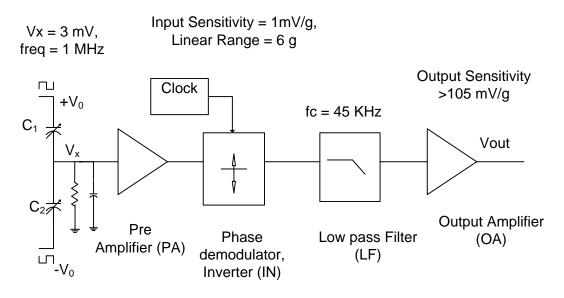

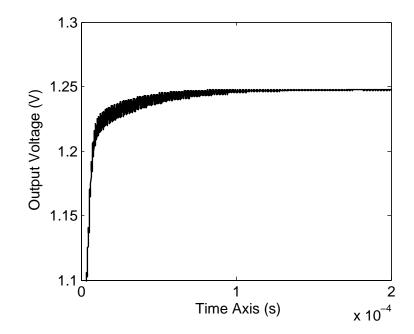

- 3. To demonstrate the topology sizing process, the interface electronics for a MEMS capacitive accelerometer has been chosen as an example. The topology parameters are determined such that a given set of specifications is satisfied with optimized performances. The predicted performances are compared with the SPICE simulation results. The two sets of results match closely.

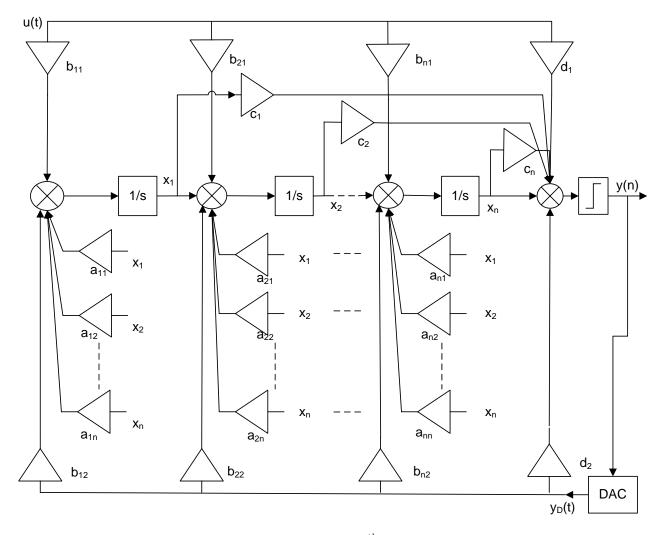

### 1.2.3 Top-Down Methodology for Generation of an Optimal Topology for Linear Analog Systems

The thesis then presents a methodology for top-down generation of an optimal functional and component-level topology for linear analog systems, starting from a transfer function model of the system. The given transfer function model is converted to a state space matrix model. This acts as the basis for generation of topologies of the system. The topology exploration process is modeled as a state space matrix exploration process. A similarity transformation matrix is used for generation of new state space models from a given one. These new topologies have identical behavioral properties, but different performance properties. A simulated annealing-based optimization technique is used to determine an optimal state space model such that the resultant topology is optimized for a set of performance parameters. The optimized state space model is realized by functional component blocks to generate an optimal functional topology, which is subsequently realized by appropriate analog component blocks to generate an optimal component-level topology of the system. The generated topology is then behaviorally simulated to check whether all the desired specifications are satisfied even in the presence of circuit-level non-idealities. If the test fails, the complete process is repeated and a new optimized topology is generated.

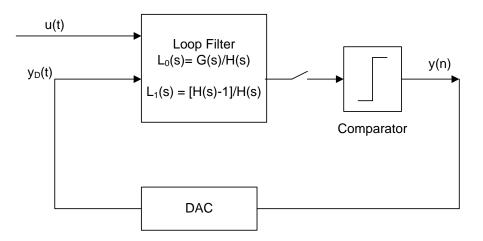

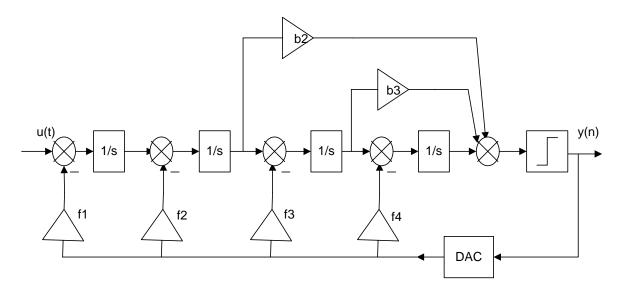

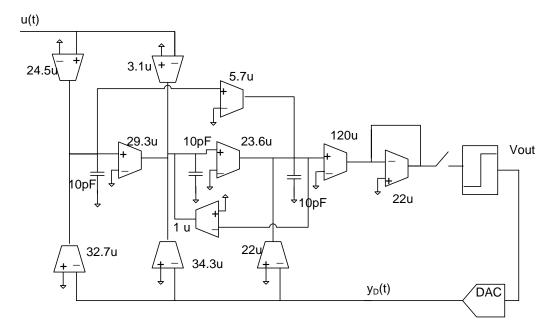

As a case study, the thesis presents a methodology for generation of an operational transconductance amplifier (OTA)-capacitor (C) based optimal topology for continuous-time  $\Sigma\Delta$  modulator. The loop filter transfer functions and the desired dynamic range specifications are taken as inputs. The chosen performance metrics are system hardware complexity, sensitivity under parameter variation and relative power consumption. A  $3^{rd}$  order and a  $4^{th}$  order modulator have been chosen as examples for experimentation. The experiments that have been carried out for each of the examples are as follows:

- 1. The behavioral equivalence of the newly generated topologies under non-ideal conditions is validated through behavioral simulation. The dynamic ranges of the topologies are determined. These are found to be nearly equal.

- 2. The generated topology is behaviorally simulated to check whether it satisfies the desired dynamic range under non-ideal conditions and non-overload conditions. It is found that the generated topology satisfies the desired dynamic range under non-ideal conditions and overloading does not take place.

- 3. The performances of the generated topology are compared with that of two standard topologies. Monte Carlo analysis is performed for comparing the sensitivity performances. The yield and performance deviation are computed. It is found that the generated topology is more tolerant to design parameter

variations not only in terms of yield but also performance deviations.

4. The relative power consumption is computed for the generated topology and the two standard topologies. It is found that the generated topology has lower relative power consumption compared to the standard topologies.

#### **1.2.4** High-Level Specification Translation

Finally, the thesis presents a methodology for high-level specification translation. A meet-in-the-middle approach is followed for the construction of a feasible design space. This is constructed as the intersection of an application bounded specification space and a circuit realizable specification space. The former is constructed through a top-down procedure using interval analysis techniques and the latter, via a bottom-up procedure through actual circuit simulation. Least squares support vector machine (LS-SVM)-based classification technique is used to identify an accurate geometry of the actual feasible design space. Genetic algorithm (GA) is used to explore the feasible design space. The final solution point is kept away from the feasible design space boundary, in order to increase the tolerance of the component-specifications.

Two case studies, an interface electronics for MEMS capacitive accelerometer sensor and a continuous-time  $\Sigma\Delta$  modulator have been presented to demonstrate the effectiveness of the procedure. The experiments that are carried out for each case study are as follows:

- LS-SVM feasibility models are constructed for all the component blocks. A set of performance metrics, viz., sensitivity, specificity and accuracy are computed. These values are found to be close to their ideal values.

- 2. GA-based design space exploration procedure determines the specification parameters of the component blocks.

- 3. With the determined specifications of the component blocks, the target systems are implemented at the transistor level and are simulated with SPICE. The SPICE simulation results satisfy the desired specifications of the system, validating the overall procedure.

#### 1.2.5 Contributions

This work has three major contributions as listed below.

- 1. A methodology is developed for the generation of good high-level performance estimation models for analog component blocks using least squares support vector machine (LS-SVM). The constructed models are accurate with respect to real circuit-level simulation results, fast to evaluate and have a good generalization ability. In addition, the model construction time is low and the construction process does not require any detailed circuit design knowledge.

- 2. A methodology is developed for generation of an optimal functional and componentlevel topology for linear analog systems, starting from a transfer function model of the system. The generated topology is ensured to perform satisfactorily under circuit-level non-ideal conditions. Through this methodology, the designer is able to specify the design goal and the desired specifications at a higher level of abstraction in terms of transfer functions, while the design tool is able to generate an optimal component-level topology directly from the transfer functions in a highly automated manner.

- 3. A methodology is developed for construction and accurate identification of a feasible design space and also for an exploration technique for high-level specification translation. Through this methodology, it is possible to obtain a set of practically correct circuit level specifications of the component blocks of a system through a fast exploration process in a single pass.

The present methodologies make the high-level design process fast and accurate. In addition, these can even be followed by novice users.

## **1.3** Organization of the rest of the Thesis

This section presents an outline of the organization of the rest of the thesis.

**Chapter 2**: It gives an overview of an optimization-based generic methodology for topology sizing and specification translation task. It also discusses in brief the state-of-the art techniques for construction of high-level models, viz., performance models, behavioral models and feasibility models and various optimization methods. The basic principles of the various methods for the generation/selection of an optimal component-level topology are also discussed.

**Chapter 3**: This chapter describes a methodology for the construction of a highlevel performance model using least squares SVM technique. It also includes a GA based topology sizing procedure, where the constructed performance models are used. Experimental results are provided to demonstrate the effectiveness of the methodology.

**Chapter 4**: This chapter describes a methodology for top-down generation of an optimal component-level topology for linear analog systems. As a case study, a continuous-time  $\Sigma\Delta$  modulator system is presented. Experimental results are provided to illustrate the effectiveness of the methodology.

**Chapter 5 :** This chapter describes a methodology for high-level specification translation. Feasible design space is identified accurately using least squares SVM technique. GA-based optimization technique is used for design space exploration. Experimental results are provided to demonstrate the effectiveness of the methodology.

**Chapter 6 :** The major contributions of this thesis are summarized in this chapter and some pointers to future research are provided therein.

## Chapter 2

# Optimization-based Analog High-Level Design Methodology

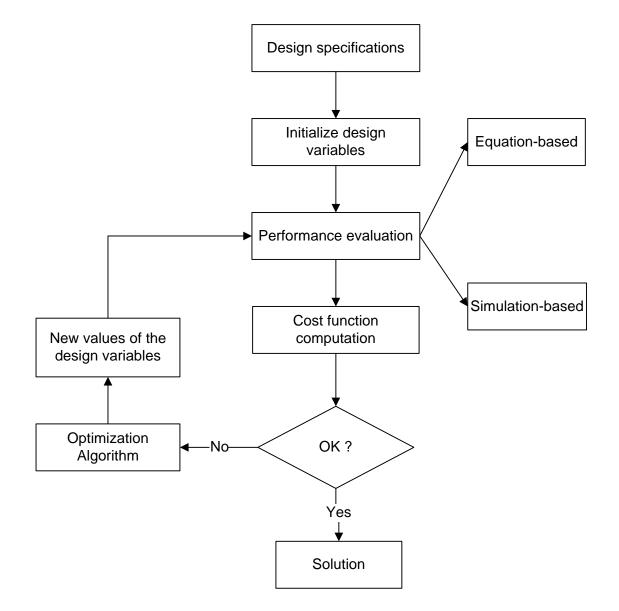

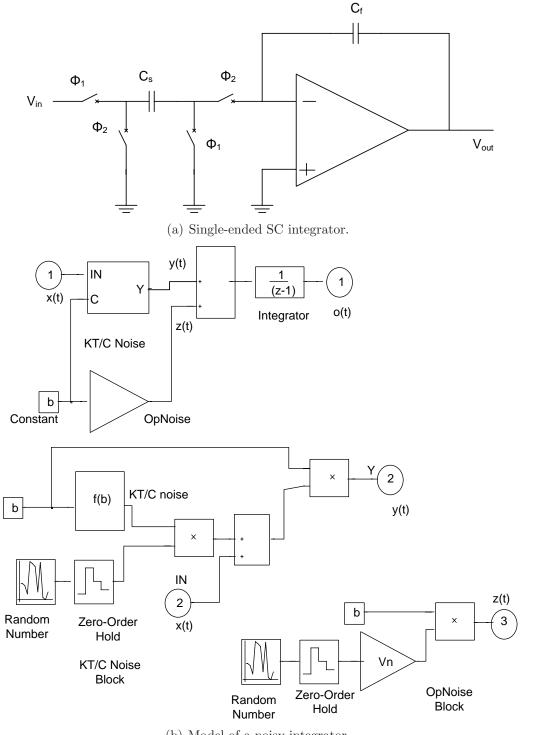

The flow diagram of a general procedure for an analog high-level design process was shown in Fig. 1.1. As mentioned in the previous chapter, there are three different methodologies for an analog high-level design process. Of them, two are optimization-based methods (one with simulations in the loop, and the other with analytical equations) and one is a library-based method. The optimization-based methodology which is the subject matter of this thesis is discussed in this chapter. At the heart of an optimization-based methodology lies several classes of high-level models such as performance models, behavioral models, etc., and an optimization procedure. This chapter presents an overview of the basic principle of the state-ofthe art techniques for constructing these models and the optimization procedures. It also includes a brief survey of the existing techniques for generation/selection of an optimal component-level topology of a system. The techniques that are used in the present research work are identified within the chapter. This chapter therefore, provides the necessary background required for understanding the contributions of the present work.

The chapter is organized as follows. Section 1 presents a generic methodology of an optimization-based high-level design procedure. It discusses the simulationbased approach and the equation-based approach for high-level design. Section 2 discusses the state-of-the art techniques for construction of the different high-level models. Section 3 discusses the various methods of optimization procedures. Section 4 presents an overview of the various techniques for generation/selection of system topologies. Finally, Section 5 presents a summary of the chapter.

## 2.1 Generic Methodology