# FORMAL VERIFICATION OF BEHAVIOURAL TRANSFORMATIONS DURING EMBEDDED SYSTEM DESIGN

Chandan Karfa

### FORMAL VERIFICATION OF BEHAVIOURAL TRANSFORMATIONS

### **DURING EMBEDDED SYSTEM DESIGN**

*Thesis submitted in partial fulfillment of the requirements for the award of the degree*

of

### **Doctor of Philosophy**

by

### **Chandan Karfa**

Under the supervision of

Dr. Chittaranjan Mandal and Dr. Dipankar Sarkar

### **Department of Computer Science and Engineering**

Indian Institute of Technology, Kharagpur

September 2011

© 2011 Chandan Karfa. All Rights Reserved.

### APPROVAL OF THE VIVA-VOCE BOARD

Certified that the thesis entitled **"Formal Verification of Behavioural Transformations during Embedded System Design**" submitted by **Chandan Karfa** to the Indian Institute of Technology, Kharagpur, for the award of the degree of Doctor of Philosophy has been accepted by the external examiners and that the student has successfully defended the thesis in the viva-voce examination held today.

(Member of the DSC)

(Member of the DSC)

(Member of the DSC)

(Member of the DSC)

(Supervisor)

(Supervisor)

(External Examiner)

(Chairman)

Date:

### CERTIFICATE

This is to certify that the thesis entitled **"Formal Verification of Behavioural Transformations during Embedded System Design"**, submitted by **Chandan Karfa** to Indian Institute of Technology, Kharagpur, is a record of bona fide research work under our supervision and we consider it worthy of consideration for the award of the degree of Doctor of Philosophy of the Institute.

Chittaranjan Mandal Professor CSE, IIT Kharagpur Dipankar Sarkar Professor CSE, IIT Kharagpur

Date:

### DECLARATION

#### I certify that

- (a) The work contained in the thesis is original and has been done by myself under the general supervision of my supervisors.

- (b) The work has not been submitted to any other Institute for any degree or diploma.

- (c) I have followed the guidelines provided by the Institute in writing the thesis.

- (d) I have conformed to the norms and guidelines given in the Ethical Code of Conduct of the Institute.

- (e) Whenever I have used materials (data, theoretical analysis, and text) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references.

- (f) Whenever I have quoted written materials from other sources, I have put them under quotation marks and given due credit to the sources by citing them and giving required details in the references.

Chandan Karfa

### ACKNOWLEDGMENTS

I would like to express my profound sense of gratitude to my thesis supervisors Prof. Chittaranjan Mandal and Prof. Dipankar Sarkar for guiding me through the PhD program. I acknowledge their constant technical and moral support and guidance throughout my PhD. I have learned a lot about the art of conducting research and solving problems from my supervisors. I consider myself extremely lucky for getting the opportunity to work under them.

I acknowledge the support from Microsoft Research India for partially funding my research work and providing generous travel grants and stipend through the Microsoft Research India PhD Fellowship Award.

I want to thank my labmates Arnab da, Aritra, Priyankar da, Srobona, MSD, Kunal, Partha, Antara, Debjit, Sudip, Subho, Gautam, Debi da and others for making the lab most enjoyable place in Kgp. I want to thank Debjit for all his system and latex related supports. Special thanks to Kunal and Partha for helping me in some experiments of my work. My stay in Kgp was extremely pleasurable thanks to my friends Somnath, Soumyajit, Soumyadip, Bodhi, Pradipta da, Gopal da, Vivek, Sumit, Sayan, Soubhik, Rajarshi and many others. I spent a lot of good time in TATA sports complex with VSRC football and cricket teams.

I acknowledge google.com for helping me in searching most of the documents during my research. Special thanks to cricinfo.com which is the source of my another (re)search on cricket during my stay in Kgp.

Last but most important are my wife Aparna, my parents and the other members of my family. Without their constant encouragements, supports, love and well wishes, this thesis never be materialized.

Chandan Karfa

### ABSTRACT

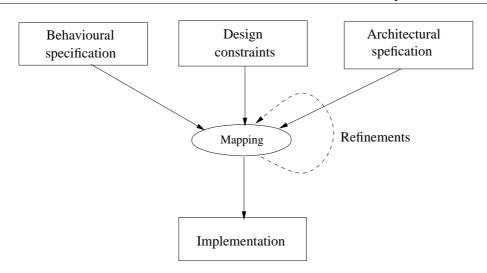

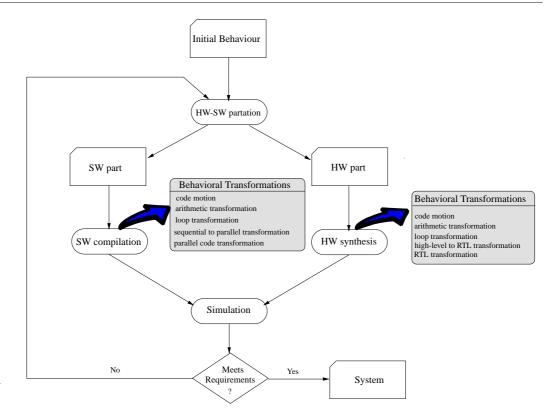

Application of behavioural transformations for obtaining optimal performance, energy and/or area on a given platform during embedded system design is now a common practice. Verifying correctness of these transformations is an important step in ensuring dependability of embedded systems. This thesis addresses verification methodologies, primarily by way of equivalence checking, for six behavioural transformations that are applied during embedded system design. The transformations considered cover code motion, generation of register transfer level (RTL) design after carrying high-level optimizations and also RTL transformations, loop and arithmetic transformations on array based programs, transformations on array based programs leading to the generations of Kahn process networks (KPN) to achieve high degree of parallelism and also transformations applied at the KPN level.

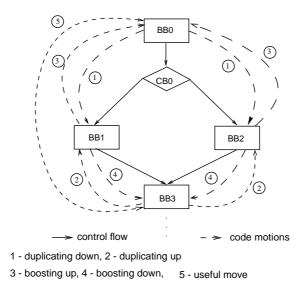

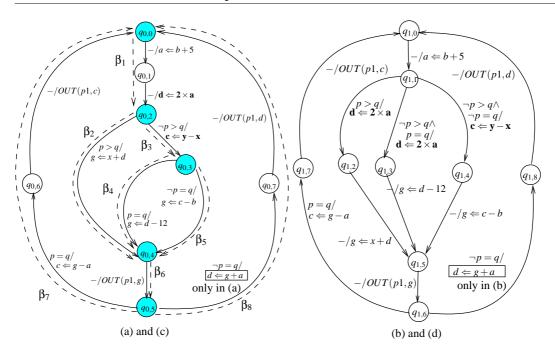

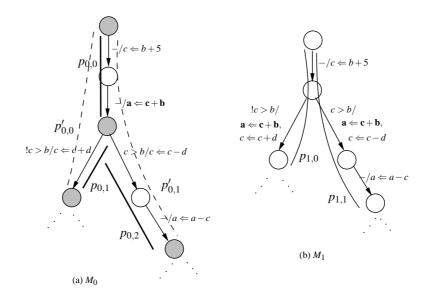

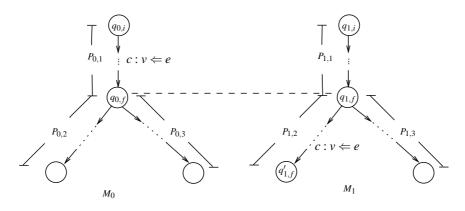

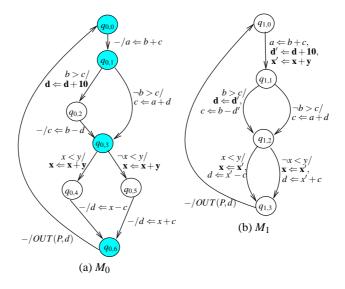

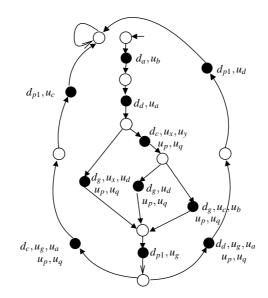

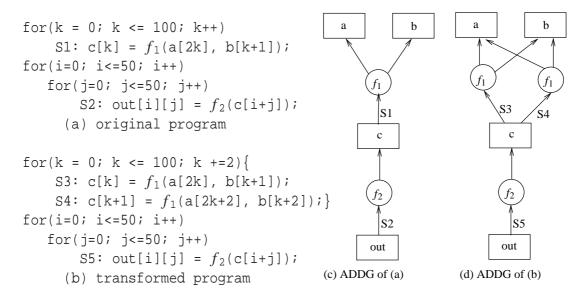

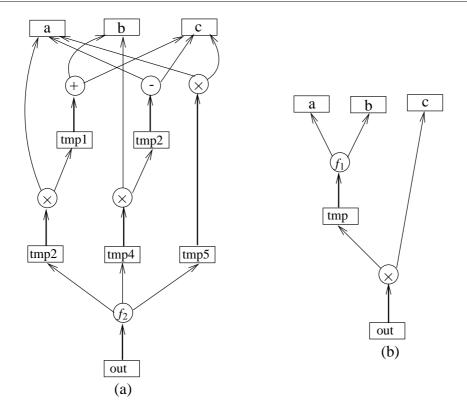

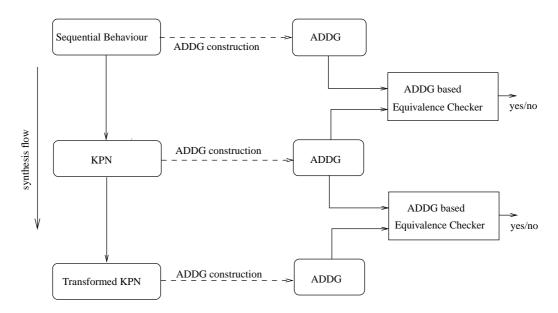

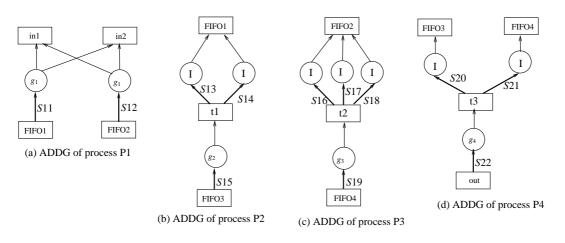

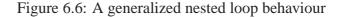

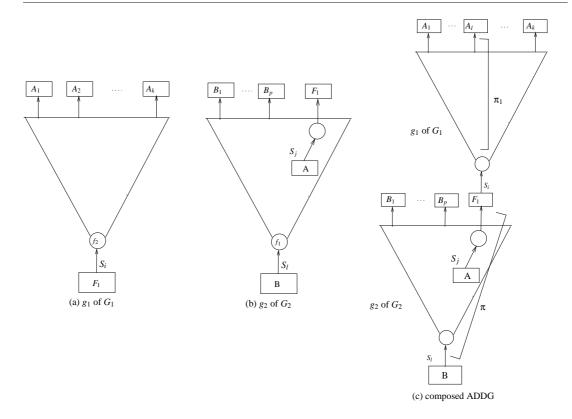

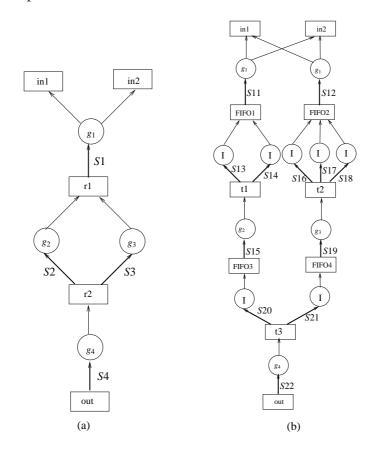

Verification methods for the first three transformations on programs not involving arrays employ the model of finite state machines with datapaths (FSMD). FSMDs are generalizations of FSMs to capture data transformations taking place between control states. FSMD based equivalence checking method consists in introducing cutpoints in one FSMD, visualizing its computations as concatenation of paths from cutpoints to cutpoints and finally, identifying equivalent finite path segments in the other FSMD; the process is then repeated with the FSMDs interchanged. Verification methods for the last three transformations involving arrays employ the array data dependence graphs (ADDG). The ADDG model primarily captures computation of a range of elements of an array from ranges of elements of other arrays. ADDG based equivalence checking attempts to show that the overall computations depicted in the ADDG to define the final ADDG nodes in terms of the initial ADDG nodes are equivalent, both in terms of computation and range of array elements, with respect to those in the ADDG being compared.

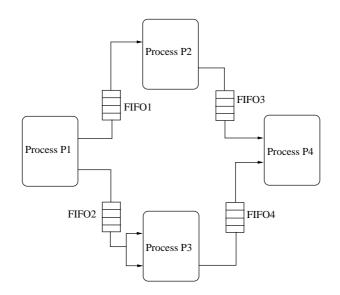

The FSMD based methods developed handle both uniform and non-uniform code motion transformations. For non-uniform code motions model checking of some data-flow properties is also carried out. A rewriting mechanism covering both pipelining and multicycling is used to construct an FSMD from register transfer operations for RTL related equivalence checking. In our ADDG equivalence checking method we have introduced the notion of slices to guide the checking along the sequences in which operations are used to define array elements in the original behaviour. Normalized representation of arithmetic ransformations for both FSMD and ADDG based equivalence checking. Our ADDG based checking has been extended to check the equivalence of KPN networks derived by parallelizing sequential array based programs. Potential deadlocks in the KPN are also detected through the ADDG based modelling.

Correctness and complexity of the all the developed methods have been treated formally. The methods have been implemented and tested on several benchmarks. This work represents useful application of equivalence checking as a verification method for verification to several aspects of the embedded system design flow.

**Keywords:** Embedded System, Formal Verification, Equivalence Checking, Behavioural Transformation, Code Motion, Loop Transformation, Register Transfer Level (RTL), Kahn Process Network, Finite State Machine with Datapath (FSMD), Array Data Dependence Graph (ADDG).

## Contents

| Al | bstrac            | et            |                                                             | xiii |

|----|-------------------|---------------|-------------------------------------------------------------|------|

| Ta | Table of Contents |               |                                                             |      |

| Li | st of S           | Symbols       | S                                                           | xix  |

| Li | st of l           | Figures       |                                                             | xxi  |

| Li | st of [           | <b>Fables</b> |                                                             | XXV  |

| 1  | Intr              | oductio       | n                                                           | 1    |

|    | 1.1               | Embeo         | dded system design flow                                     | 1    |

|    | 1.2               |               | ioural transformations                                      | 4    |

|    |                   | 1.2.1         | Code motion transformations                                 | 4    |

|    |                   | 1.2.2         | Loop transformations                                        | 5    |

|    |                   | 1.2.3         | Arithmetic transformations                                  | 6    |

|    |                   | 1.2.4         | High-level to RTL transformations                           | 6    |

|    |                   | 1.2.5         | Sequential to parallel transformations                      | 7    |

|    | 1.3               | Motiva        | ations and objectives                                       | 8    |

|    |                   | 1.3.1         | Problem statements                                          | 10   |

|    | 1.4               | Contri        | butions                                                     | 13   |

|    | 1.5               | Organi        | ization of the thesis                                       | 15   |

| 2  | Lite              | rature S      | Survey                                                      | 17   |

|    | 2.1               | Code 1        | motion transformations                                      | 17   |

|    |                   | 2.1.1         | Applications of code motion transformations                 | 17   |

|    |                   | 2.1.2         | Verification of code motion transformations                 | 20   |

|    | 2.2               | High-l        | evel to RTL and RTL transformations                         | 22   |

|    |                   | 2.2.1         | Applications of High-level to RTL and RTL transformations . | 22   |

|    |                   | 2.2.2         | Verification of High-level to RTL and RTL transformations   | 23   |

|   | 2.3  | Loop transformations and arithmetic transformations                | 25 |

|---|------|--------------------------------------------------------------------|----|

|   |      | 2.3.1 Applications of loop transformations                         | 25 |

|   |      | 2.3.2 Applications of arithmetic transformations                   | 27 |

|   |      | 2.3.3 Verification of loop and arithmetic transformations          | 29 |

|   | 2.4  | Parallelizing transformations                                      | 31 |

|   |      | 2.4.1 Applications of parallelizing transformations                | 31 |

|   |      |                                                                    | 34 |

|   | 2.5  | · ·                                                                | 35 |

| 3 | Veri | fication of Code Motion Transformations                            | 37 |

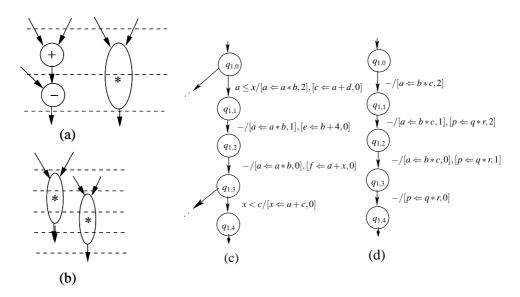

|   | 3.1  | Introduction                                                       | 37 |

|   | 3.2  | Basic equivalence checking method                                  | 38 |

|   |      | 3.2.1 FSMDs and its paths                                          | 38 |

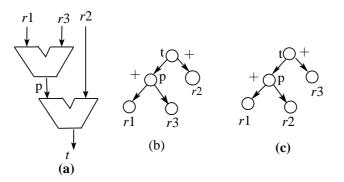

|   |      | 3.2.2 Normalization of arithmetic expressions                      | 42 |

|   | 3.3  | Equivalence problem formulation                                    | 44 |

|   |      | 3.3.1 Path cover and equivalence of FSMDs                          | 45 |

|   |      | 3.3.2 A method to handle uniform code motions                      | 46 |

|   | 3.4  | Verification of non-uniform code motions                           | 48 |

|   |      | 3.4.1 An example of non-uniform code motion                        | 48 |

|   |      | 3.4.2 A scheme for verifying non-uniform code motions              | 49 |

|   |      | 3.4.3 Strong and weak equivalence of paths                         | 53 |

|   |      |                                                                    | 56 |

|   |      | 3.4.5 Encoding and model checking the data-flow properties         | 57 |

|   |      | 3.4.6 The equivalence checking method                              | 58 |

|   |      | 3.4.7 Illustration of working of the equivalence checking method   | 64 |

|   |      | 3.4.8 Justification of the initial cutpoints                       | 66 |

|   | 3.5  |                                                                    | 68 |

|   | 3.6  | Correctness and complexity                                         | 70 |

|   |      |                                                                    | 70 |

|   |      | 3.6.2 Complexity                                                   | 74 |

|   | 3.7  |                                                                    | 75 |

|   |      | 3.7.1 Limitations of the method                                    | 81 |

|   | 3.8  | Conclusion                                                         | 82 |

|   |      |                                                                    |    |

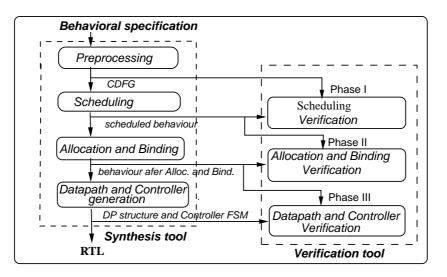

| 4 | Veri | fication of RTL Generation Phase                                   | 83 |

|   | 4.1  | Introduction                                                       | 83 |

|   | 4.2  | Verification challenges                                            | 86 |

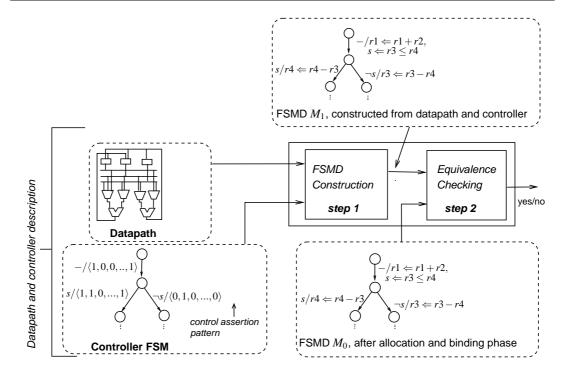

|   | 4.3  | Construction of FSMDs from RTL designs                             | 87 |

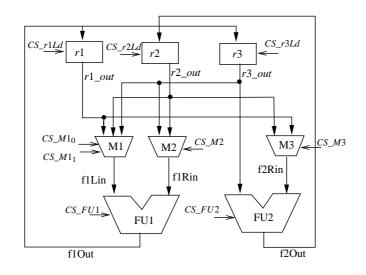

|   |      | 4.3.1 Representation of the datapath description                   | 87 |

|   |      | 4.3.2 A Method of obtaining the micro-operations for a control as- |    |

|   |      | sertion pattern                                                    | 89 |

|   |      | 4.3.3 Identification of RT operations realized by a set of micro-  |    |

|   |      | operations                                                         | 91 |

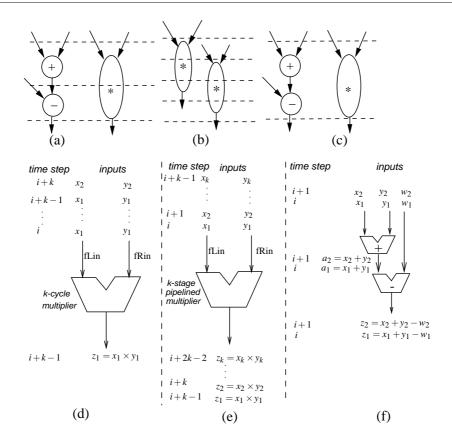

|   |      | 4.3.4 Multicycle, pipelined and chained operations                 | 93 |

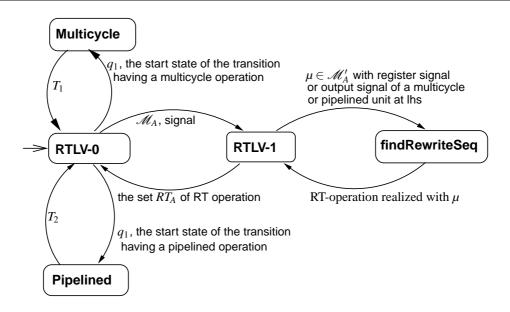

|   | 4.4  | The Overall construction framework of FSMD                         | 95 |

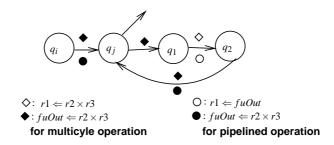

|   |      | 4.4.1 Handling of multicycle operations                            | 96 |

|   |      |                                                                    |    |

| <ul> <li>4.4.4 Verification during construction of FSMD</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 4.4.2 Handling of pipelined operations                                                                                        | 99 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>4.4.4 Verification during construction of FSMD</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | 4.4.3 Handling chained operations                                                                                             | 01 |

| <ul> <li>4.5 Correctness and complexity of the algorithm</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                                                                                                               |    |

| <ul> <li>4.5.2 Correctness and complexity of the module <i>RTLV-1</i></li> <li>4.5.3 Correctness and complexity of the module <i>Multicycle</i> and <i>Pipelined</i></li> <li>4.5.4 Correctness and complexity of the module <i>RTLV-0</i></li> <li>4.6 Verification by equivalence checking</li> <li>4.7 Verification of low power RTL transformations</li> <li>4.7.1 Alternative datapath architecture</li> <li>4.7.2 Restructuring of multiplexer networks to enhance data correlation</li> <li>4.7.3 Restructuring of multiplexer networks to eliminate glitchy con trol signals</li> <li>4.7.4 Clocking of control signals</li> <li>4.7.5 Glitch reduction using delays</li> <li>4.8 Experimental results</li> <li>4.9 Conclusion</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> </ul>                                         |   | 4.5  | Correctness and complexity of the algorithm                                                                                   |    |

| <ul> <li>4.5.3 Correctness and complexity of the modules <i>Multicycle</i> and <i>Pipelined</i></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      | 4.5.1 Correctness and complexity of the module <i>findRewriteSeq</i> 10                                                       | 03 |

| <ul> <li>4.5.3 Correctness and complexity of the modules <i>Multicycle</i> and <i>Pipelined</i></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |      |                                                                                                                               |    |

| Pipelined         4.5.4       Correctness and complexity of the module <i>RTLV-0</i> 4.6       Verification of low power RTL transformations         4.7       Verification of low power RTL transformations         4.7.1       Alternative datapath architecture         4.7.2       Restructuring of multiplexer networks to enhance data correlation         4.7.3       Restructuring of multiplexer networks to enhance data correlation         4.7.4       Clocking of control signals         4.7.5       Glitch reduction using delays         4.8       Experimental results         4.9       Conclusion         5       Verification of Loop Transformations         5.1       Introduction         5.2       Array data dependence graphs         5.2.1       Representation of data dependencies of the behaviour         5.2.3       Recurrence in ADDG         5.2.4       Construction of the ADDG from a sequential behaviour         5.3       Slices         5.4       Equivalence of ADDGs         5.4.1       Normalization of the characteristic formula of a slice         5.4.2       Some simplification rules for data transformations         5.5       A case study         5.6       Correctness and complexity         5.7                                                                                                                                |   |      | 1 7                                                                                                                           |    |

| <ul> <li>4.5.4 Correctness and complexity of the module <i>RTLV-0</i></li> <li>4.6 Verification by equivalence checking</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      | $Pipelined \dots \dots$ | 12 |

| <ul> <li>4.6 Verification by equivalence checking</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      | 1                                                                                                                             |    |

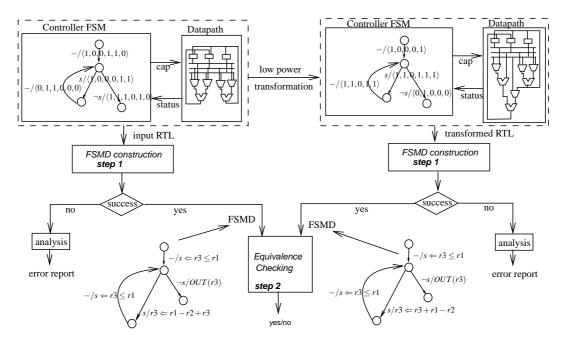

| <ul> <li>4.7 Verification of low power RTL transformations <ul> <li>4.7.1 Alternative datapath architecture</li> <li>4.7.2 Restructuring of multiplexer networks to enhance data correlation</li> <li>4.7.3 Restructuring of multiplexer networks to eliminate glitchy control signals</li> <li>4.7.4 Clocking of control signals</li> <li>4.7.5 Glitch reduction using delays</li> </ul> </li> <li>4.8 Experimental results <ul> <li>4.9 Conclusion</li> </ul> </li> <li>5 Verification of Loop Transformations</li> <li>5.1 Introduction</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> </ul> <li>6 Verification of Parallelizing Transformations <ul> <li>6.1 Introduction</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul> </li> |   | 4.6  | 1 0                                                                                                                           |    |

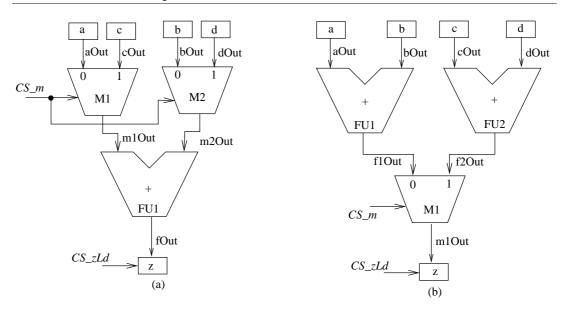

| <ul> <li>4.7.1 Alternative datapath architecture</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 4.7  |                                                                                                                               |    |

| <ul> <li>4.7.2 Restructuring of multiplexer networks to enhance data correlation</li> <li>4.7.3 Restructuring of multiplexer networks to eliminate glitchy control signals</li> <li>4.7.4 Clocking of control signals</li> <li>4.7.5 Glitch reduction using delays</li> <li>4.7.5 Glitch reduction using delays</li> <li>4.8 Experimental results</li> <li>4.9 Conclusion</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                           |   |      | 1                                                                                                                             |    |

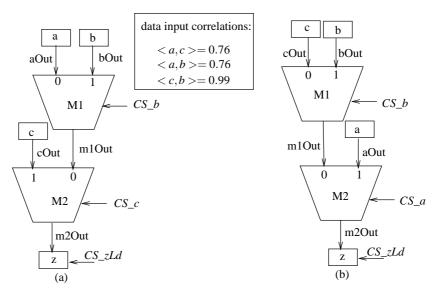

| lation       4.7.3         Restructuring of multiplexer networks to eliminate glitchy control signals         4.7.4       Clocking of control signals         4.7.5       Glitch reduction using delays         4.8       Experimental results         4.9       Conclusion         5.1       Introduction         5.2       Array data dependence graphs         5.2.1       Representation of data dependencies of the behaviour         5.2.2       Transitive dependence         5.2.3       Recurrence in ADDG         5.2.4       Construction of the ADDG from a sequential behaviour         5.3       Slices         5.4       Equivalence of ADDGs         5.4.1       Normalization of the characteristic formula of a slice         5.4.2       Some simplification rules for data transformations         5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2                                                                                                                                                                                                      |   |      |                                                                                                                               |    |

| <ul> <li>4.7.3 Restructuring of multiplexer networks to eliminate glitchy control signals</li> <li>4.7.4 Clocking of control signals</li> <li>4.7.5 Glitch reduction using delays</li> <li>4.8 Experimental results</li> <li>4.9 Conclusion</li> <li>5 Verification of Loop Transformations</li> <li>5.1 Introduction</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4 correctness and complexity</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                 |   |      | lation                                                                                                                        | 21 |

| trol signals       4.7.4       Clocking of control signals         4.7.5       Glitch reduction using delays       4.8         4.8       Experimental results       4.9         4.9       Conclusion       5         5       Verification of Loop Transformations       5.1         5.1       Introduction       5.2         6.1       Representation of data dependence graphs       5.2.1         7.2.1       Representation of data dependencies of the behaviour       5.2.2         7.2.3       Recurrence in ADDG       5.2.3         7.4       Construction of the ADDG from a sequential behaviour       5.3         7.3       Slices       5.4         7.4.1       Normalization of the characteristic formula of a slice       5.4.2         7.4.3       Equivalence of ADDGs       5.4.3         7.4.4       Some simplification rules for data transformations       5.4.3         7.5.4       Equivalence problem formulation       5.5         7.5.4       Equivalence problem formulation       5.5         7.5.5       A case study       5.6         7.6       Correctness and complexity       5.6         7.6       Error diagnosis       5.5         7.7       Error diagnosis                                                                                                                                                                                        |   |      |                                                                                                                               |    |

| <ul> <li>4.7.5 Glitch reduction using delays</li> <li>4.8 Experimental results</li> <li>4.9 Conclusion</li> <li>5 Verification of Loop Transformations</li> <li>5.1 Introduction</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4 A case study</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |   |      | trol signals                                                                                                                  | 22 |

| <ul> <li>4.7.5 Glitch reduction using delays</li> <li>4.8 Experimental results</li> <li>4.9 Conclusion</li> <li>5 Verification of Loop Transformations</li> <li>5.1 Introduction</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4 A case study</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                    |   |      | 4.7.4 Clocking of control signals                                                                                             | 23 |

| <ul> <li>4.8 Experimental results</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |      |                                                                                                                               |    |

| <ul> <li>4.9 Conclusion</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 4.8  | Experimental results                                                                                                          |    |

| <ul> <li>5 Verification of Loop Transformations</li> <li>5.1 Introduction</li> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | 4.9  | Conclusion                                                                                                                    |    |

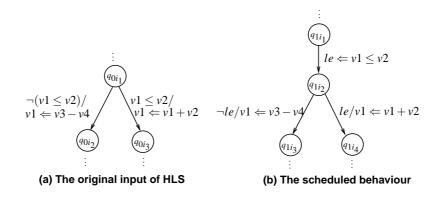

| <ul> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |                                                                                                                               |    |

| <ul> <li>5.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 | Veri | ication of Loop Transformations                                                                                               | 33 |

| <ul> <li>5.2 Array data dependence graphs</li> <li>5.2.1 Representation of data dependencies of the behaviour</li> <li>5.2.2 Transitive dependence</li> <li>5.2.3 Recurrence in ADDG</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.6.1 Complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ľ |      | -                                                                                                                             |    |

| 5.2.1       Representation of data dependencies of the behaviour         5.2.2       Transitive dependence         5.2.3       Recurrence in ADDG         5.2.4       Construction of the ADDG from a sequential behaviour         5.3       Slices         5.4       Equivalence of ADDGs         5.4.1       Normalization of the characteristic formula of a slice         5.4.2       Some simplification rules for data transformations         5.4.3       Equivalence problem formulation         5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      |                                                                                                                               |    |

| 5.2.2       Transitive dependence         5.2.3       Recurrence in ADDG         5.2.4       Construction of the ADDG from a sequential behaviour         5.3       Slices         5.4       Equivalence of ADDGs         5.4.1       Normalization of the characteristic formula of a slice         5.4.2       Some simplification rules for data transformations         5.4.3       Equivalence problem formulation         5.4.3       Equivalence problem formulation         5.4.3       Equivalence problem formulation         5.4.3       Equivalence problem formulation         5.4.5       A case study         5.6       Correctness and complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |                                                                                                                               |    |

| <ul> <li>5.2.3 Recurrence in ADDG.</li> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |      |                                                                                                                               |    |

| <ul> <li>5.2.4 Construction of the ADDG from a sequential behaviour</li> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |      |                                                                                                                               |    |

| <ul> <li>5.3 Slices</li> <li>5.4 Equivalence of ADDGs</li> <li>5.4.1 Normalization of the characteristic formula of a slice</li> <li>5.4.2 Some simplification rules for data transformations</li> <li>5.4.3 Equivalence problem formulation</li> <li>5.5 A case study</li> <li>5.6 Correctness and complexity</li> <li>5.6 Correctness and complexity</li> <li>5.6 Correctness and complexity</li> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |      |                                                                                                                               |    |

| 5.4.1       Normalization of the characteristic formula of a slice         5.4.2       Some simplification rules for data transformations         5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.3  | Slices                                                                                                                        |    |

| 5.4.2       Some simplification rules for data transformations         5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 5.4  | Equivalence of ADDGs                                                                                                          | 54 |

| 5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6       Verification of Parallelizing Transformations         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.4.1 Normalization of the characteristic formula of a slice 1                                                                | 56 |

| 5.4.3       Equivalence problem formulation         5.5       A case study         5.6       Correctness and complexity         5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6       Verification of Parallelizing Transformations         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |      | 5.4.2 Some simplification rules for data transformations 1                                                                    | 58 |

| <ul> <li>5.5 A case study</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      | -                                                                                                                             | 61 |

| 5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6       Verification of Parallelizing Transformations         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 5.5  | A case study                                                                                                                  | 65 |

| 5.6.1       Complexity         5.7       Error diagnosis         5.8       Experimental results         5.9       Conclusion         6       Verification of Parallelizing Transformations         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 5.6  | Correctness and complexity                                                                                                    | 67 |

| <ul> <li>5.7 Error diagnosis</li> <li>5.8 Experimental results</li> <li>5.9 Conclusion</li> <li>6 Verification of Parallelizing Transformations</li> <li>6.1 Introduction</li> <li>6.2 Verification framework</li> <li>6.2.1 Kahn process networks</li> <li>6.2.2 Verification approach</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |      | 5.6.1 Complexity                                                                                                              | 68 |

| <ul> <li>5.8 Experimental results</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   | 5.7  | Error diagnosis                                                                                                               | 71 |

| 6       Verification of Parallelizing Transformations         6.1       Introduction         6.2       Verification framework         6.2.1       Kahn process networks         6.2.2       Verification approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.8  | Experimental results                                                                                                          |    |

| <ul> <li>6.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 5.9  | Conclusion                                                                                                                    | 74 |

| <ul> <li>6.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |      |                                                                                                                               |    |

| <ul> <li>6.1 Introduction</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6 | Veri | ication of Parallelizing Transformations 1'                                                                                   | 75 |

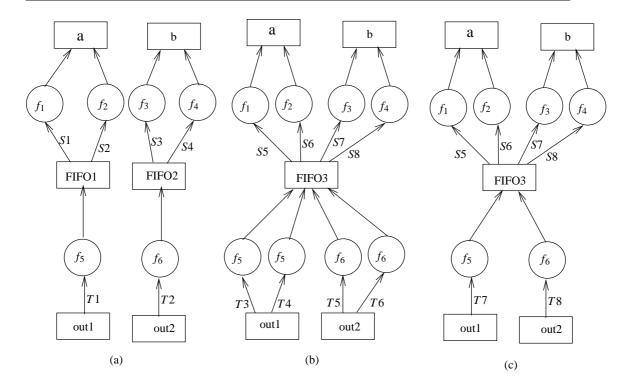

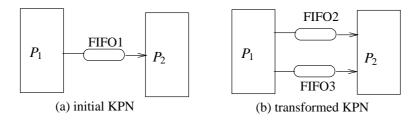

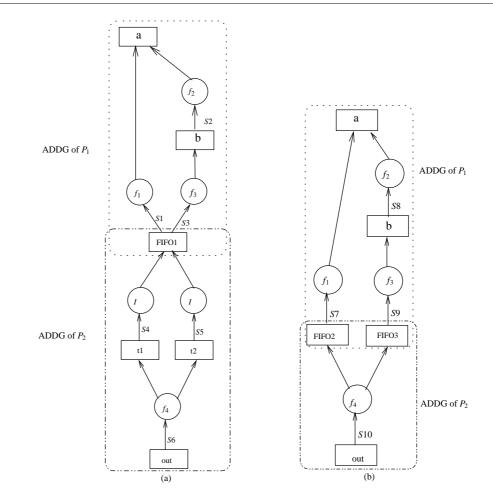

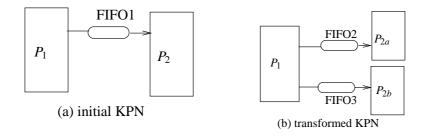

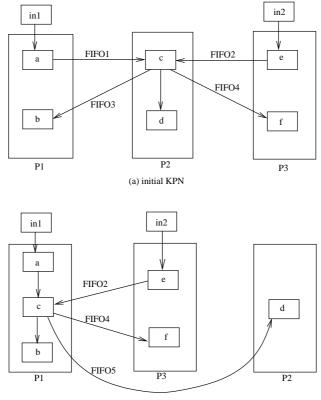

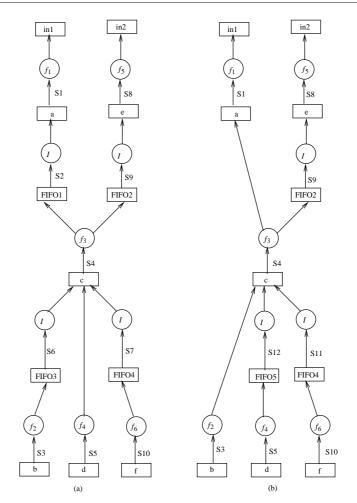

| <ul> <li>6.2 Verification framework</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |      |                                                                                                                               | 75 |