## Hand-in-hand Verification and Synthesis of Digital Circuits

THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

**Master of Science (by Research)**

in

**Computer Science and Engineering**

Ву

**Chandan Karfa**

under the guidance of

Chittaranjan Mandal Dipankar Sarkar

Department of Computer Science and Engineering

Indian Institute of Technology

Kharagpur

March 2007

Dedicated to my parents

## Certificate

This is to certify that the thesis titled "Hand-in-hand Verification and Synthesis of Digital Circuits" submitted by Chandan Karfa, to the Department of Computer Science and Engineering, Indian Institute of Technology, Kharagpur, India, for the partial fulfilled for award of the degree of Master of Science (by Research), is a bonafide record of original research work carried out by him under our supervision and guidance. The thesis fulfills all the requirements as per the regulations of this Institute and, in our opinion, has reached the standard needed for submission. Neither this thesis nor any part of it has been submitted for any degree elsewhere.

| Place: I.I.T. Kharagpur | (Chittaranjan Mandal)              |

|-------------------------|------------------------------------|

|                         | Associate Professor                |

| Date:                   | Dept. of Computer Science and Engg |

|                         | Indian Institute of Technology     |

|                         | Kharagpur 721302, INDIA.           |

|                         |                                    |

|                         |                                    |

(Dipankar Sarkar)

Dept. of Computer Science and Engg

Indian Institute of Technology

Kharagpur 721302, INDIA.

**Professor**

Place: I.I.T. Kharagpur

Date:

## Acknowledgment

This thesis is the result of my research work under the guidance of Prof. C. R. Mandal and Prof. D. Sarkar at the Department of Computer Science and Engineering of the Indian Institute of Technology, Kharagpur. I am deeply grateful to my research advisors for the huge amount of time and effort they spent guiding me through several difficulties on the way. Without the help, encouragement and patient support I received from my guides, this thesis would never have materialized. I am considered myself extremely lucky for getting the opportunity to work under them. During my long association with them and the other professors in IIT, Kharagpur, I am sure, I have learned a lot. I am also thankful to Dr. Chris Reade, Head of School of Business Information Management, Kingston Business School for providing me some useful suggestions and support. I want to thank Prof. A. Patra, Professor-in-charge, Advanced VLSI Design Laboratory, IIT Kharagpur for allowing me to use the lab resource for my experimentations. I will never forget the support, suggestion and ideas provided by Santosh Biswas through out my research work. I am grateful to Murali, Satyam, Srinivas and Ajay for their full sopport in the development of SAST. My special thanks goes to Sumit and Tirthankar for help me in preparing the GUI of SAST. It was a great fun and source of ideas and energy to have friends like Somnath, Bodhisatwa, Harsha, Sayak, Gopal, Soham, Soumyajit, Sunandan, Pratyush, Barun, Plaban, Anupam and others in my department. I am thankful to our cook Das da for serving me food through out my stay in IIT Kgp. Last but most important are my parents and the other members of my family. Without their constant encouragements, supports and well wishes, this thesis never be materialized.

#### Chandan Karfa

Department of Computer Science and Engineering

Indian Institute of Technology, Kharagpur

March 2007

## **Abstract**

Advances in VLSI technology have enabled its deployment into complex circuits. Synthesis flow of such circuits comprises various phases where each phase performs the task algorithmically providing for ingenious interventions of experts. The gap between the original behaviour and the finally synthesized circuit is too wide to be analyzed by any reasoning mechanism. The validation tasks, therefore, must be planned to go hand-in-hand with each phase of synthesis with scope to handle the specialties of each synthesis sub-task separately. This thesis is concerned with hand-in-hand verification and (high-level) synthesis of digital circuits. The verification of high-level synthesis is performed in three-phases namely, scheduling verification, allocation and binding verification and data-path and controller verification. The input and output of each phase are represented as finite state machines with data-paths (FSMD); the equivalence of two FSMDs is defined and has been proved. The difficulties of each phase are identified and the verification methods based on equivalence of two FSMDs have been formulated accordingly. The scheduling verification method is strong enough to accommodate merging of path segments in the original behaviour, application of several code motion techniques and some arithmetic transformations employed during scheduling. The allocation and binding verification method is capable of handling register sharing verification. For verification of the data-path and controller synthesis phase, a rewriting method is proposed. The method reveals, from a flat set of control signal assertions, the spatial sequences of data flow over the data-path, each sequence realizing a member of a concurrent set of register transfer operations. A high-level synthesis tool, called *structured architecture* synthesis tool (SAST), has been developed which support hand-in-hand synthesis and verification. The synthesis flow of SAST and the results for several high-level synthesis benchmarks are provided. The thesis concludes by identifying some directions for future research.

**Key Words:** High-level Synthesis, Formal Verification, Equivalence Checking, Normalization, FSMD models, Path-Based Scheduling, Code Motion Techniques, Allocation and Binding, Register Sharing, Data-Path and Controller Generation, Rewriting Method, SAST.

## **Contents**

| 1 | Intr | roduction, Background and Motivat                  | ion                  | 1    |

|---|------|----------------------------------------------------|----------------------|------|

|   | 1.1  | General Introduction                               |                      | . 1  |

|   |      | 1.1.1 High-level Synthesis                         |                      | . 3  |

|   |      | 1.1.2 Formal Verification                          |                      | . 5  |

|   | 1.2  | Literature Survey on High-level Syr                | nthesis Verification | . 6  |

|   |      | 1.2.1 Pre-synthesis Verification .                 |                      | . 7  |

|   |      | 1.2.2 Formal Synthesis Verification                | on                   | . 7  |

|   |      | 1.2.3 Post-synthesis Verification                  |                      | . 8  |

|   | 1.3  | Motivation and Objectives of the Pr                | esent Work           | . 13 |

|   | 1.4  | Contributions of the Present Work                  |                      | . 15 |

|   | 1.5  | Organization of the Thesis                         |                      | . 17 |

| 2 | The  | e Equivalence Problem Formulation                  |                      | 19   |

|   | 2.1  | Introduction                                       |                      | . 19 |

|   | 2.2  | Finite State Machines with Data-pa                 | nths                 | . 19 |

|   |      | 2.2.1 Paths and Transformations                    | along a Path         | . 23 |

|   |      | 2.2.2 Computation of $R_{\alpha}$ and $r_{\alpha}$ |                      | . 25 |

|   |      | 2.2.3 Characterization of Paths .                  |                      | . 25 |

|   |      | 2.2.4 Computations and Path Cov                    | vers of an FSMD      | . 25 |

|   | 2.3  | Equivalence of FSMDs                               |                      | . 26 |

|   |      | 2.3.1 The Basic Equivalence Che                    | cking Method         | . 28 |

|   |      | 2.3.2 Normalization of Arithmeti                   | c Expressions        | . 30 |

|   | 2.4  | Conclusions                                        |                      | . 33 |

| 3 | Sche | eduling Verification                               |                      | 35   |

8 CONTENTS

|   | 3.1  | Introdu  | uction                                                        | . 33 |

|---|------|----------|---------------------------------------------------------------|------|

|   | 3.2  | Object   | tive of Scheduling Verification                               | . 37 |

|   | 3.3  | Verific  | cation Issues                                                 | . 37 |

|   | 3.4  | The So   | cheduling Verification Algorithm                              | 42   |

|   |      | 3.4.1    | The Algorithm                                                 | 42   |

|   |      | 3.4.2    | Correctness of the algorithm                                  | 43   |

|   |      | 3.4.3    | Complexity of the algorithm                                   | 44   |

|   | 3.5  | Verific  | eation of Different Scheduling Algorithms                     | 45   |

|   |      | 3.5.1    | Basic Block Based Scheduling                                  | 45   |

|   |      | 3.5.2    | Path Based Scheduling                                         | 46   |

|   | 3.6  | Perform  | mance on Several HLS Transformations                          | 48   |

|   |      | 3.6.1    | Renaming                                                      | 48   |

|   |      | 3.6.2    | Common Sub-Expression Elimination                             | 49   |

|   |      | 3.6.3    | Code Transformation to Increase Conditional Reuse of Hardware | 51   |

|   |      | 3.6.4    | Reverse Speculation                                           | 52   |

|   |      | 3.6.5    | Early Condition Execution                                     | . 55 |

|   |      | 3.6.6    | Conditional Speculation                                       | 56   |

|   |      | 3.6.7    | Conditional Branch Balancing                                  | 57   |

|   |      | 3.6.8    | Speculation                                                   | . 57 |

|   |      | 3.6.9    | Loop Shifting and Compaction                                  | . 59 |

|   | 3.7  | Conclu   | usions                                                        | 61   |

| 4 | Allo | cation a | and Binding Verification                                      | 63   |

|   | 4.1  |          | uction                                                        | 63   |

|   | 4.2  |          | tives                                                         |      |

|   | 4.3  | _        | eation of Allocation and Binding of Functional Units          |      |

|   | 4.4  |          | er Sharing Verification                                       |      |

|   |      | 4.4.1    | The Mapping Functions                                         | 66   |

|   |      | 4.4.2    | Verification Issues                                           |      |

|   |      | 4.4.3    | Verification Algorithm                                        |      |

|   |      | 4.4.4    | An Example                                                    |      |

|   |      | 4.4.5    | Performance of the Algorithm                                  |      |

|   |      |          |                                                               |      |

CONTENTS 9

|   | 4.5  | Conclusions                                                          | . 73  |

|---|------|----------------------------------------------------------------------|-------|

| 5 | Data | a-path and Controller Verification                                   | 75    |

|   | 5.1  | Introduction                                                         | . 75  |

|   | 5.2  | Verification Goal                                                    | . 78  |

|   | 5.3  | Construction of the FSMD $M_3$                                       | . 78  |

|   |      | 5.3.1 Construction of the FSMD $M_3$ : An Example                    | . 82  |

|   |      | 5.3.2 A Rewriting Method                                             | . 84  |

|   |      | 5.3.3 Correctness and Complexity of Algorithm 2                      | . 86  |

|   | 5.4  | Verification During Construction of FSMD $M_3$                       | . 89  |

|   |      | 5.4.1 Redundancy Optimization in the Data-path and in the Controller | . 90  |

|   | 5.5  | Verification by Equivalence Checking                                 | . 91  |

|   | 5.6  | Conclusions                                                          | . 91  |

| 6 | Deve | elopment of a High-level Synthesis Tool (SAST)                       | 95    |

|   | 6.1  | Introduction                                                         | . 95  |

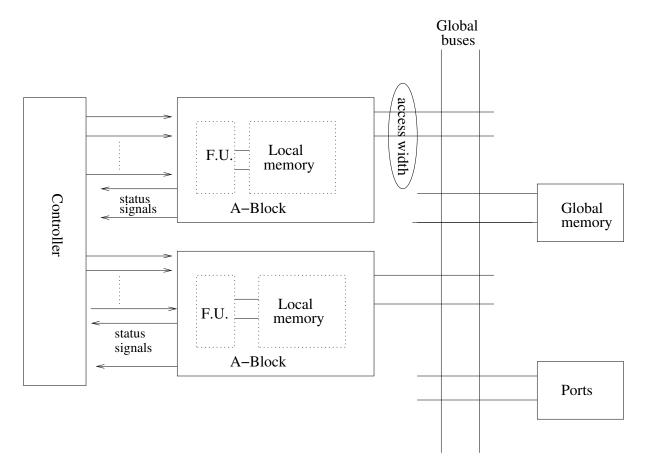

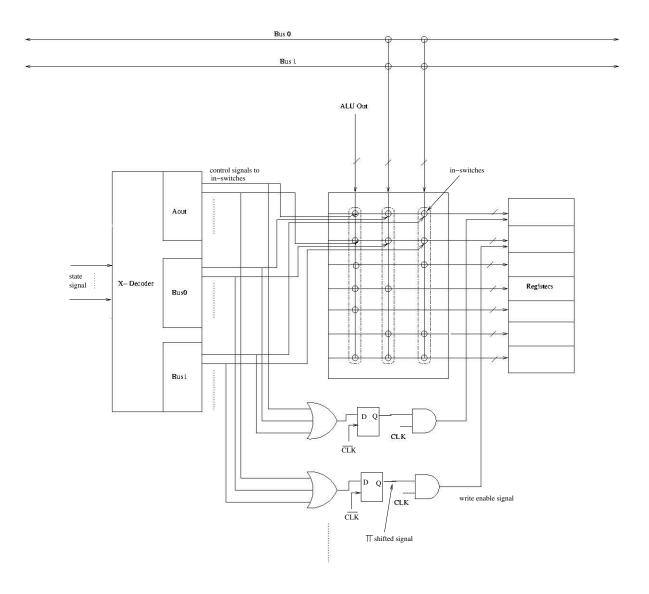

|   | 6.2  | Target Architecture                                                  | . 95  |

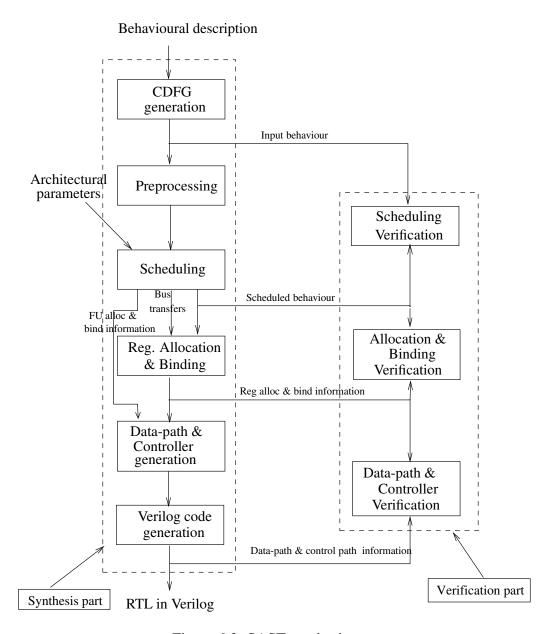

|   | 6.3  | SAST Synthesis Steps                                                 | . 98  |

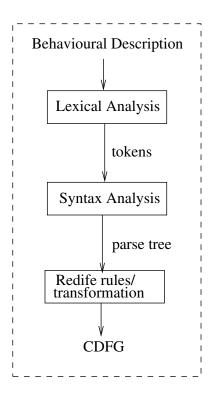

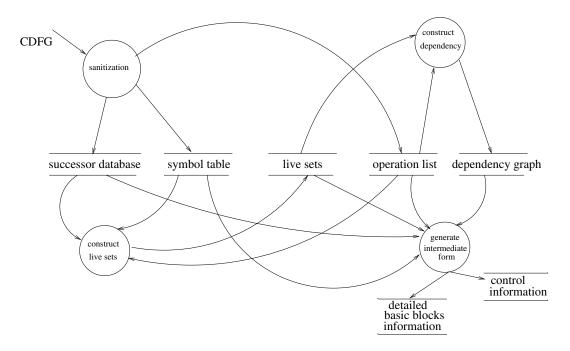

|   |      | 6.3.1 CDFG Generation                                                | . 99  |

|   |      | 6.3.2 Preprocessing                                                  | . 102 |

|   |      | 6.3.3 Scheduling                                                     | . 106 |

|   |      | 6.3.4 Register Allocation and Binding                                | . 114 |

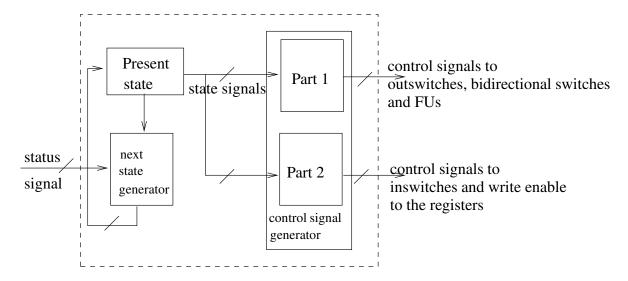

|   |      | 6.3.5 Data-path and Controller Generation                            | . 118 |

|   |      | 6.3.6 Verilog Code Generation                                        | . 121 |

|   | 6.4  | Generation of the FSMDs for Verification                             | . 122 |

|   |      | 6.4.1 Construction of FSMD from the CDFG                             | . 123 |

|   |      | 6.4.2 Construction of FSMD from the Scheduled Behaviour              | . 123 |

|   |      | 6.4.3 Construction of FSMD from the Allocation and Binding Results   | . 125 |

|   |      | 6.4.4 Construction of FSMD from RTL Design                           | . 126 |

|   | 6.5  | Conclusions                                                          | . 128 |

| 7 | Exp  | erimental Results                                                    | 129   |

|   | 7.1  | Introduction                                                         | . 129 |

|     | 7.2    | Synthe    | sis and Verification Results                                 | . 129 |

|-----|--------|-----------|--------------------------------------------------------------|-------|

|     |        | 7.2.1     | Effects of the Architectural Parameters on Synthesis Results | . 129 |

|     |        | 7.2.2     | Comparison with other Synthesis Tools                        | . 131 |

|     |        | 7.2.3     | Verification vs. Synthesis                                   | . 132 |

|     | 7.3    | Conclu    | isions                                                       | . 133 |

| 8   | Con    | clusions  | s and Future Scope of Work                                   | 135   |

|     | 8.1    | Summa     | ary of the Work                                              | . 135 |

|     | 8.2    | Future    | Scope of Work                                                | . 136 |

| A   | Synt   | thesis w  | ith SAST: A Case Study                                       | 139   |

| В   | Pub    | lications | s out of this work                                           | 155   |

| C   | Bio-   | data      |                                                              | 157   |

| Bil | oliogi | raphy     |                                                              | 159   |

# **List of Figures**

| 1.1  | Hierarchy of Synthesis Flow                                                           | 2  |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | The steps of high-level synthesis                                                     | 4  |

| 1.3  | Hand-in-hand synthesis and verification                                               | 14 |

| 2.1  | The FSMD corresponding to the GCD behaviour given in example 1                        | 22 |

| 2.2  | A typical path, its condition of execution and its simple data transformation         | 24 |

| 2.3  | FSMD designations in the hand-in-hand synthesis and verification flow                 | 30 |

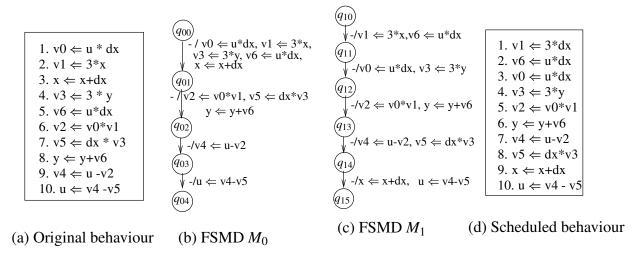

| 3.1  | Phase-wise modification of an example input behaviour by a basic block based          |    |

|      | scheduler                                                                             | 36 |

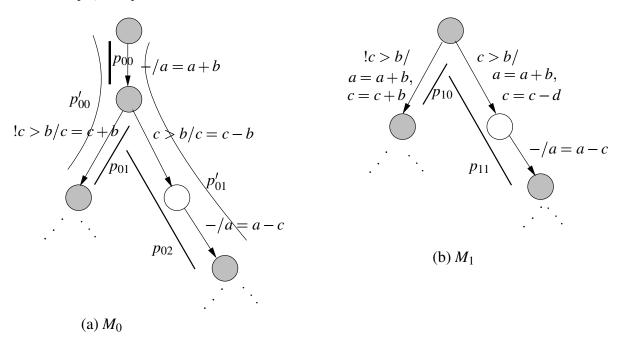

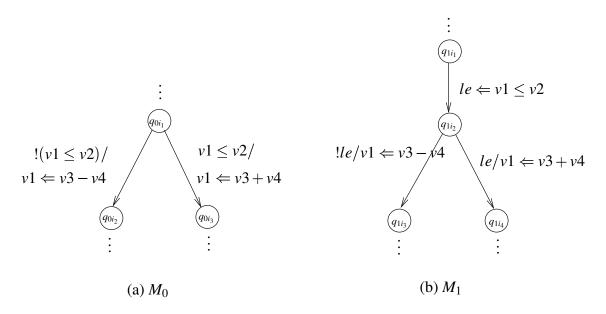

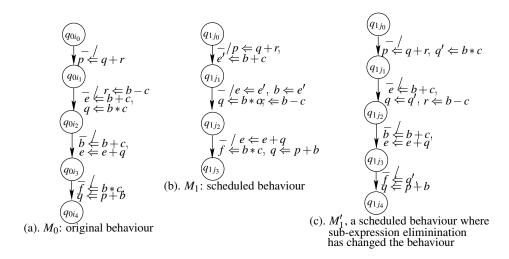

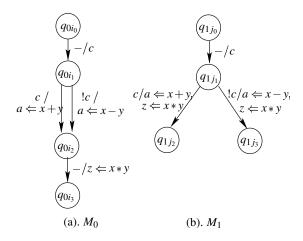

| 3.2  | Working of the proposed algorithm on an example. (a) $M_0$ : An FSMD before           |    |

|      | scheduling (b) $M_1$ : Corresponding FSMD after scheduling                            | 40 |

| 3.3  | Scheduling of a relational operation                                                  | 41 |

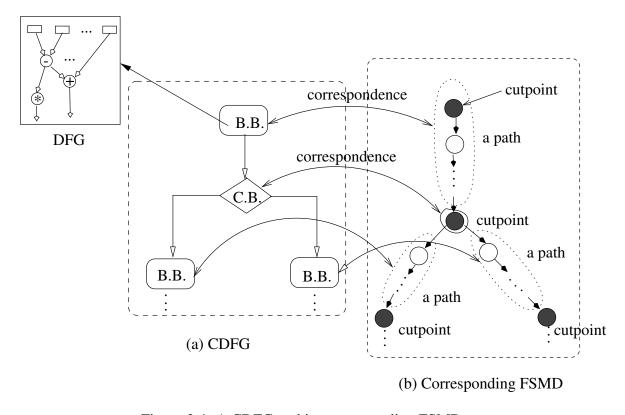

| 3.4  | A CDFG and its corresponding FSMD structure                                           | 46 |

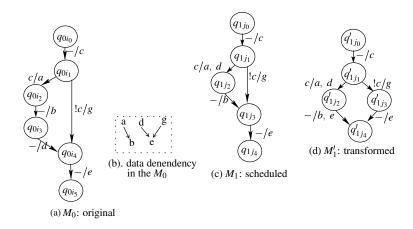

| 3.5  | The FSMDs of the GCD example (a) $M_0$ : before scheduling (b) $M_1$ : after schedul- |    |

|      | ing using a path-based scheduler                                                      | 47 |

| 3.6  | Scheduling using variable renaming technique: An example                              | 48 |

| 3.7  | Scheduling using elimination of common sub-expressions: An example                    | 50 |

| 3.8  | Conditional reuse to reduce execution time: An example                                | 52 |

| 3.9  | Reverse speculation technique: An example                                             | 53 |

| 3.10 | Reverse speculation: A special case                                                   | 54 |

| 3.11 | Early Condition Execution: An example                                                 | 55 |

| 3.12 | Conditional speculation technique: An example                                         | 56 |

| 3.13 | Conditional branch balancing: An example                                              | 57 |

| 3.14 | Speculation technique: An example                                                     | 58 |

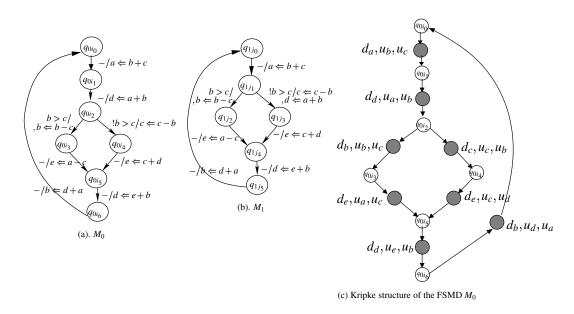

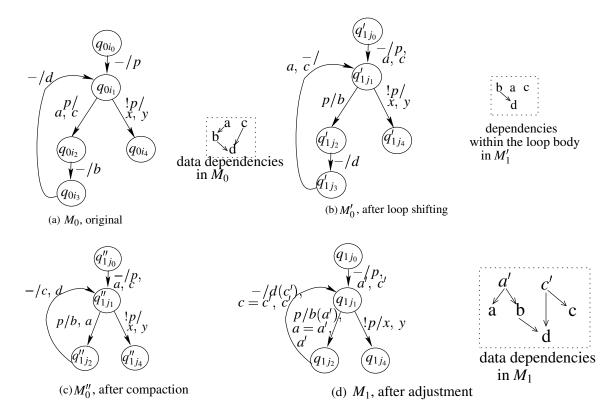

| 3.15 | Loop shifting and compaction: An example                                           |

|------|------------------------------------------------------------------------------------|

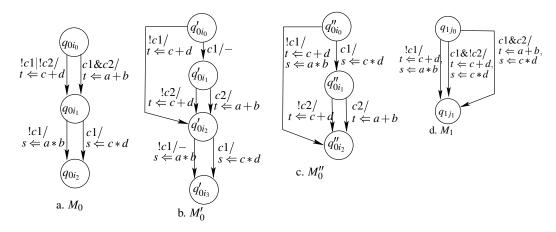

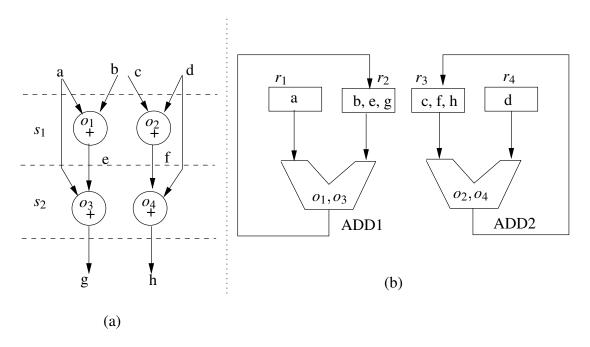

| 4.1  | An illustration of allocation and binding process: a. Scheduled behaviour b. After |

|      | allocation and binding                                                             |

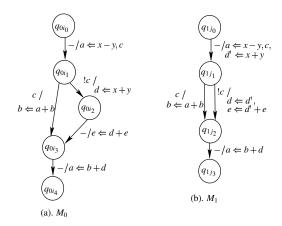

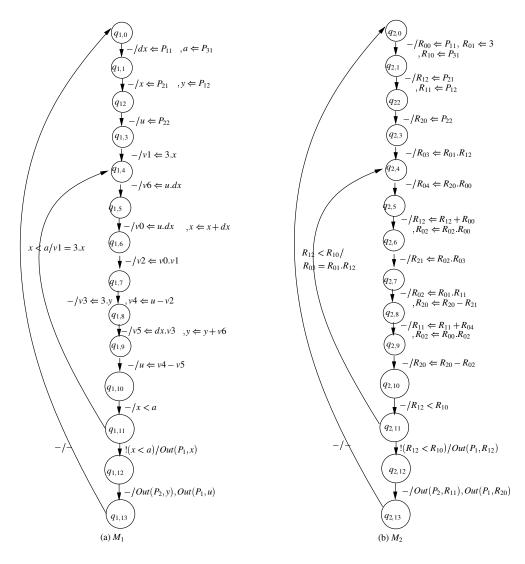

| 4.2  | DIFFEQ Example: a. FSMD after scheduling b. FSMD after allocation & binding . 66   |

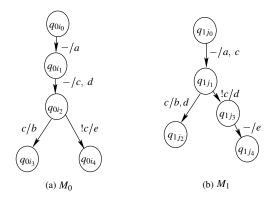

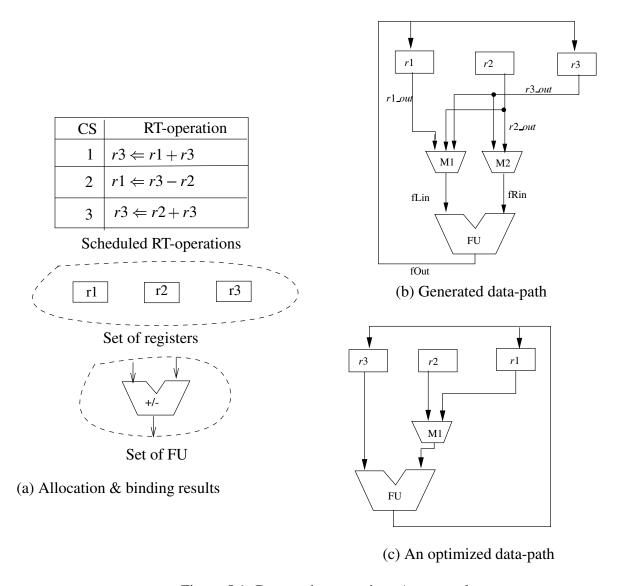

| 5.1  | Data-path generation: An example                                                   |

| 5.2  | The structure of the RTL description produced by any HLS tool                      |

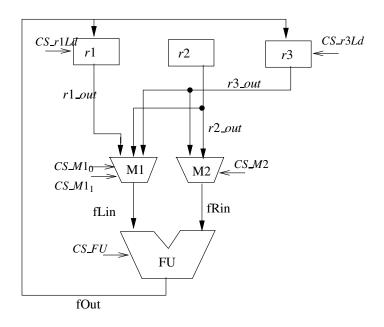

| 5.3  | Data-path with control signals                                                     |

| 5.4  | The steps of data-path and controller verification                                 |

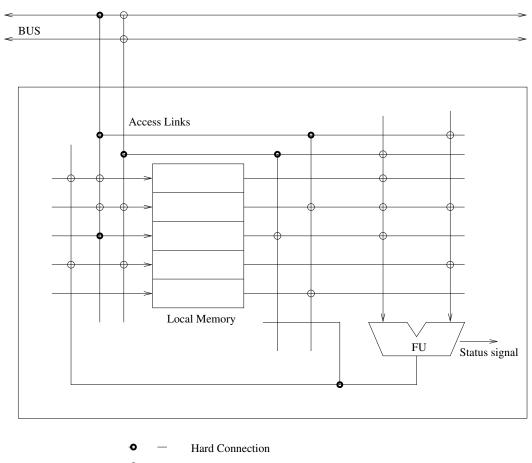

| 6.1  | Schematic of structured architecture                                               |

| 6.2  | An Architecture Block                                                              |

| 6.3  | SAST synthesis steps                                                               |

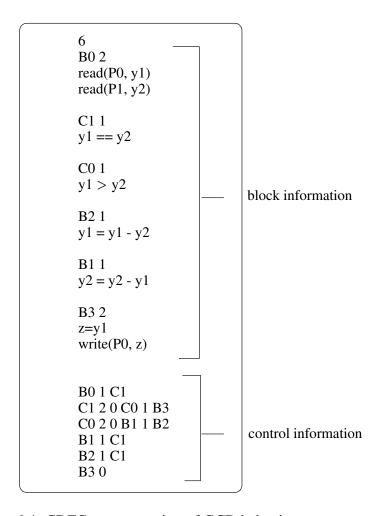

| 6.4  | CDFG representation of GCD behaviour                                               |

| 6.5  | Steps involved in CDFG generation                                                  |

| 6.6  | Data flow diagram for preprocessor before scheduling                               |

| 6.7  | A sample behavioural description                                                   |

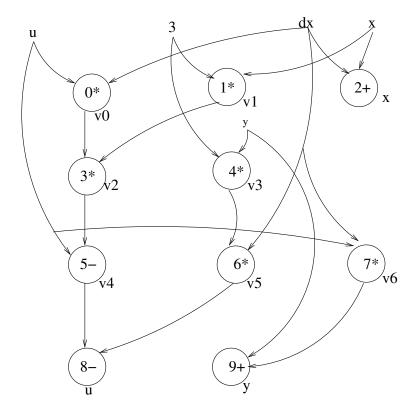

| 6.8  | Partial order for the behavioural description given in figure 6.7                  |

| 6.9  | Generating initial attributes of offspring by crossover                            |

| 6.10 | Completion algorithm                                                               |

| 6.11 | The block-diagram of the controller                                                |

| 6.12 | Generating Write Enable signals                                                    |

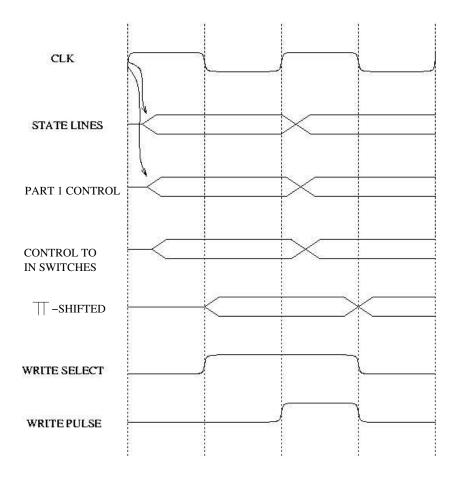

| 6.13 | Timing diagram for control and write enable signals                                |

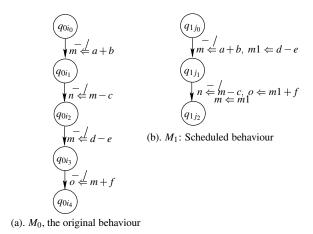

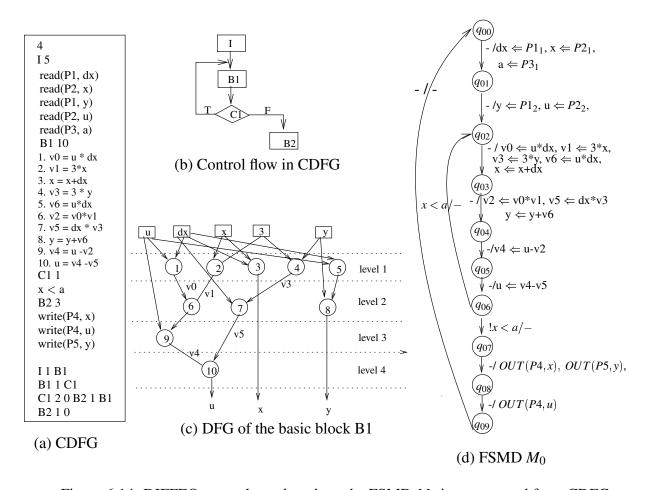

| 6.14 | DIFFEQ example to show how the FSMD $M_0$ is constructed from CDFG 125             |

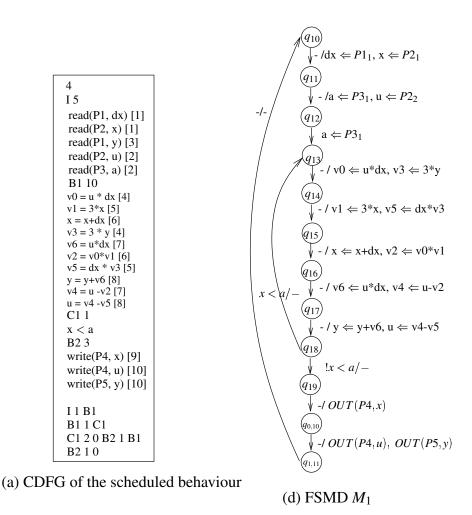

| 6.15 | DIFFEQ example: the scheduled behaviour and the FSMD $M_1$                         |

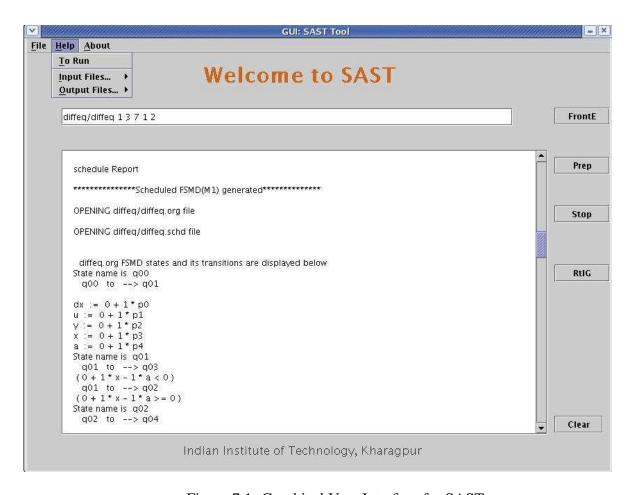

| 7.1  | Graphical User Interface for SAST                                                  |

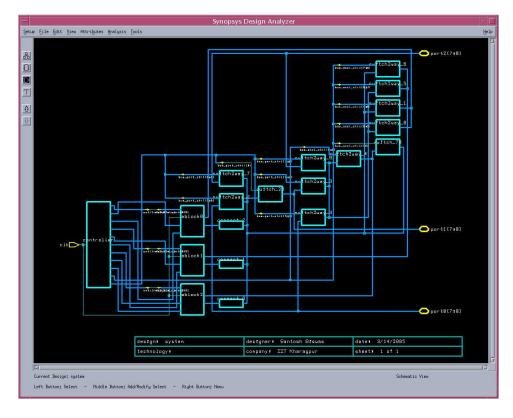

| 7.2  | Synopsys DA output for EWF                                                         |

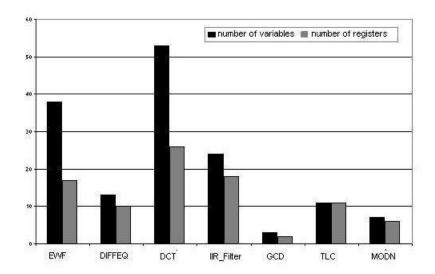

| 7.3  | The typical number of variables and the number of registers required for different |

|      | HLS benchmarks                                                                     |

## **List of Tables**

| 2.1 | Conditions on $c_1$ and $c_2$ for which $(s_1 + c_1)R_10$ implies $(s_2 + c_2)R_20 \dots 32$                                                       |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | Mapping of the registers to the variables for DIFFEQ example 67                                                                                    |

| 4.2 | Computation of data transformation of the path $q_{1,0} \Rightarrow q_{1,11}$ in $M_1 \ldots \ldots 71$                                            |

| 4.3 | Computation of data transformation of the path $q_{2,0} \Rightarrow q_{2,11}$ in $M_2 \dots 72$                                                    |

| 5.1 | The function $f_{mc}$ from the set $\mathscr{M}$ to the set $\mathscr{A}$                                                                          |

| 5.2 | Construction of the set $\mathcal{M}_A$ from the function $f_{mc}$ for the control assertion pattern                                               |

|     | $A = \langle 1, 0, 1, 1, 1, 0 \rangle \dots \dots$ |

| 6.1 | Schedule of operations of the code for DIFFEQ given in figure 6.7                                                                                  |

| 6.2 | Crossover of scheduling attributes of operation '3' of figure 6.7                                                                                  |

| 7.1 | Synthesis results for some HLS benchmarks for different architectural parameters . 131                                                             |

| 7.2 | Comparison of results with a few other synthesis tools                                                                                             |

| 7.3 | Results for different high-level synthesis benchmarks                                                                                              |

| 7.4 | Scheduling verification results for different high-level synthesis benchmarks 134                                                                  |

## Chapter 1

## Introduction, Background and Motivation

### 1.1 General Introduction

Very Large Scale Integrated Circuit (VLSI) technology provides densities of several million gates of random logic per chip. Chips of such complexity are very difficult, if not impossible, to design using the traditional capture and simulate design methodology. Furthermore, VLSI technology has also reached such a maturity level that it is well understood so as to no longer provide a competitive edge by itself. Instead, time to market is usually equally, if not more, important than area or speed. The industry has started looking at the product development cycle comprehensively to reduce the design time and to gain a competitive edge in the time-to-market race. Automation of the entire design process from conceptualization to silicon or a describe-and-synthesize design methodology has become necessary [1].

As the complexity of the chips increases, so does the need for design automation on higher levels of abstraction where functionality is easier to understand and trade-offs are more influential. There are several advantages to automating part or all of the design process and expanding the scope of automation to higher levels. First, automation assures a much shorter design cycle. Secondly, it allows for more exploration of different design styles since different designs can be generated and evaluated quickly. Finally, if synthesis algorithms are well understood, design automation tools may out-perform average human designers in meeting most of the design constraints and requirements.

Synthesis is the process of interconnecting primitive components at a certain level of abstraction (target level) to realize a specification at a higher level of abstraction (source level). Synthesis,

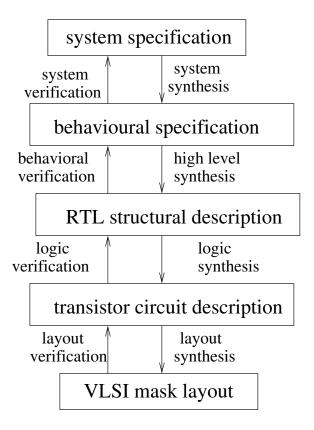

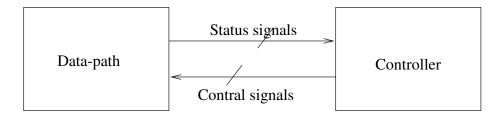

Figure 1.1: Hierarchy of Synthesis Flow

sometimes called design refinement, adds an additional level of detail that provides information needed for the next level of synthesis or for manufacturing the design. This more detailed design must satisfy design constraints supplied along with the original behavioural description or generated by a previous synthesis step. The source and target levels categorize the various synthesis systems. Several levels of the synthesis process is shown in figure 1.1. The system synthesis step takes as input a system specification involving processors and memories and outputs an equivalent functional specification. The high level synthesis (HLS) step takes an algorithmic or high level behaviour as input and outputs the register transfer level (RTL) behaviour consisting of functional units, storage and interconnection units. The logic synthesis step takes Boolean equations as inputs and generates a gate level design after performing logic optimizations of the input. The layout synthesis step takes the gate level specification and outputs the physical layout implementing the gate level specification.

### 1.1.1 High-level Synthesis

A behavioural description is used as the starting point for HLS. It specifies the behaviour in terms of operations, assignment statements, and control constructs in a hardware description language (HDL) (e.g., VHDL [2] or Verilog [3]). The output from a high-level synthesizer consists of two parts: a data path structure at the register-transfer level (RTL) and a specification of the finite state machine to control the data path. At the RTL level, a data path is composed of three types of components: functional units (e.g., ALUs, multipliers, and shifters), storage units (e.g., registers and memory), and interconnection units (e.g., buses and multiplexors). The finite state machine specifies every set of micro-operations for the data path to be performed during every control step.

In the first step of HLS, the behavioural description is compiled into an internal representation. This process usually includes a series of compiler like optimizations. In addition, it may also apply some hardware-specific transformations such as, syntactic variances minimization, retiming and those exploiting the associativity and commutativity properties of certain operations. A control/data flow graph (CDFG) is a commonly used internal representation to capture the behaviour. The control-flow graph (CFG) of the CDFG captures sequencing, conditional branching and looping constructs in the behavioural description; the data-flow graph (DFG) captures data-manipulation activities described by a set of assignment statements (operations).

The following three steps form the core of transforming a behaviour into an RTL description: scheduling, allocation and binding. Scheduling assigns operations of the behavioural description into control steps. A control step usually corresponds to a cycle of the system clock, the basic time unit of a synchronous digital system. Allocation chooses functional units and storage elements from the component library. There may be several alternatives among which the synthesizer must select the one that matches the design constraints best and maximizes the optimization objective. Binding assigns operations to functional units, variables to storage elements and data transfers to wires or buses such that data can be correctly moved around according to the scheduling.

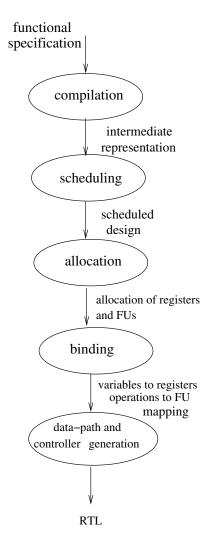

The final step of high-level synthesis is data-path and controller generation. Depending upon the scheduling and the binding information of the operations and the variables, proper interconnection between the data-path components is set up. Finally, a finite state machine is generated to control all the micro-operations over the date-path. The high-level synthesis steps are depicted in figure 1.2.

Figure 1.2: The steps of high-level synthesis

#### Requirements of High-level Synthesis Verification

The use of high-level synthesis systems becomes increasingly crucial to deal with the increasing complexity of today's VLSI designs, shorten the design cycle, search the design space and reduce the design errors. Several HLS systems like Maha [4], Hercules [5], HAL [6], Chippe [7], STAR [8], SAM [9], GABIND [10], SPARK [11] are now available to support the HLS of digital systems. Constant evolution and concurrent changes in the HLS synthesis process and in the component libraries, however, have made the synthesis steps so intricate that neither the synthesis procedures nor the component libraries can be assumed to be correct by construction. Also, there is no one-to-one correspondence between the input and the output of the HLS process. Moreover, there are several optimizations that are performed during the synthesis process, like minimization

of the control steps in scheduling, that of registers and functional units in allocation and binding, optimization of the data-path interconnections in data-path generation, minimization of control signals in the controller generation, etc. It is, therefore, necessary to carry out extensive verification of the RTL design before going to the next level synthesis.

#### 1.1.2 Formal Verification

Formal verification consists in formally establishing a relationship between an implementation and a specification. The fact that this reasoning has to be formal requires that some kind of formalism be used to express all three entities, implementation, specification, and the relationship between them.

An implementation consists of a description of actual hardware design that is to be verified. A specification is a description of the intended/required behaviour of a hardware. Formal verification involves furnishing a proof that an implementation "satisfies" a specification. The notion of satisfaction also has to be formalized, typically in the form of requiring that a certain formal relationship holds between the descriptions of the implementation and the specification. Various notions have been used by the researchers, the semantics for each of these ensuring that the intended satisfaction relation is met. The formal verification techniques can be classified in four categories:

- *Theorem proving*: The relationship between a specification and an implementation is regarded as a theorem in logic, to be proved within the context of a proof calculus, where the implementation provides axioms and assumptions that the proof can draw upon. For most of the cases, the logic has to be beyond propositional logic. Thus, we confront the undecidability result ruling out a completely automated prover.

- Model Checking: The specification is in the form of logic formula, the truth of which is

determined with respect to a semantic model provided by an implementation. This approach

is more suitable for property checking whereas the HLS verification is a problem of establishing behavioural equivalence.

- Language Containment: The language accepted by the automaton representing an implementation is shown to be in the language accepted by the automaton representing a specification. This approach cannot encompass integers or beyond and hence does not apply to HLS of say, arithmetic circuits.

• Equivalence Checking: The equivalence of a specification and an implementation is checked. In the synthesis process, the design representations are transformed from one abstraction level to its lower abstraction level. Naturally, the equivalence checking is a more suitable choice than the three approaches mentioned above for verifying the synthesis process.

Another aspect in formal verification is the model used to represent the specification and the implementation. In this work, we use FSMD (finite state machine with data-paths) instead of an FSM (finite state machine) for modeling purpose. The FSMD is a universal specification model [12], that can represent all hardware designs. An FSM (finite state machine) model works well for up to several hundred states. Beyond that, the model becomes incomprehensible to human designers. The designer tackles this problem by resorting to a control path - data path partitioning of the circuit in which all the data storage registers and the data transformation / status detection circuits are put in the data path (DP) and the sequential aspects of the behaviour are taken care of in the control path (CP) of the circuit. Starting from the initial state, the control path invokes signals which set up paths for the register transfer operations in the data path as specified in the behavioural specification; the results of these operations are available to the control path through certain status outputs of the data-path; depending upon the states of these lines, the control path assumes the next state. The entire data path state space is partitioned by some data predicates captured by the status output lines. In fact, the data path space influences the control flow of the underlying algorithm only at some time steps; at each of these steps, the data path contains at most  $2^n$  subsets where n is the number of status lines. This notion is captured in the FSMD model. If the data path contains m k-bit registers, then the data space cardinality is  $2^{mk}$ . In practice, n is never more than ten, whereas the product mk can easily be as high as one thousand. These figures clearly indicate the reduction in input state space achieved by resorting to such CD-DP partitioning. The control path, accordingly, can be modeled as an FSM with has much less number of states than what would have been possible had the entire circuit been modeled as an FSM.

## 1.2 Literature Survey on High-level Synthesis Verification

The correctness of synthesis can be ascertained before, during or after the synthesis process. Hence, synthesis verification can be classified into three categories [13, 14] - *pre-synthesis verification, formal synthesis verification, and post synthesis verification.* In this section, we give a brief survey of literature on each of these categories.

### 1.2.1 Pre-synthesis Verification

Pre-synthesis verification means proving the correctness of the synthesis procedure, i.e., it has to be proved, that the synthesis program always produces correct synthesis results with respect to the synthesis input. This is to be done by means of software verification techniques [15, 16]. In pre-synthesis verification the correctness is proved once and for all instead of deriving the correctness proof for each synthesis run separately. Software verification, however, is extremely tedious especially, for large sized programs such as the synthesis tools. Therefore, there are only a few works reported where this method is adopted for circuit synthesis verification.

Chapman et al. proposed a pre-synthesis verification technique and employed it in BEDROC HLS tool [15]. Using this tool, part of the high-level synthesis process such as, translation from high-level behavioral description language called Hardware-pal to *Dependence flow graphs*, and some scheduling algorithms were verified.

### 1.2.2 Formal Synthesis Verification

Formal synthesis means deriving formally the synthesis result within some logical calculus. In conventional synthesis, hardware is represented by arbitrary data structures and there are no restrictions on the transformations on these data structures. In formal synthesis, hardware is represented by means of terms and formulae and only correctness preserving logical transformations are allowed. Restricting synthesis to only correctness preserving logical transformations guarantees the correctness of the synthesis procedure in an implicit manner. In contrast to conventional synthesis, the result is not only some hardware implementation but also a proof of its correctness with respect to the specification.

In [17], a formal synthesis tool, called HASH, is developed and applied in scheduling verification. Each transformation in HASH takes the current design state and the result of some synthesis heuristic and returns a new design state along with the correctness theorem, starting that the old design state is equivalent to (or implied by) the new design state. Exploiting the idea of separating the design space exploration from the formal derivation, the HASH project defines a set of guidelines to formalize both the behaviour and the design decisions taken as higher-order  $\lambda$ -expressions. The system uses theorem prover HOL to decide the soundness of those decisions. Although HASH performs the verification automatically, the formalism used to represent the behaviours and the circuits has limited expressive power and the verification time grows exponentially unless HOL

kernel is modified.

Another formal synthesis system called *FRESH* was built and a new technique for verification was proposed in [18]. In this method, the input behaviour is described by using equational specification (ES) and a set of derivation rules is applied consecutively on the ES. This formal synthesis verification technique is used to check the correctness of scheduling, allocation and binding steps. The distinctive characteristic of these formal synthesis systems is the development of formal design environments where the mathematical representation of a behaviour can be transformed only by the application of sound rules. But the weak relationship between the formal transformations and their underlying hardware concepts forces these systems to be manually driven by the designer, who has to understand the mathematical formalism.

### 1.2.3 Post-synthesis Verification

Post-synthesis verification is the most frequently used approach today [13]. In post-synthesis verification the synthesis step is first performed in a conventional manner and then the correctness of the synthesis output with respect to the synthesis input is proved. It is independent of the synthesis procedure. The only information available is the synthesis input and the synthesized output. There is no information on how the output was derived from the input. The work, proposed in this thesis, belongs to this category. Several post-synthesis verification techniques of high-level synthesis are reviewed in the following.

#### **Simulation-based Verification Approaches**

In simulation based verification, the design to be verified is simulated with a suite of test vectors and the output responses are compared with that of a *golden model*. Ernst et al. proposed a simulation-based verification for high-level synthesis in [19]. Their system, called *Satya*, maps an algorithmic description to a logic circuit description, compares the two descriptions to detect semantic errors and identify the causes of those errors. The authors have used *Satya* to verify the *Bridge* synthesis system [20]. Limitation of this system is that verification is at the level of scheduled specification and in the original behavioural level [21].

In [22], a technique for augmenting simulation based verification at RTL level is reported. In this method, the designer of an RTL circuit embeds a small amount of well understood extra functionality or behaviour into the circuit verification. This extra behaviour is inserted into both

the golden model and the also the circuit under verification. During simulation based verification, this extra behaviour is used along with the existing behaviour of the circuit to exercise the design more throughly. Once the circuit is throughly verified for the functionality, the extra behavioural constructs can be removed to produce the original verified design. Embedding the extra behaviour automatically in the RTL design produced by an HLS, however, is the main bottleneck of this approach.

Another simulation-based methodology, called *Observable time windows (OWT)*, is proposed in [21] for verification of high-level synthesis results. In this work, the notion of equivalence between the behaviour before scheduling (specification) and the implementation is defined. OWTs correspond to the instants in the simulation run of the implementation which can be directly compared with those in the simulation result of the specification. This approach is implemented in the HIS system reported in [23].

As the complexity of digital systems increases, normal simulation based methods of design validation are becoming impractical due to the large number of internal states [24]. Also, a simulation based approach cannot prove that the result of synthesis is correct as formal verification would do because the former is non-exhaustive.

#### **End-to-end Verification of High-level Synthesis**

A set of high-level synthesis systems is validated using formally verified transformations in [25]. This tool examines the output of a high-level synthesis system and derives a sequence of behaviour-preserving (correct) transformations (witness) that leads to the same effect as the applied HLS algorithm. If every transformation, identical in the derived sequence, is applied in the presence of a set of preconditions (which are proved to lead to a correct design), then the resulting RTL design is correct. The approach is as follows. A set of elementary structural transformations is specified and proved for correctness in PVS. Now, given a high-level behaviour, an initial design is derived by interpreting the control and data flow graph (CDFG) to form a unique ALU in the data-path to implement each operation in the behaviour, a unique register to store each value and a unique wire to carry each data flow. The transformations are applied to this initial design. It has a *witness generator* which takes the output of an existing synthesis tool for that given high-level behaviour as input and generates a sequence of elementary transformations which, when applied to the RTL design, achieve the same outcome.

A formal approach to address the correctness of transformations in high-level synthesis is proposed in [26]. This work was part of the SPRITE project at *philips research laboratories*. Both the specification at the behavioural level and the implementation at the RTL level are encoded in SIL [27] in this work. A small set of properties (axioms) corresponding to the SIL graph is asserted to be true. These axioms capture the general notion of refinement of the CDFG used in various synthesis frameworks. Other properties are checked to be true by applying a small number of inference rules on properties that have already been verified. The practicality of the tool, however, was not established as it was not integrated with any HLS CAD tool.

An equivalence checking between behavioural and RTL descriptions with virtual controllers and data-paths is reported in [28]. In order to compare the behavioral and the RTL descriptions in a uniform way, a framework for verification and reasoning of the descriptions based on mapping to virtual datapaths/controllers from these descriptions is developed in this work. Once those mappings have been established, the real comparison can be based on the data transfer analysis controlled by finite state machines; and the verification of arithmetic/logic functionality can be done separately. Virtual datapaths are essentially in net-list form and virtual controllers are represented as finite state machines. There are two key ideas behind this approach. One is to convert equivalence checking on the two descriptions to equivalence checking on their virtual controllers by using the same virtual datapaths for the two descriptions to be checked. The other is to reduce the comparison between two finite state machines to pure topological analysis on the structure of the finite state machines by utilizing equivalence classes on the sets of sub-machines. Normally, equivalence checking between the two descriptions can be made by reachability analysis which is very expensive. In this work, the same virtual data path has been used for the two virtual controllers to be compared thereby easily reducing the problem to the one of the comparison of two virtual controllers only. How the equivalence checking works when the two descriptions are very different and they cannot be mapped to the same data path, however, is not discussed in this work.

In [29], the RTL generated by an HLS tool is verified against its input specification. This technique of determining the correctness of the RTL design depends upon comparing the values of certain critical specification variables in certain critical behavioural states with those of certain critical RTL registers in certain critical controller states, provided they match at the start state. It is accomplished by showing that for each critical path between a pair of critical states, if the critical variables match the critical registers at the originating state, then they will match them at the terminating state. The technique is integrated with DSS [30] high-level synthesis system. This

approach, however, necessitates that the control flow branches in the behaviour specification are preserved and no new control flow branches are introduced. This condition may not hold for the path-based scheduler.

The end-to-end HLS verification techniques are not efficient enough as it is not only error prone but also unable to find the exact sub-task in which the error occurs. Also, the sub-tasks of HLS are interdependent on each other. If an error occurs in the early steps in the synthesis process, it has to be fixed at that moment. Otherwise, it will propagate to the subsequent steps resulting in avoidable wastage of time and longer design cycles.

#### Verification of the High-level Synthesis Sub-tasks

To overcome the problem discussed above, several approaches are proposed in the literature to verify the sub-tasks of the HLS process. They are typically scheduling verification, allocation and binding verification and RTL verification. Some of the allocation and binding verification methods treat the allocation, binding and the data-path and controller generation steps into one by verifying the final RTL against the scheduled behaviour. In the following, the verification of different subtasks of HLS are discussed.

#### **Scheduling Verification**

Verification of *As-Soon-As-Possible (ASAP)* scheduling algorithm is reported in [31]. The high-level design description is represented as a state table format (STF) here. The STF semantics are embedded using a library of some inductively defined relations and functions which make up the scheduling algorithm. The relations and the functions are defined using the standard recursive and non-recursive definition mechanisms of HOL [32].

A formal specification and proof of correctness of widely used Force-Directed List Scheduling (FDLS) algorithm for resource-constrained scheduling in high-level synthesis systems is presented in [33]. In this approach, the base specification model for the scheduling task is identified first. Next, the specification model is formalized as a collection of theorems in a higher-order logic theorem proving environment. Finally, the formal description of the algorithm is verified against the base theorems.

The above two approaches, however, are applicable only to a certain class of scheduling algorithms.

A formal verification of scheduling process using finite state machines with data-path (FSMD) is reported in [34]. In this paper, break-points are introduced in both the FSMDs followed by construction of the respective path sets. Each path of one set is then shown to be equivalent to some path of the other set. This approach necessities that the path structure of the input FSMD is not disturbed by the scheduling algorithm in the sense that the respective path sets obtained from the break points are assumed to be bijective. This property, however, does not necessarily hold because the scheduler may merge the segments of the original specification into one segment or distribute operations of a segment over various segments for optimization of time steps.

An automatic verification of scheduling by using symbolic simulation of labeled segments of behavioural descriptions has been proposed in [14]. In this paper, both the inputs to the verifier, namely the specification and the implementation, are represented in the *Language of Labeled Segments (LLS)*. Two labeled segments  $S_1$  and  $S_2$  are bisimilar iff the same data-operations are performed in them and control is transformed to the bisimilar segments. The method described in this paper transforms the original description into one which is bisimilar with the scheduled description.

Most of the methods discussed above are well suited for basic block based scheduling [35, 36] where control structure of the input does not get changed by the scheduler; they fail for path-based scheduling algorithms [37, 38] as well as when some code motion techniques [39, 40, 41, 42] are used by the scheduler.

#### **Allocation and Binding Verification**

A compositional model for the functional verification of high-level synthesis is proposed in [43]. The method is applicable to the verification of the final synthesis steps in which both the inputs to the verifier, the specification and the implementation, are encoded as FSMDs. The FSMD corresponding to the implementation comprises two parts, namely the operative part FSMD or the data-path and the controller FSMD. Demonstrating the equivalence of the composed FSMD (functional composition of control and operative part) with the scheduled FSMD accomplishes the functional verification.

A formal methodology for verification of various register allocation schemes was proposed in [44]. The scheduled and the RTL description are encoded as *extended finite state machines* (*EFSMs*) in this work. The method consists in determining the equivalence of critical states, critical variables and critical paths of two EFSMs. A preliminary version of this work, reported in [29],

which can be integrated with synthesis systems which performs little register optimization. One may, however, encounter an infinite number of execution paths from the initial state during showing the equivalence between two critical states in the presence of loops in the behaviour.

The method in [45] checks the correctness of the register transfer level (RTL) description with respect to the scheduled behaviour. The major contribution of this work is the partitioning of the equivalence checking task into two simpler subtasks, verifying the validity of register sharing and verifying the correctness of synthesis of the RTL interconnection and the controller. The irrelevant portions of the design are automatically abstracted out simplifying the register sharing verification task, the later being performed by a model checker. Verifying the RTL is reduced to a combinational equivalence check; a novel and fast RTL technique for combinational equivalence check instead of using slower global gate level checking is also presented.

The work proposed in [46] handles the high-level verification in two steps: verification of scheduling and verification of allocation and final architecture generation. This paper mainly high-lighted the verification of allocation and final architecture generation tasks. The goal is achieved by ensuring that the correct FU has been chosen, the correct functionality of the FU has been chosen, the communication network has been correctly generated to allow the necessary data flow for a specified operation and the control signals have been assigned for each operation of the behaviour. The approach, however, ignores register sharing verification.

## 1.3 Motivation and Objectives of the Present Work

An end-to-end verification method for HLS is very tough and also inadequate in locating the exact source(s) of errors. A phase-wise verification technique with scope to handle the difficulties of each synthesis sub-task separately is necessary for high-level synthesis because of the following reasons. First, the input behavioural specification is given at a very high abstraction level compared to the abstraction level of the output (RTL); secondly, the complexity of the present day VLSI systems is very high; thirdly, the HLS process consists of several sub-tasks such as, scheduling, allocation, binding, data-path and controller design, etc., which are performed sequentially and each sub-task depends mainly on the result of the previous stages. In contrast to end-to-end verification if the correctness of the intermediate results is verified after every sub-task of the HLS process, then we can also easily find the origin of the errors.

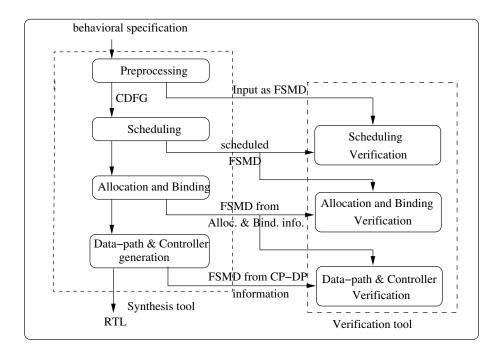

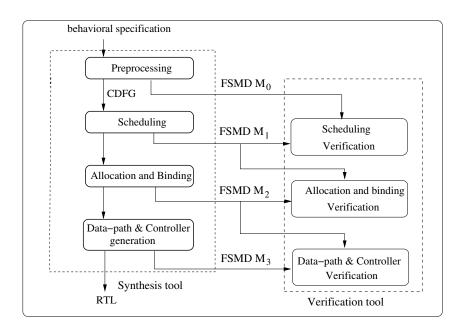

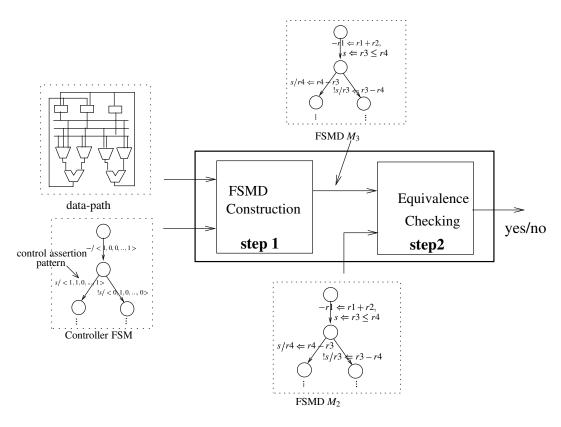

• In this work, the correctness of the HLS process is verified in three phases. Phase-I verifies

the scheduling process. In phase-II, the allocation and binding process is verified against the scheduled behaviour. Phase-III ensures the correctness of the data-path interconnections and the controller. The proposed hand-in-hand synthesis and verification framework is shown in figure 1.3.

Figure 1.3: Hand-in-hand synthesis and verification

Several works proposed in the literature for verification of different phases of HLS are not strong enough in the sense that they fail in some circumstances which are very common to the modern HLS tools. For example, the proposed methods in the literature for scheduling verification are likely to fail for path-based scheduling algorithms as well as when code motion techniques [47] are used by the scheduler. Hence, more sophisticated verification methodologies are required to cope with these difficulties.

• In this work, an equivalence checking method is proposed which is equipped to handle these difficulties. This method can be applied to the first two phases of HLS verification. The input and output of each of these two phases are encoded as finite state machines with data-paths (FSMDs) and our proposed method finds the equivalence between these two FSMDs.

The verification of the data-path interconnections and the controller behaviour is not an easy task. It consists in analyzing the data-path to find a *spatial sequence* of concurrent micro-operations

needed to accomplish a register transfer (RT) operation and ensuring that the controller generates correct control signals in each control step to perform the required RT operations in the data-path. To the best of our knowledge, no work has been reported in the literature for handling these tasks separately.

• In this work, a state based equivalence checking method is proposed for this phase to accomplish all these tasks. The method uses a *rewriting procedure* to find the spatial sequence of the concurrent micro-operations to establish that the control assertion pattern in each control step is correct.

### 1.4 Contributions of the Present Work

#### • Equivalence problem formulation

A formal method for checking equivalence between two FSMDs is formulated. The method consists in introducing cutpoints in one FSMD, visualizing its computations as concatenations of paths from cutpoints to cutpoints and finally, identifying equivalent finite path segments in the other FSMD; the process is then repeated with the FSMDs interchanged.

#### • Normalization of arithmetic expression over integers

Finding equivalence between two paths involves checking equivalence between two sets of arithmetic expressions. Hence, checking equivalence of two paths reduces to the validity problem of first-order logic which is undecidable; thus, a canonical form does not exist for integer arithmetic. Instead, in this work we adapt a normal form [48] for the arithmetic expressions over integers. The normalization process renders many computationally equivalent formulas syntactically identical as it forces all the formulas to follow a uniform structure.

#### • Hand-in-hand verification of high-level synthesis

Our goal is to find equivalence between the behavioural description given as input to any HLS tool and the RTL output of that HLS tool. This verification goal is achieved in three phases as discussed in subsection 1.3 and the verification process needs to proceed hand-in-hand with the synthesis process. The hand-in-hand synthesis and verification framework is depicted in figure 1.3. An overview of these three phases of verification is as follows:

Scheduling verification: The goal of the scheduling process is to optimize the number of control steps required to execute all the operations in the input behaviour meeting all the constraints regarding the number of control steps, the delay, the power and the hardware resources. A path-based scheduler [37] [38] may modify the control structure of the input behaviour as it tries to merge some consecutive path segments of the input behaviour. Also, use of several code motion techniques like speculation, reverse speculation, early condition execution, branch balancing, common sub-expression elimination, loop shifting, renaming, etc, [47, 49, 39, 41], in the scheduling process leads to different transformations in the input behaviour of HLS. The goal of the scheduling verification process is to ensure that the scheduling process preserves the input behaviour, irrespective of the scheduling technique used. The FSMD equivalence checking method proposed in this work meets the requirements for this phase of verification.

Allocation and binding verification: The number of functional units (FUs) selected for performing the operations is less than or equal to the number of operations. Similarly, the number of registers used to store the variables of the behaviour is less than or equal to the number of variables. It is required to ensure that enough number of FUs and registers are allocated and their binding with the operations and variables, respectively, are also proper. The verification of this phase consists of two tasks: (i) verification of the functional unit allocation and binding, and (ii) verification of register sharing among the behavioural variables. Our proposed equivalence checking method has been shown to be applicable to register sharing verification.

Data-path and controller verification: The objective of the data-path generation is to maximize sharing of interconnections and thus minimize the interconnection cost avoiding conflict during data transfers required by the register transfer (RT) operations. Similarly, minimum number of control signals are used by the controller to control all the data transfers among the data-path elements. The controller, represented as an FSM, assigns a value to each control signal in each control step to execute all the required data-transfers and proper operations in the FUs. The verification task in this phase is to ensure the correctness of the data-path interconnections and the controller. The verification involves the following tasks: (i) construction of an FSMD from the data-path and the controller FSM and (ii) showing equivalence between the input FSMD and the output FSMD.

#### • Development of a high-level synthesis tool

We have developed the above hand-in-hand synthesis and verification framework, called *structured architecture synthesis tool (SAST)*. It takes a synthesizable behavioural description and produces an RTL code in Verilog. SAST is an interconnection aware high-level synthesis tool as it produces a *structured data-path (structured architecture)* by avoiding random interconnections among the data-path components. The tool provides required information for verification from its intermediary synthesis results and supports the hand-in-hand synthesis and verification. Finally, it produces a *correct* RTL behaviour in Verilog.

## 1.5 Organization of the Thesis

The rest of the thesis is organized as follows.

**Chapter 2**: In this chapter, the equivalence problem of FSMDs has been formulated, the basic method has been devised and the correctness of the method has been proved. A normal form for the expressions and several simplifications that have been carried out on the normalized expressions are discussed next.

**Chapter 3**: This chapter discusses the scheduling verification phase. The objective of the scheduling verification is identified first. The required modifications on the basic equivalence checking method are given. An algorithm for verifying the correctness of the scheduling result is proposed and its correctness and complexity have been analyzed subsequently. The performance of this algorithm for different scheduling algorithms and on various code motion techniques are discussed next. Some upgradations of the algorithm, needed to handle the above tasks, are also proposed in this chapter.

**Chapter 4**: This chapter discusses the allocation and binding verification phase. The objectives of the this phase of verification is enlisted. The verification of FU allocation and binding is given next. It is followed by the register sharing verification. Some mapping functions are defined and also the modification required on definition of equivalence of paths is discussed. A register sharing verification method is proposed next. The working of the algorithm is discussed with an example. The performance of this method for different register optimization schemes as well as for various nature of the input specification have been provided.

**Chapter 5**: This chapter discusses the verification of data-path and controller synthesis. The objectives of this phase are identified first. The construction of the FSMD from the control-path and

data-path information is discussed. A rewriting algorithm involved in the construction mechanism is given next. Termination, soundness and completeness of the method have been proved and the complexity of the method is also analyzed. The construction process is described with an illustrative example. The verification of the data-path and the controller during FSMD construction is given next. Finally, a state-based verification method for verifying the functionality of the RTL behaviour is proposed.

**Chapter 6**: This chapter discusses the proposed target data-path, the details of the synthesis phases of SAST and the method for generating the FSMD from the input and the output of each synthesis phase.

**Chapter 7**: This chapter provides some synthesis and verification results.

**Chapter 8**: The chapter contains some concluding remarks and identifies some future research directions.

## **Chapter 2**

## The Equivalence Problem Formulation

### 2.1 Introduction

This chapter is concerned with the theoretical issues behind our proposed verification methodologies of different phases of high-level synthesis. The finite state machine with data-path (FSMD) proposed in [12] has been adapted for design representation in this work. The notion of paths in FSMD, the transformations along a path and the computation and path cover of an FSMD are defined. The equivalence of two FSMDs has been derived and proved. The basic method for checking equivalence of two FSMDs is also provided. The normal form of the expression and the simplifications over the normalized expressions are also discussed in this chapter.

## 2.2 Finite State Machines with Data-paths

An FSMD (finite state machine with data-path) is a universal specification model, proposed by Gajski et al. in [12], which can represent all hardware designs. The model is used in the present work with the addition of a reset state, for encoding the designs to be verified. This reset state is also called the start state of the FSMD. The FSMD is defined as an ordered tuple  $\langle Q, q_0, I, V, O, f, h \rangle$ , where

- 1.  $Q = \{q_0, q_1, q_2, \dots, q_n\}$  is the finite set of control states,

- 2.  $q_0 \in Q$  is the reset state,

- 3. *I* is the set of primary input signals,

- 4. V is the set of storage variables,

- 5. *O* is the set of primary output signals,

- 6.  $f: Q \times 2^S \to Q$ , is the state transition function and

- 7.  $h: Q \times 2^S \to U$ , is the update function of the output and the storage variables, where *S* and *U* are as defined below.

- (a)  $S = \{L \cup E_R \mid L \text{ is the set of Boolean literals of the form } b \text{ or } \neg b, b \in B \subseteq V \text{ is a}$ Boolean variable and  $E_R = \{e \mid R \mid 0 \mid e \in E_A\}\}$ ; it represents a set of status expressions over  $I \cup V$ , where  $E_A$  represents a set of arithmetic expressions over the set  $I \cup V$  of input and storage variables and R is any arithmetic relation.  $R \in \{==, \neq, >, \geq, <, \leq\}$ .

- (b)  $U = \{x \leftarrow e \mid x \in O \cup V \text{ and } e \in E_A \cup E_R\}$  represents a set of storage or output assignments.

Conjunction is assumed to be the implicit connective among the relational expressions belonging to  $2^S$ . Parallel edges between two states capture disjunction of status expressions. Thus, the next (control and data) state and the output depend not only on the present state and the input signals but also on the conjunction of the status expressions that indicate whether a predicate holds on the data state of the storage and the input variables. An FSMD is inherently deterministic, that is, the state transition function f satisfies the property  $s_j = s_k \Rightarrow f(q_i, s_j) = f(q_i, s_k)$ . It may be noted that we have not introduced final states in the FSMD model as we assume that a system works in an infinite outer loop.

The behavioural description of the *extended euclidean algorithm for finding the greatest com*mon divisor (GCD) of two integer numbers [50] is given below and its FSMD is shown in the figure 2.1.

#### Example 1 Behavioural description of GCD is:

```

begin

main_process: process

Input: P0, P1;

Output: yout;

Variable : res, y1, y2 : integer;

begin

```

```

mainloop: loop

y1 \Leftarrow P0;

y2 \Leftarrow P1;

res \Leftarrow 1;

while(!(y1 == y2)) loop

if (even(y1)) then

if (even(y2)) then

begin

res \Leftarrow res * 2;

y1 \Leftarrow y1/2;

y2 \Leftarrow y2/2;

end

else

y1 \Leftarrow y1/2;

else if (even(y2)) then

y2 \Leftarrow y2/2;

else if(y1 > y2) then

y1 \Leftarrow y1 - y2;

else

y2 \Leftarrow y2 - y1;

end if;

end loop;

res \Leftarrow res * y1;

yout \Leftarrow res;

end loop mainloop;

end process main_process;

end behv;

```

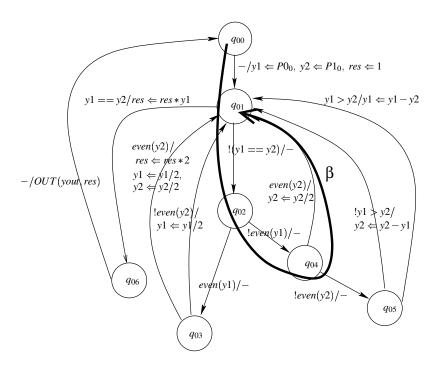

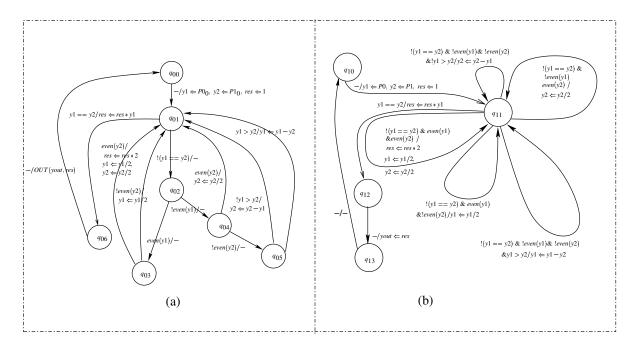

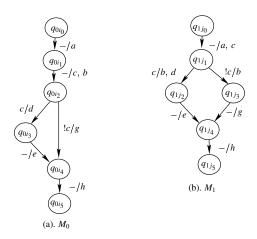

**Example 2** The FSMD model  $M_0$  for the behavioural specification of GCD example is given below and depicted in figure 2.1.

•  $M_0 = \langle Q, q_0, I, V, O, f, h \rangle$ , where

Figure 2.1: The FSMD corresponding to the GCD behaviour given in example 1

- $Q = \{q_{00}, q_{01}, q_{02}, q_{03}, q_{04}, q_{05}, q_{06}\},\$

- $q_0 = q_{00}$ ,

- $V = \{res, y1, y2\},\$

- $I = \{P0_0, P1_0\},\$

- $O = \{yout\},\$

- $U = \{y1 \Leftarrow P0_0, y2 \Leftarrow P1_0, res \Leftarrow res * 2, y1 \Leftarrow y1/2, y2 \Leftarrow y2/2, y1 \Leftarrow y1 y2, y2 \Leftarrow y2 y1\},$

- $S = \{even(y1), even(y2), y1 > y2\}$ , where even(y) indicates  $y \mod 2 = 0$ ,

- f and h are defined as in the transition graph shown in figure 2.1.

- Some typical values of f and h are as follows:

- $f(q_{00}, true) = q_{01},$

- $f(q_{05}, y_1 > y_2) = q_{02},$

- $h(q_{05}, y_1 > y_2) = \{y_1 \leftarrow y_1 y_2\},\$

- $h(q_{03}, even(y2)) = \{res \Leftarrow res * 2\}.$

### 2.2.1 Paths and Transformations along a Path

**Definition 1** *Path*  $\alpha$  *from*  $q_i$  *to*  $q_j$ :

A (finite) path  $\alpha$  from  $q_i$  to  $q_j$ , where  $q_i, q_j \in Q$ , is a finite transition sequence of states of the form  $\langle q_i = q_1 \xrightarrow{c_1} q_2 \xrightarrow{c_2} \dots \xrightarrow{c_{n-1}} q_n = q_j \rangle$  such that  $\forall l, 1 \leq l \leq n-1, \exists c_l \in 2^S$  such that  $f(q_l, c_l) = q_{l+1}$ , and  $q_k$ ,  $1 \leq k \leq n-1$ , are all distinct. The end state of the path, i.e.,  $q_n$ , may be identical to any state  $q_k$ ,  $i \leq k \leq n-1$ , along the path.

A path, say  $\beta$ , is indicated by the bold arrows in figure 2.1. Here,  $\beta$  is  $q_{00} \rightarrow q_{01} \xrightarrow{|(y1=-y2)|} q_{02}$   $\xrightarrow{|(even(y1))|} q_{04} \xrightarrow{even(y2)} q_{01}$ . Since there may be more than one transition from a state  $q_i$  to a state  $q_j$  (with different conditions  $c_l$  associated with them), a sequence of states alone does not uniquely characterize a path and has been used only when there is no ambiguity. The state sequence  $q_{01} \rightarrow q_{02} \rightarrow q_{03} \rightarrow q_{01}$  in figure 2.1, for example, does not uniquely represent a path as there is more than one transition between the two states  $q_{03}$  and  $q_{01}$ . Whereas, the state sequence  $q_{00} \rightarrow q_{01} \rightarrow q_{02} \rightarrow q_{03}$  in this figure represents a path uniquely.

**Definition 2** *The condition of execution of a path*  $\alpha$  ( $R_{\alpha}$ ):

Let  $\alpha = \langle q_{l_0} \xrightarrow[c_0]{} q_{l_1} \xrightarrow[c_1]{} q_{l_2} \dots \xrightarrow[c_{k-1}]{} q_{l_k} \rangle$  be a path. The condition of execution  $R_{\alpha}$  of the path  $\alpha$  is a logical expression over  $I \cup V$  such that  $R_{\alpha}$  is satisfied by the (initial) data state at  $q_{l_0}$  iff the path  $\alpha$  is traversed.

Thus,  $R_{\alpha}$  is the weakest precondition of the path  $\alpha$  [51].

For example, the condition of execution  $R_{\beta}$  of the path  $\beta$  of figure 2.1 is  $!(P0_0 == P1_0) \land !even(P0_0)$   $\land even(P0_0)$ . It is assumed that the inputs and the outputs occur through named ports. The  $i^{th}$  input from port P is a value represented as  $P_i$ . Thus, if some variable v stores an input from port P (for the  $i^{th}$  time along a path), it is equivalent to the assignment  $v \Leftarrow P_i$ . The variable 'y1' in the GCD algorithm of example 1 is updated by the  $0^{th}$  input from the port P0. This is shown as  $y1 \Leftarrow P0_0$  in the corresponding FSMD in figure 2.1. Similarly, the variable 'y2' stores the  $0^{th}$  input from the port P1 and is shown accordingly as  $y2 \Leftarrow P1_0$  in the FSMD in figure 2.1. In essence,  $P_i$ 's comprise the input variable set I.

#### **Definition 3** *The simple data transformation of a path* $\alpha$ *over* $V(s_{\alpha})$ *:*

It is an ordered tuple  $\langle e_i \rangle$  of algebraic expressions over the variables in V and the inputs in I such that the expression  $e_i$  represents the value of the variable  $v_i$  after the execution of the path in terms of the initial data state (i.e., the values of the variables at the initial control state) of the path.

The data transformation  $s_{\beta}$  of the path  $\beta$  in figure 2.1 is  $\langle P0_0, P1_0/2, 1 \rangle$ , where the order of the variables is  $y1 \prec y2 \prec res$ .

The above definition does not take into account the outputs that may occur in a path. The output of an expression e to a port P is represented as OUT(P, e) and put as a member of a list preserved for each path. Taking into account the outputs that may occur in a path, the data transformation of a path may be defined as follows.

**Definition 4** The data transformation  $r_{\alpha}$  of a path  $\alpha$  over V is the ordered pair  $\langle s_{\alpha}, O_{\alpha} \rangle$ , where  $s_{\alpha}$  is the simple data transformation of  $\alpha$  and the output list  $O_{\alpha} = [OUT(P_{i_1}, e_1), OUT(P_{i_2}, e_2), \ldots]$ . For every expression e output to port P along the path  $\alpha$ , there is a member of the form OUT(P, e) in the list, in the order in which the outputs occurred.

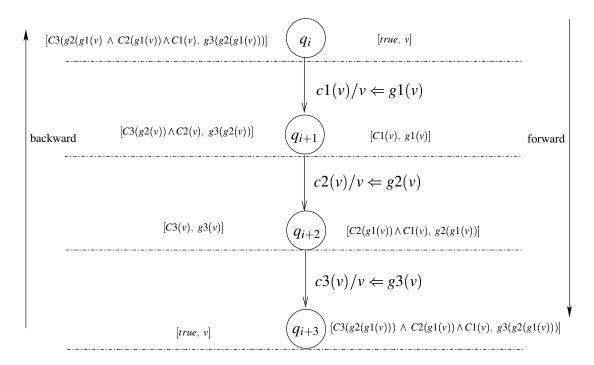

Figure 2.2: A typical path, its condition of execution and its simple data transformation

#### **2.2.2** Computation of $R_{\alpha}$ and $r_{\alpha}$

Computation of the condition of execution  $R_{\alpha}$  can be by *backward* substitution or by *forward* substitution. The former is based on the following rule: If a predicate c(y) is true after assignment  $y \leftarrow g(y)$ , then the predicate c(g(y)) must have been true before the assignment [52]. The transformation  $s_{\alpha}$  is found indirectly using the same principle. The forward substitution method of finding  $R_{\alpha}$  is based on symbolic execution. The ordered pairs at various points in figure 2.2 represents the values of  $(R_{\alpha}, s_{\alpha})$  at that point.

#### 2.2.3 Characterization of Paths

The characteristic formula  $\tau_{\alpha}(\overline{\nu}, \overline{\nu}_f, O)$  of the path  $\alpha$  is  $R_{\alpha}(\overline{\nu}) \wedge (\overline{\nu}_f = s_{\alpha}(\overline{\nu})) \wedge (O = O_{\alpha}(\overline{\nu}))$ , where  $s_{\alpha}$  is the data transformation and  $O_{\alpha}$  is the output list in the path  $\alpha$ ,  $\overline{\nu}$  represents a vector of values of the variables of  $I \cup V$ ,  $\overline{\nu}_f$  represents a vector of values of the variables of V. The formula captures the following: if the condition of execution  $R_{\alpha}$  of the path  $\alpha$  is satisfied by the (initial) vector  $\overline{\nu}$  at the beginning of the path, then the path is executed and after execution, the final vector  $\overline{\nu}_f$  of variable values becomes  $s_{\alpha}(\overline{\nu}_f)$  and the output  $O_{\alpha}(\overline{\nu})$  is produced.

Let  $\tau_{\alpha}(\overline{v}, \overline{v}_f, O) : R_{\alpha}(\overline{v}) \wedge (\overline{v}_f = s_{\alpha}(\overline{v})) \wedge (O = O_{\alpha}(\overline{v}))$  be the characteristic formula of the path  $\alpha$  and  $\tau_{\beta}(\overline{v}, \overline{v}_f, O) : R_{\beta}(\overline{v}) \wedge (\overline{v}_f = s_{\beta}(\overline{v})) \wedge (O = O_{\beta}(\overline{v}))$  be the characteristic formula of the path  $\beta$ . The characteristic formula for the concatenated path  $\alpha\beta$  is  $\tau_{\alpha\beta}(\overline{v}, \overline{v}_f, O) = \exists \overline{v}_{\alpha} \exists O_1 \exists O_2(\tau_{\alpha}(\overline{v}, \overline{v}_{\alpha}, O_1) \wedge \tau_{\beta}(\overline{v}_{\alpha}, \overline{v}_f, O_2)) = R_{\alpha}(\overline{v}) \wedge R_{\beta}(s_{\alpha}(\overline{v})) \wedge (\overline{v}_f = s_{\beta}(s_{\alpha}(\overline{v}))) \wedge (O = O_{\alpha}(\overline{v})O_{\beta}(s_{\alpha}(\overline{v})))$ . O is the concatenated output list of  $O_{\alpha}(\overline{v})$  and  $O_{\beta}(s_{\alpha}(\overline{v}))$ .

## 2.2.4 Computations and Path Covers of an FSMD

A computation of an FSMD is a finite walk from the reset state  $q_0$  back to itself without having any intermediary occurrence of  $q_0$ . Such a computational semantics of an FSMD is based on the assumption that a revisit of the reset state means the beginning of a new computation and each computation terminates. In other words, the behavioural representation has a non-terminating outermost loop from the reset state and each inner loop has a state from which there is a transition out of the loop. A computation  $\mu$  of an FSMD M may be characterized as  $\tau_{\mu}(\overline{v}_i, \overline{v}_f, O) : R_{\mu}(\overline{v}_i) \wedge (\overline{v}_f = s_{\mu}(\overline{v}_i)) \wedge (O = O_{\mu}(\overline{v}_i))$ , where  $\overline{v}_i$  is the vector of initial input with which the computation is started,  $R_{\mu}$  is a satisfiable condition over the domain of I,  $s_{\mu}$  is a function over this domain to the codomain of values over V and  $O_{\mu}$  is the concatenation of the output lists resulting from output

operations along  $\mu$ .

**Definition 5** Two computations  $\mu_1$  and  $\mu_2$  having the characteristic formulae  $\tau_{\mu_1}$  and  $\tau_{\mu_2}$ , respectively, are said to be equivalent if  $R_{\mu_1} = R_{\mu_2}$  and  $r_{\mu_1} = r_{\mu_2}$ .

The computational equivalence of two computations  $\mu_1$  and  $\mu_2$  is denoted as  $\mu_1 \simeq \mu_2$ . The computational equivalence of two paths  $p_1$  and  $p_2$  can be defined in a similar manner and is denoted as  $p_1 \simeq p_2$ . Equivalence checking of paths, therefore, consists in establishing the computational equivalence of the respective conditions of execution and the respective data transformations.

Any computation  $\mu$  of an FSMD M can be looked upon as a computation along some concatenated path  $[\alpha_1\alpha_2\alpha_3...\alpha_k]$  of M such that the path  $\alpha_1$  emanates from and the path  $\alpha_k$  terminates in the reset state  $q_0$  of M, for  $1 \le i \le k$ ,  $\alpha_i$  terminates in the initial state of the path  $\alpha_{i+1}$  and  $\alpha_i$ 's may not be all distinct. If  $\tau_{\alpha_i}(\overline{\nu}_i,\overline{\nu}_{i+1}), 1 \le i \le k$ , be the characteristic formula of the path  $\alpha_i$ , then the characteristic formula of the concatenated path  $[\alpha_1\alpha_2\alpha_3...\alpha_k]$  is the formula

$$R_{\alpha_{1}}(\overline{v}_{1}) \wedge R_{\alpha_{2}}(s_{\alpha_{1}}(\overline{v}_{1})) \wedge \cdots \wedge R_{\alpha_{k}}(s_{\alpha_{k-1}}(\cdots(s_{\alpha_{1}}(\overline{v}_{1}))\cdots)) \wedge [\overline{v}_{k+1} = s_{\alpha_{k}}(s_{\alpha_{k-1}}(\cdots(s_{\alpha_{1}}(\overline{v}_{1}))\cdots))]$$